附录B:Standard Delay Format(SDF)(上)

Posted KuoGavin

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了附录B:Standard Delay Format(SDF)(上)相关的知识,希望对你有一定的参考价值。

文章目录

本附录将介绍标准延迟标注格式,并说明了如何在仿真中执行反标。

延迟格式描述了设计网表的单元延迟和互连走线延迟,无论设计是用两种主要硬件描述语言( V H D L VHDL VHDL或 V e r i l o g H D L Verilog\\ HDL Verilog HDL)中的哪一种所描述的。

本章还会介绍仿真的反标(backannotation), S T A STA STA的反标其实是一个简单直接的过程,其中 D U A DUA DUA中的时序弧将由 S D F SDF SDF所指定的延迟进行标注。

B.1 什么是SDF(What is it)

S D F SDF SDF是指标准延迟格式(Standard Delay Format)。它是一个 I E E E IEEE IEEE标准—— I E E E S t d 1497 IEEE\\ Std\\ 1497 IEEE Std 1497,它是 A S C I I ASCII ASCII文本文件,它描述了时序信息和约束,其目的是用作各种工具之间的文本类型的时序信息交换媒介,它也可以用来描述需要它的工具的时序数据。由于它是 I E E E IEEE IEEE标准,因此由一个工具生成的时序信息可以被支持该标准的许多其它工具所使用。 S D F SDF SDF中的数据与工具和语言都无关,且包括了互连走线延迟、器件延迟以及时序检查的规范。

由于 S D F SDF SDF是 A S C I I ASCII ASCII文件,因此它易于阅读,尽管对于实际设计而言,这些文件往往很大。但是,它是作为工具之间的交换媒介。经常在进行信息交换时,一个工具可能会在生成 S D F SDF SDF文件时产生一个问题,而另一个读取 S D F SDF SDF的工具可能无法正确读取 S D F SDF SDF。读取 S D F SDF SDF的工具可能会在读取 S D F SDF SDF时产生一个错误或警告,或者它可能会错误地解释 S D F SDF SDF中的值。在这种情况下,设计人员可能必须查看 S D F SDF SDF文件,看看出了什么问题。本章介绍了 S D F SDF SDF文件的基础知识,并提供了必要和足够的信息,以帮助理解和调试任何标注问题。

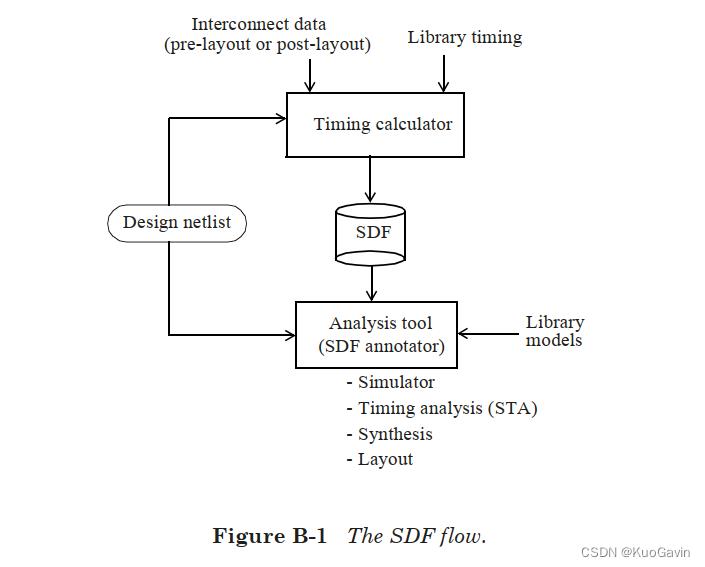

图B-1显示了如何使用 S D F SDF SDF文件的典型流程。时序计算工具通常会生成时序信息存储在 S D F SDF SDF文件中。然后,通过读取 S D F SDF SDF的工具将该信息反标到设计中。请注意,完整的设计信息不会都存储到 S D F SDF SDF文件中,而只会存储延迟值。例如,实例名称和实例的引脚名称将被存储到 S D F SDF SDF文件中,因为它们对于指定实例相关或引脚相关的延迟是必需的。因此,必须为 S D F SDF SDF生成工具和 S D F SDF SDF读取工具提供相同的设计。

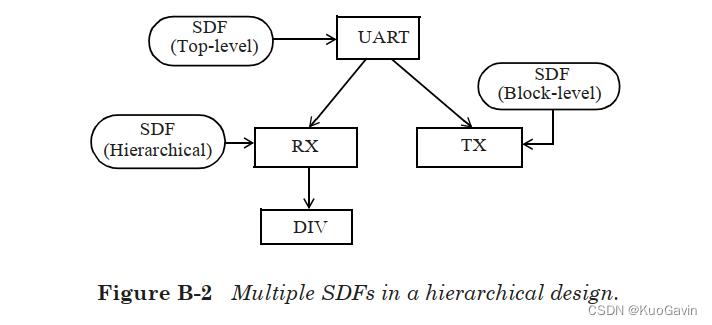

一个设计可以具有多个与之关联的 S D F SDF SDF文件。可以为一个设计创建一个 S D F SDF SDF文件,在分层设计中,也可以为分层中的每个块创建多个 S D F SDF SDF文件。在标注期间,每个 S D F SDF SDF都将应用于适当的分层实例中,如图B-2所示。

S D F SDF SDF文件包含了用于反标和标注的时序数据。更具体地说,它包含:

- 单元延迟(Cell delays);

- 脉冲传播(Pulse propagation);

- 时序检查(Timing checks);

- 互连走线延迟(Interconnect delays);

- 时序环境(Timing environment);

引脚到引脚的延迟(pin-to-pin delay)和分布式延迟(distributed delay)都可以针对单元延迟进行建模。引脚到引脚的延迟使用 I O P A T H IOPATH IOPATH结构(construct)表示,这些结构定义了每个单元输入到输出的路径延迟。 C O N D COND COND结构还可以用于额外指定有条件的引脚到引脚延迟。状态相关(state-dependent)的路径延迟也可以使用 C O N D COND COND结构来指定,分布式延迟的建模是使用 D E V I C E DEVICE DEVICE结构指定的。

脉冲传播结构—— P A T H P U L S E PATHPULSE PATHPULSE和 P A T H P U L S E P E R C E N T PATHPULSEPERCENT PATHPULSEPERCENT可用于指定使用引脚到引脚延迟模型时允许传播到单元输出端口的毛刺大小。

可以在SDF中指定的时序检查包括:

- 建立时间:

SETUP,SETUPHOLD; - 保持时间:

HOLD,SETUPHOLD; - 恢复时间:

RECOVERY,RECREM; - 撤销时间:

REMOVAL,RECREM; - 最大偏斜:

SKEW,BIDIRECTSKEW; - 最小脉冲宽度:

WIDTH; - 最小周期:

PERIOD; - 不变化:

NOCHANGE;

时序检查中的信号可能存在某些条件。在时序检查中允许使用负值,不支持负值的工具可以选择将其替换为零。

S D F SDF SDF描述中支持三种类型的互连走线建模。 I N T E R C O N N E C T INTERCONNECT INTERCONNECT结构是最通用且最常用的,可用于指定点对点延迟(从源端到接收端),因此单个网络可以具有多个 I N T E R C O N N E C T INTERCONNECT INTERCONNECT结构。 P O R T PORT PORT结构可用于指定负载端口处的网络延迟,假定网络只有一个源端驱动。 N E T D E L A Y NETDELAY NETDELAY结构可用于指定整个网络的延迟,而无需考虑其源端或接收端,因此是指定网络上延迟的最不具体的方法。

时序环境提供了设计在工作时所依据的信息,这些信息包括 A R R I V A L ARRIVAL ARRIVAL, D E P A R T U R E DEPARTURE DEPARTURE, S L A C K SLACK SLACK和 W A V E F O R M WAVEFORM WAVEFORM结构。这些结构主要用于标注,例如可用于综合。

B.2 SDF格式(The Format)

S D F SDF SDF文件包含一个首部(header section),后跟一个或多个单元。每个单元代表设计中的一个区域或范围,它可以是库原语(primitive)或用户自定义的黑盒。

(DELAYFILE

<header_section>

(CELL

<cell_section>

)

(CELL

<cell_section>

)

... <other cells>

)

首部包含一般信息,除了层次结构分隔符、时间刻度(timescale)和

S

D

F

SDF

SDF版本号外,都不会影响

S

D

F

SDF

SDF文件的语义。默认情况下,层次结构分隔符DIVIDER是点字符(.)。通过以下方法,可以将其替换为/字符:

(DIVIDER /)

如果首部中没有时间刻度信息,则默认值为

1

n

s

1ns

1ns。否则,可以使用以下命令明确指定时间刻度TIMESCALE:

(TIMESCALE 10ps)

也就是说,将 S D F SDF SDF文件中指定的所有延迟值乘以 10 p s 10ps 10ps。

S

D

F

SDF

SDF版本号SDFVERSION是必需的,

S

D

F

SDF

SDF文件的使用者会根据它来确保文件符合指定的

S

D

F

SDF

SDF版本。首部中可能存在的其它信息(属于常规信息类别)包括日期、程序名称、版本和工作条件。

(DESIGN "BCM")

(DATE "Tuesday, May 24, 2004")

(PROGRAM "Star Galaxy Automation Inc., TimingTool")

(VERSION "V2004.1")

(VOLTAGE 1.65:1.65:1.65)

(PROCESS "1.000:1.000:1.000")

(TEMPERATURE 0.00:0.00:0.00)

首部之后是一个或多个单元的描述,每个单元在设计中代表一个或多个实例(使用通配符),单元可以是库原语或分层块(hierarchical block)。

(CELL

(CELLTYPE <cell_type>)

(INSTANCE <hierarchical_instance_name>)

(DELAY

<path_delay_section>

)

(TIMINGCHECK

<timing_check_section>

)

(TIMINGENV

<timing_environment_section>

)

(LABEL

<label_section>

)

)

. . . <other cells>

单元的顺序很重要,因为数据是从上到下进行处理的。后面的单元描述可以覆盖前面的单元描述所指定的时序信息(通常,两次定义同一单元实例的时序信息并不常见)。另外,可以将时序信息标注为绝对值或增量的形式。如果时序信息使用增量的形式,它将会把新值添加到现有值中。而如果时序信息是绝对值,它将覆盖任何先前指定的时序信息。

单元实例可以是分层实例名称。用于层次结构分隔的分隔符必须符合首部中指定的分隔符。单元实例名称可以选择为*字符,即通配符,这表示指定类型的所有单元实例。

(CELL

(CELLTYPE "NAND2")

(INSTANCE *)

// Refers to all instances of NAND2.

. . .

一个单元可以用指定四类时序规格来进行描述:

DELAY:用来描述时延;TIMINGCHECK:用来描述时序检查;TIMINGENV:用来描述时序环境;LABEL:声明用以描述时延的时序模型变量;

以下是相关例子:

// An absolute path delay specification:

(DELAY

(ABSOLUTE

(IOPATH A Y (0.147))

)

)

// A setup and hold timing check specification:

(TIMINGCHECK

(SETUPHOLD (posedge Q) (negedge CK) (0.448) (0.412))

)

// A timing constraint between two points:

(TIMINGENV

(PATHCONSTRAINT UART/ENA UART/TX/CTRL (2.1) (1.5))

)

// A label that overrides the value of a Verilog HDL

// specparam:

(LABEL

(ABSOLUTE

(t$CLK$Q (0.480:0.512:0.578) (0.356:0.399:0.401))

(tsetup$D$CLK (0.112))

)

)

DELAY时序规范有四种类型:

ABSOLUTE:在反标期间替换单元实例的现有延迟值;INCREMENT:将新的延迟数据添加到单元实例的任何现有延迟值;PATHPULSE:指定设计输入和输出之间的脉冲传播极限。此极限值用于决定是将出现在输入上的脉冲传播到输出,还是将其标记为X,或者将其滤除;PATHPULSEPERCENT:除了值以百分比表示外,这与PATHPULSE完全相同;

以下是一些例子:

// Absolute port delay:

(DELAY

(ABSOLUTE

(PORT UART.DIN (0.170))

(PORT UART.RX.XMIT (0.645))

)

)

// Adds IO path delay to existing delays of cell:

(DELAY

(INCREMENT

(IOPATH (negedge SE) Q (1.1:1.22:1.35))

)

)

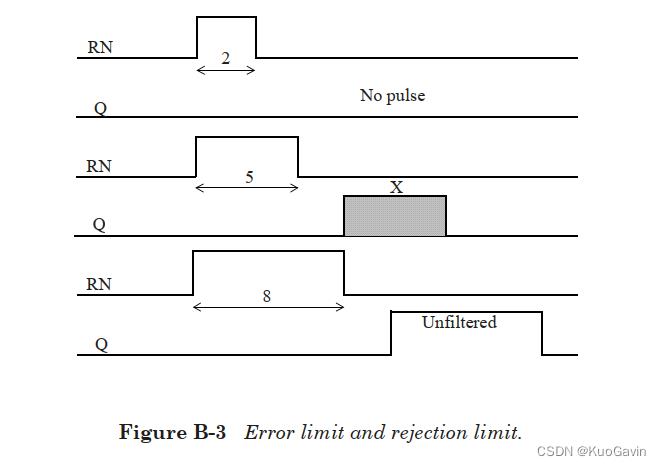

// Pathpulse delay:

(DELAY

(PATHPULSE RN Q (3) (7))

)

// The ports RN and Q are input and output of the

// cell. The first value, 3, is the pulse rejection

// limit, called r-limit; it defines the narrowest pulse

// that can appear on output. Any pulse narrower than

// this is rejected, that is, it will not appear on

// output. The second value, 7, if present, is the

// error limit - also called e-limit. Any pulse smaller

// than e-limit causes the output to be an X.

// The e-limit must be greater than r-limit. See

// Figure B-3. When a pulse that is less than 3 (r-limit)

// occurs, the pulse does not propagate to the output.

// When the pulse width is between the 3 (r-limit) and

// 7 (e-limit), the output is an X. When the pulse width

// is larger than 7 (e-limit), pulse propagates to output

// without any filtering.

// Pathpulsepercent delay type:

(DELAY

(PATHPULSEPERCENT CIN SUM (30) (50))

)

// The r-limit is specified as 30% of the delay time from

// CIN to SUM and the e-limit is specified as 50% of

// this delay.

可以使用ABSOLUTE或INCREMENT描述八种延迟定义:

IOPATH:输入到输出路径的延迟;RETAIN:保留时间定义,可以用于指定输出端口在其相关输入端口改变后应保留其先前值的时间;COND:条件路径延迟,可以用于指定状态相关的输入到输出路径延迟;CONDELSE:默认路径延迟,可以用于指定条件路径的默认值;PORT:端口延迟,可以用于指定互连走线延迟,该延迟被建模为输入端口的延迟;INTERCONNECT:互连走线延迟,可以用于指定从其源端到接收端的整个网络的传播延迟;NETDELAY:网络延迟,可以用于指定从一个网络的所有源端到所有接收端的传播延迟;DEVICE:器件延迟,主要用于描述分布式时序模型,可以用于指定通过单元到输出端口的所有路径的传播延迟;

以下是一些例子:

// IO path delay between posedge of CK and Q:

(DELAY

(ABSOLUTE

(IOPATH (posedge CK) Q (2) (3))

)

)

// 2 is the propagation rise delay and 3 is the

// propagation fall delay.

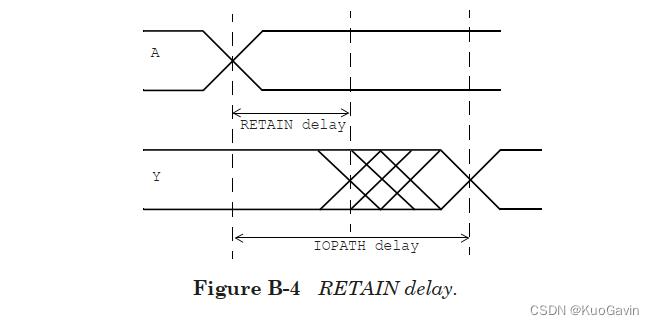

// Retain delay in an IO path:

(DELAY

(ABSOLUTE

(IOPATH A Y

(RETAIN (0.05:0.05:0.05) (0.04:0.04:0.04))

(0.101:0.101:0.101) (0.09:0.09:0.09))

)

)

// Y shall retain its previous value for 50ps (40ps for

// a low value) after a change of value on input A.

// 50ps is the retain high value, 40ps is the retain

// low value, 101ps is the propagate rise delay and

// 90ps is the propagate fall delay. See Figure B-4.

// Conditional path delay:

(DELAY

(ABSOLUTE

(COND SE == 1'b1 (IOPATH (posedge CK) Q (0.661)))

)

)

// Default conditional path delay:

(DELAY

(ABSOLUTE

(CONDELSE (IOPATH ADDR[7] COUNT[0] (0.870) (0.766)))

)

)

// Port delay on input FRM_CNT[0]:

(DELAY

(ABSOLUTE

(PORT UART/RX/FRM_CNT[0] (0.439))

)

)

// Interconnect delay:

(DELAY

(ABSOLUTE

(INTERCONNECT O1/Y O2/B (0.209:0.209:0.209))

)

)

// Net delay:

(DELAY

(ABSOLUTE

(NETDELAY A3/B (0.566))

)

)

延迟(Delay)

到目前为止,我们已经看过了许多不同形式的延迟,

以上是关于附录B:Standard Delay Format(SDF)(上)的主要内容,如果未能解决你的问题,请参考以下文章