I2C 时序

Posted god-of-death

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了I2C 时序相关的知识,希望对你有一定的参考价值。

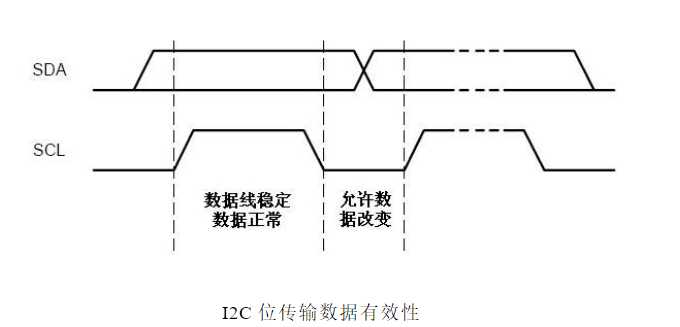

数据的有效性

SDA 线上的数据必须在时钟的高电平周期保持稳定。数据线的高或低电平状态只 有在SCL 线的时钟信号是低电平时才能改变 。

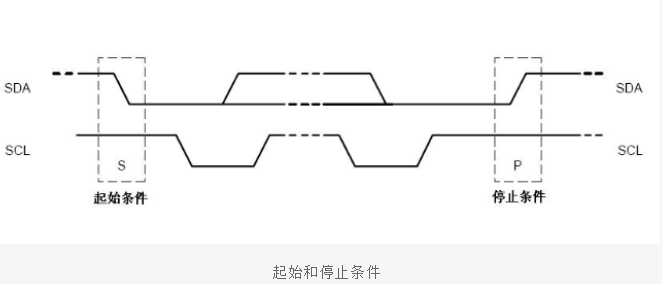

起始和停止条件

SCL 线是高电平时,SDA 线从高电平向低电平切换,这个情况表示起始条件;

SCL 线是高电平时,SDA 线由低电平向高电平切换,这个情况表示停止条件

起始和停止条件一般由主机产生,总线在起始条件后被认为处于忙的状态

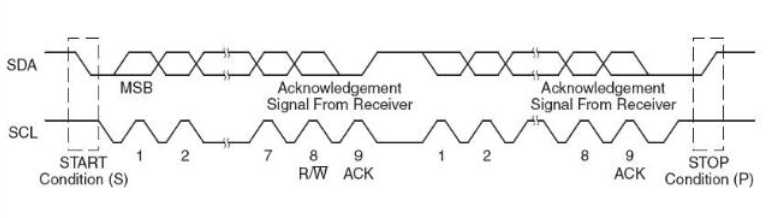

I2C总线数据传输

发送到SDA 线上的每个字节必须为8位,每次传输可以发送的字节数量不受限制。每个字节后必须跟一个响应位。首先传输的是数据的最高位(MSB),如果从机要完成一些其他功能后(例如一个内部中断服务程序)才能接收或发送下一个完整的数据字节,可以使时钟线SCL 保持低电平,迫使主机进入等待状态,当从机准备好接收下一个数据字节并释放时钟线SCL 后数据传输继续。

以上是关于I2C 时序的主要内容,如果未能解决你的问题,请参考以下文章