nor flash之写保护

Posted zqb-all

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了nor flash之写保护相关的知识,希望对你有一定的参考价值。

背景

没有电池的嵌入式设备,很容易发生随机掉电。因此要让产品可靠稳定,就必须保证各种场景下的掉电安全。

例如系统更新过程随机掉电,不能导致系统无法启动。例如正常读写flash过程中掉电,最多正在传输的数据丢掉,但不能导致flash其他数据出错,否则轻则丢数据,重则直接变砖无法启动。本文主要分析flash数据出错的情况。

问题:flash掉电数据出错

为什么掉电会导致flash数据出错呢?因为在产品掉电时,对用户来说拔下插头是一瞬间,但对于板子上的各个器件来说,却是存在一个掉电过程,即电压从正常值掉到0的过程,这个不是瞬间的。而掉电时机是随机的无法预测的,也就是开始掉电的时候,主控可能正在读flash,写flash,擦除flash,SPI总线上还有很多波形在欢快地传输着。而各个器件也各自有一个工作电压的范围,因此当电压开始掉落时,各个器件还会继续做自己的事情,直到电压掉到实际工作电压之下,才停止工作。

flash的规格书上会标注工作电压,例如标称3.6V-2.7V,那么在电压从正常的3.3V一路掉到2.7V的过程中,我们可以知道flash都还能正常工作,可以正常接收命令进行读写擦等,但从2.7V再往下掉就开始超出flash正常的工作电压,flash就不保证继续正常工作了。那是不是到了2.7V flash就不工作了呢,抱歉,也不是,flash要到某个更低的电压才会彻底歇菜停止运转,我们假设为2.3V吧。

那么问题来了,电压跌落到2.7V-2.3V之间呢,这个时候flash是怎么样的? 答案是flash是处于不稳定态,可能还在工作,但不保证正常工作。

不保证正常工作的意思是,我也许还能工作,但不保证工作的结果是对的。例如此时收到一条擦除A地址的数据的命令,实际可能把表示A地址的波形解析成B地址,然后就把B地址的数据擦了。或者收到写A地址的命令,却写到了B地址。

解决方式

硬件解法

既然知道flash在掉电时,会存在一段电压区间,工作不稳定。那么硬件解法就是设法避免这种场景。

例如加快掉电速度,那这段危险区间的时间就变短了,出错的概率就降低了。如果能很快把flash的电掉下来,则flash就没有时间可以出错了。

例如设法在电压掉到2.7V之前,先把主控的电断了或者把SPI的通信阻断掉,这样flash就不会收到波形,也就不会解析错了。

硬件上的解决方式,规避方式,降低概率方式应该还是蛮多的,但硬件解法有个问题,就是需要增加成本,这个对于有些追求可靠性的产品来说,可靠稳定最重要,增加点成本问题不大。但对于有些价格敏感竞争激烈的产品来说,就是大问题了。

软件解法

软件上其实没有特别好的解决方式,只能通过降低flash的擦写频率,启用写保护等手段,最终达到把概率降到足够低的目的。

降低flash擦写频率,这个很好理解,写得越多,在掉电时撞上正在操作flash的概率就越大,那么出错的概率就越大。但是否写flash,写多少这个是跟应用相关的。下主面要介绍下nor flash写保护,这个是可以在驱动层面做的。

nor写保护

写保护是nor提供的功能,即可以通过配置一些寄存器,将某些区域保护起来。如果没有解除保护,那对这个区域的写入和擦除,都会被直接忽略掉。

例如在不稳定状态下,写A的命令被理解为写B了,此时如果B是处于写保护区域,那这个命令会被忽略掉,不会造成实质性的破坏性的影响。

BP保护

大多数nor flash支持使用BP位来配置写保护,这种保护的特点是其保护的数据是成片的,一般是从flash头部开始的一片数据,或者从flash尾部开始的一片数据。

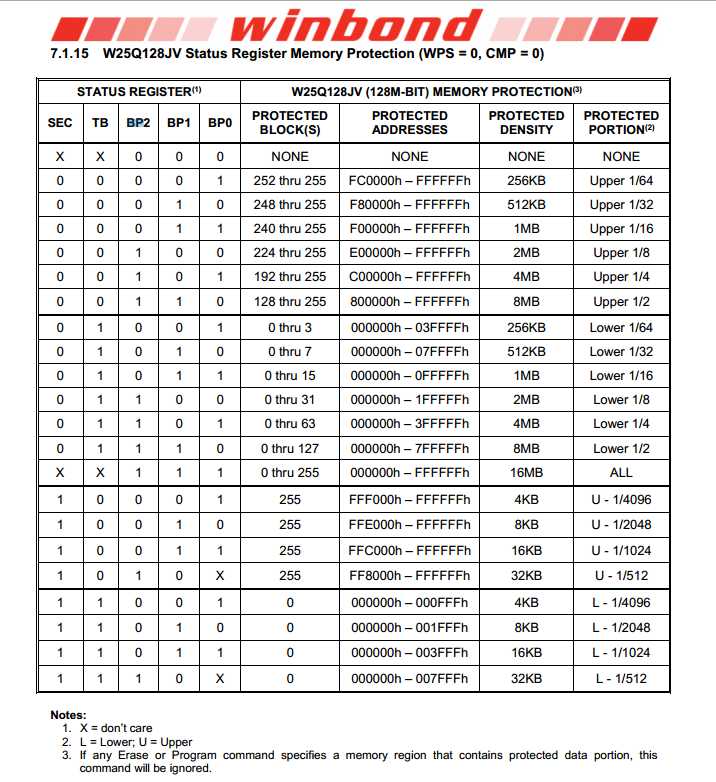

例如 winbond的这款flash就标注了

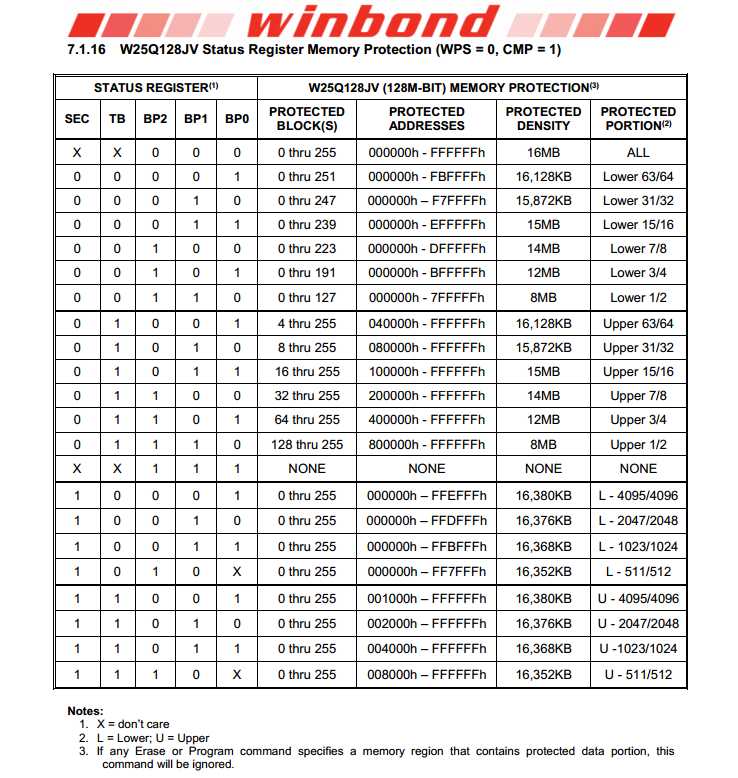

从规格书可很容易看出,保护的范围是BP bit再结合其他的一些bit 一起决定的,可以保护1/2, 3/4, 7/8 等多种范围。

这些bit的位置,设置方式,规格书中都有描述,按照规定在驱动中操作对应的寄存器即可。

不同厂家的保护bit设置都不太一样,涉及到BP bit,SEC bit, CMP bit等,每适配一款新的nor,都得重新查下规格书才行。

特别要注意的是,区分好具体的设置是持久化的还是掉电丢失的,具体的bit是否有OTP的特性,即one time program,只能写入一次,无法逆转。

独立块保护

除了普遍支持的BP写保护,也就是分片保护之外,有些flash还提供了更细粒度的写保护,即独立块保护(individual block protect)。

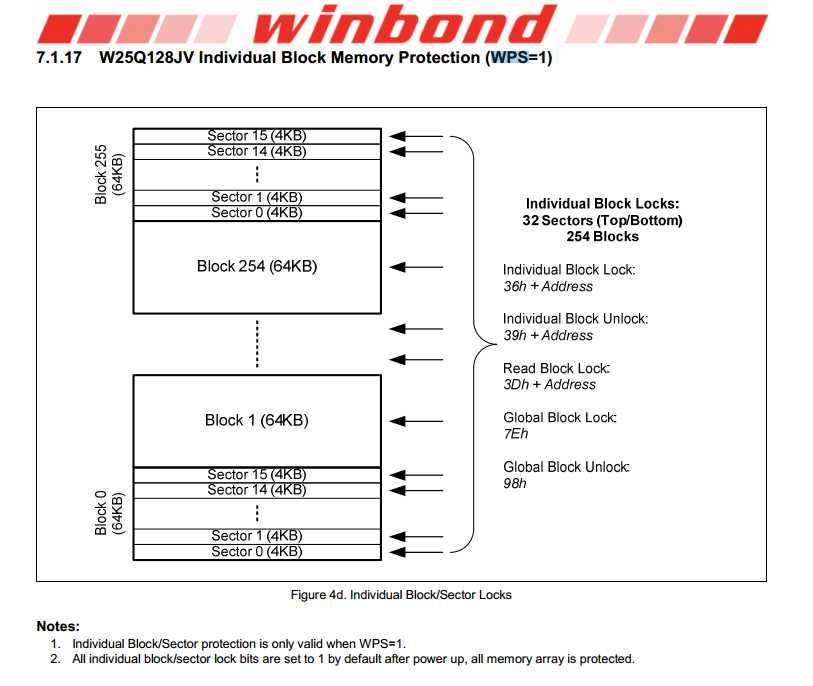

还是以winbond为例,当WPS(write protect selection) bit被设置,则写保护切换到独立块保护。

在这种模式下,BP的设置就无效了,每次上电默认处于完全写保护的状态。

主控可以针对每个block(64KB)进行独立的解锁和上锁。对于首尾两个block,还可以细致到sector(4KB)进行保护。

两种写保护的比较

相对而言,独立块保护的出错概率肯定是比BP保护的概率低的,因为写入A或擦除A时,必须先对A进行解保护。

对于BP保护来说,为了解开A的写保护,必须解开一片区域。假如A处于flash的中间位置,那么解保护的范围会接近1/2 flash的范围。此时发生解析错误,把A解析成B,那么B落在这片未保护的区域的概率还是比较高的。

对于独立块保护来说,为了解开A的写保护,需要解开的区域仅为1个block甚至1个sector,那么出错后的B刚好落在这个范围的概率自然就大大降低了。

当然,具有独立块保护功能的flash,其成本肯定要高些,售价一般也会高一些吧。

小结

flash掉电会有误擦误写的风险,写保护只是降低误擦误写的概率,并不能完全解决。只要有写入和擦除,就可能会撞上掉电。

硬件解决增加成本,软件使用写保护则只能降低概率。部分flash支持独立块保护机制,理论上出错概率会远小于BP保护机制。

本文地址:https://www.cnblogs.com/zqb-all/p/12182920.html

以上是关于nor flash之写保护的主要内容,如果未能解决你的问题,请参考以下文章