在verilog里, 上升沿和下降沿的问题. 求大神帮助, 小的新人一枚. 谢谢先

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了在verilog里, 上升沿和下降沿的问题. 求大神帮助, 小的新人一枚. 谢谢先相关的知识,希望对你有一定的参考价值。

我的时间j变化时, a和r也应该跟着变化, 但当j 在第二次变化的时候, a和r 没有跟着变, 我的代码和testbench如下,并附有我的真图.

module try ( clk, rst, v, j, a, r, b);

input wire clk;

input wire rst;

input wire [9:0] v;

input wire [3:0] j;

output reg [1:0] r;

reg [9:0] v_call;

output reg [9:0] a;

output reg [9:0] b;

always @ (*)

if (j == 0) begin

v_call = v;

b = v_call;

end

always @ (posedge j or negedge j) begin

r[1] = v_call[9];

r[0] = v_call[8];

v_call = v_call << 2;

a = v_call;

end

endmodule

testbench如下:

`timescale 1ns/100ps

module testbench1 ();

reg clk;

reg rst;

//wire pbit;

reg [9:0] v;

reg [3:0] j;

wire [1:0] r;

wire [9:0] a;

wire [9:0] b;

//wire [3:0] c;

//wire [2:0] d;

try DUT (

.clk(clk),

.rst(rst),

//.pbit(pbit),

.v(v),

.j(j),

.r(r),

.a(a),

.b(b)

//.c(c),

//.d(d)

);

initial begin

v = 10'b1110001011;

clk = 0;

rst = 0;

j = 4'd0;

#5

rst = 1;

#5

clk <= 1; // S = 01

#10

clk <= 0;// S = 10

#10

clk <= 1; // S = 11

#10

clk <= 0;// S = 00

j = 4'd1;

#10

clk <= 1; //01

#10

clk <= 0; //10

#10

clk <= 1; //11

#10

clk <= 0;// S = 00

j = 4'd2;

#10

clk <= 1; //01

#10

clk <= 0; //10

#10

clk <= 1; //11

#10

clk <= 0;// S = 00

j = 4'd3;

#10

clk <= 1; //01

#10

clk <= 0; //10

#10

clk <= 1; //11

end

endmodule

我自学的... 我想我懂了,谢谢

参考技术A j是四个字节的你怎么搞成上升和下降沿的追问因为我也才学verilog, 所以可以给我讲详细点吗? 四个字节的就不能上升和下降沿了吗? 那我应该怎么改呢? 谢谢你回我

追答你想实现个什么东西?说一下可以帮你知道下

Verilog实现上升下降沿检测 FPGA

Verilog实现上升、下降沿检测

源文件

`timescale 1ns / 1ps

module top(

input clk, //时钟信号

input rst_n, //复位信号,低电平有效

input signal //待检测信号

);

wire posedge_get; //检测到上升沿标志

wire negedge_get; //检测到下降沿标志

reg signal_buff_1; //输入数据缓冲1

reg signal_buff_2; //输入数据缓冲2

//对输入数据进行两次缓存(打两拍)

always @(posedge clk or negedge rst_n) begin

if (rst_n == 0) begin

signal_buff_1 <= 0;

signal_buff_2 <= 0;

end

else begin

signal_buff_1 <= signal;

signal_buff_2 <= signal_buff_1;

end

end

//前一个时钟为低电平,下一个时钟为高电平,说明上升沿到来。

assign posedge_get = (signal_buff_2 == 0)&&(signal_buff_1 == 1);

//前一个时钟为高电平,下一个时钟为低电平,说明下降沿到来。

assign negedge_get = (signal_buff_2 == 1)&&(signal_buff_1 == 0);

endmodule

激励文件

`timescale 1ns / 1ps

module tb_top;

// 时钟参数

parameter PERIOD = 10;

// 输入参数

reg clk = 0 ;

reg rst_n = 0 ;

reg signal = 0 ;

initial begin

forever

#(PERIOD/2) clk=~clk; //系统时钟

end

initial begin

#(PERIOD*2) rst_n = 1; //复位信号

end

//例化边沿检测模块

top u_top (

.clk ( clk ),

.rst_n ( rst_n ),

.signal ( signal )

);

initial begin

#(PERIOD*2.5) signal=1; //信号拉高,上升沿到来

#(PERIOD*4) signal=0; //信号拉低,下降沿到来

end

endmodule

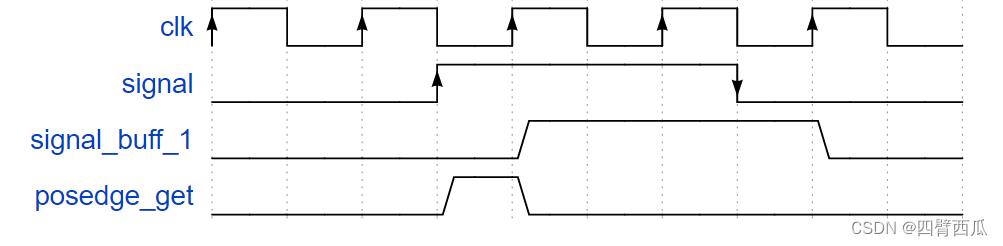

仿真波形

释义

代码的含义,已经通过注释讲明,如有不清楚存在疑问的,可以评论留言。

这里解释下,为什么要拍2拍,为什么不只是拍1拍,也就是为什么存在两个signal_buff。

试想一下,当上升沿到来的时候,signal_buff_1为低电平,signal为高电平,可以直接判断出上升沿的到来,没有必要再设置signal_buff_2。可是如果这样判断上升沿,因为signal是不受时间控制的,posedge_get会在时钟高电平或者低电平期间变化。

假如要是signal有噪声,那么posedge_get也将会有噪声。

虽然大部分时候,后续的操作会避免这个异步因素,但是这个异步代码终究是个隐患。

这位前辈就是采用打一拍的方式检测上升下降沿。【数字IC手撕代码】Verilog边沿检测电路(上升沿,下降沿,双边沿)|题目|原理|设计|仿真_myhhhhhhhh的博客-CSDN博客_verilog上升沿检测

以上是关于在verilog里, 上升沿和下降沿的问题. 求大神帮助, 小的新人一枚. 谢谢先的主要内容,如果未能解决你的问题,请参考以下文章