Quartus II 6.0的报错!

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Quartus II 6.0的报错!相关的知识,希望对你有一定的参考价值。

Error (10500): VHDL syntax error at ctrl.vhd(312) near text "BEGIN"; expecting "(", or "'", or "." 你知道 这个报错什么意思吗?? 非常感谢

--BEGIN前一句要分号结束LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

use IEEE.STD_LOGIC_ARITH.ALL;

ENTITY Test IS

PORT

(

PORT1: OUT STD_LOGIC_VECTOR(15 DOWNTO 0);

PORT2: OUT STD_LOGIC_VECTOR(15 DOWNTO 0)

);

END Test;

ARCHITECTURE Test_arch OF Test IS

SIGNAL Period1uS, Period1mS, Period1S: STD_LOGIC;

SIGNAL spdata: STD_LOGIC_VECTOR(10 DOWNTO 0);

SIGNAL PS2: STD_LOGIC;

BEGIN

--BEGIN后面不要分号(;)

PROCESS( LED, Refresh )

BEGIN

--你的PROCESS

END PROCESS;

PORT1 <= "ZZZZZZZZZZZZZZZZ";

PORT2 <= "ZZZZZZZZZZZZZZZZ";

END Test_arch; 参考技术A 上一句没有加分号吧,或者括号之类的 ,检查一下吧 参考技术B 对,begin后面别画蛇添足。

Quartus系列:Quartus II 原理图输入设计

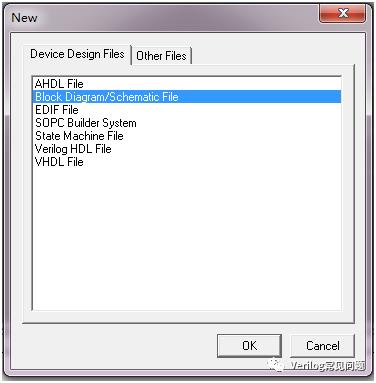

1.新建一个项目,点击"File->New..."弹出如下对话框:

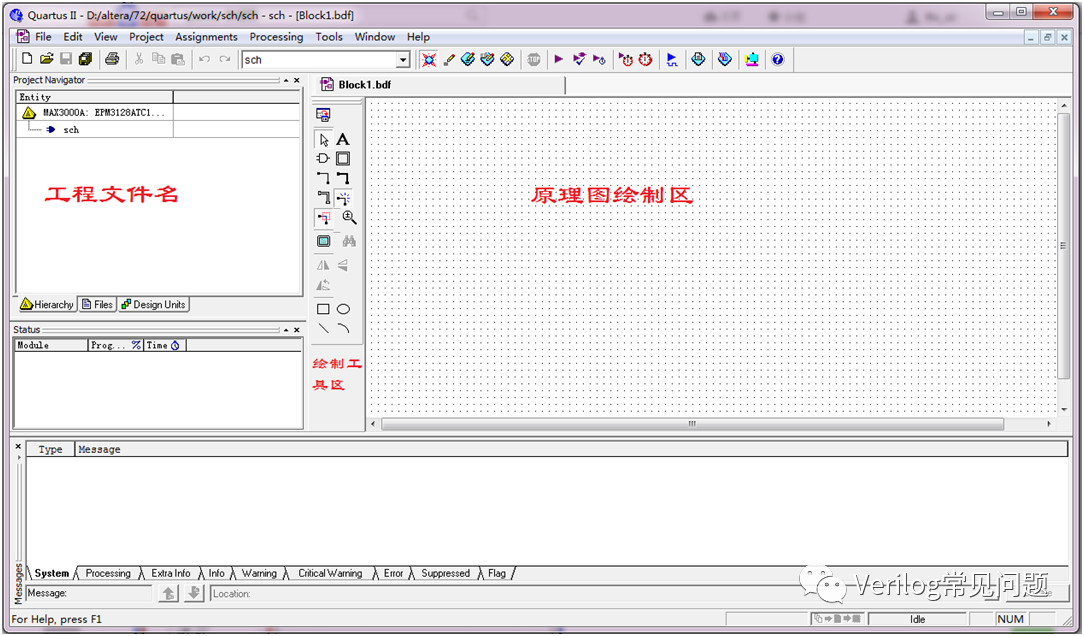

2.建立原理图设计平台:

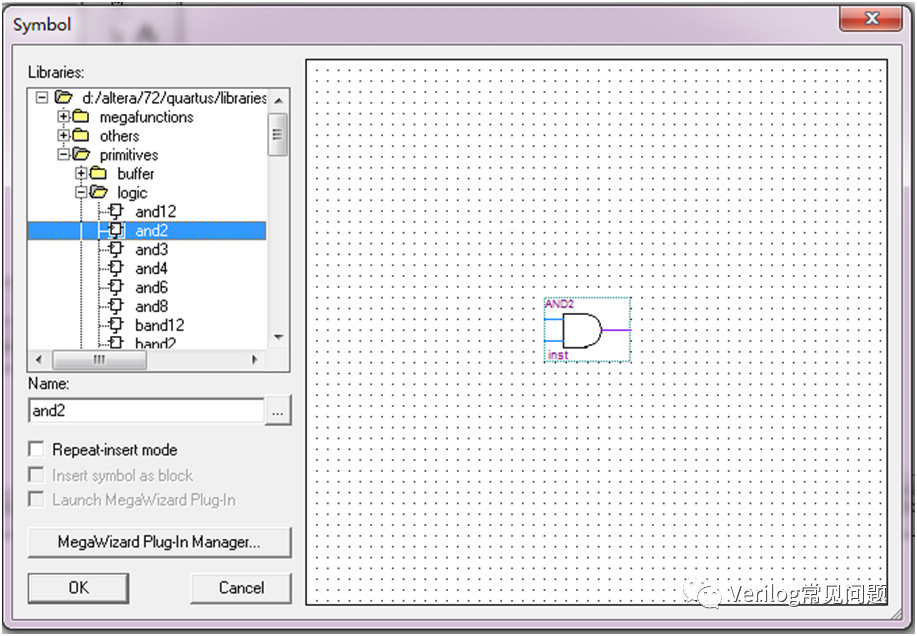

3.在原理图绘制区双击鼠标左键,即可弹出元件符号窗口,如下图所示:

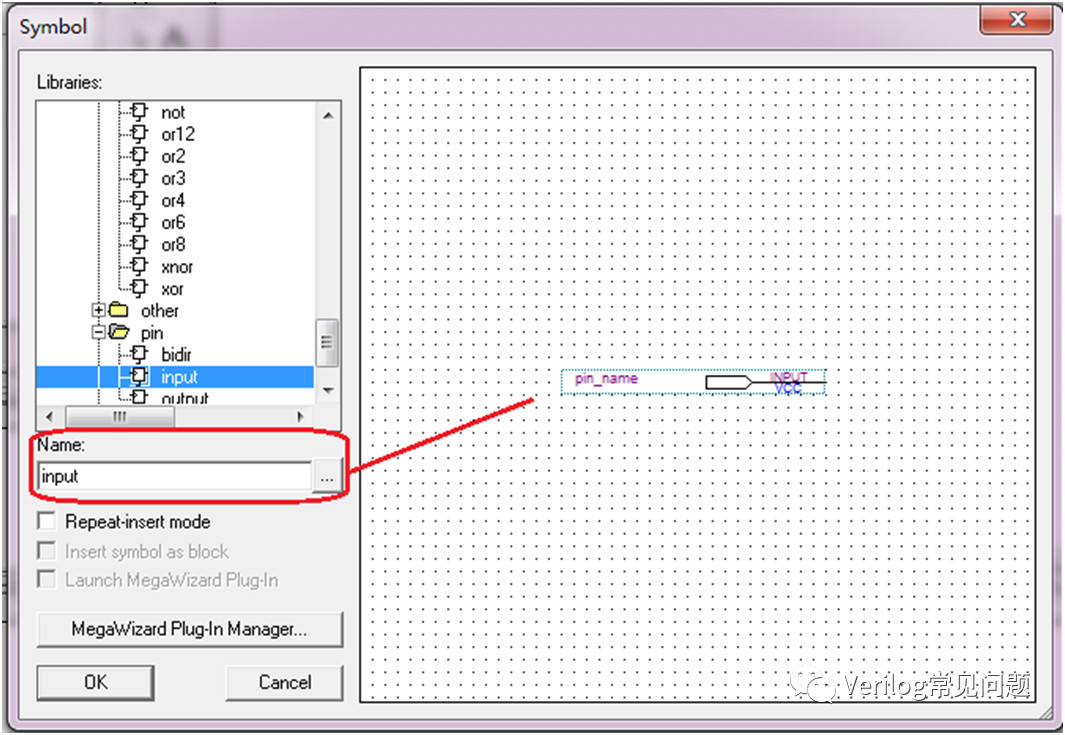

4.添加元件,在红色框部分输入要查找的元件名,如果库中存在对应元件,则对应元件符号会显示在对话框右侧的绘制区,单击"OK"即可完成对应元件加入到原理图绘制窗口中:

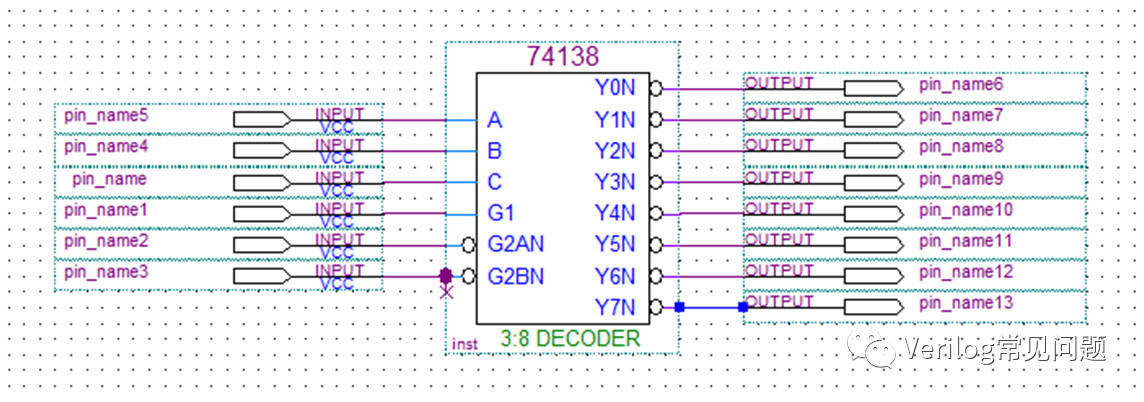

5.绘制连接原理图,当鼠标放到元件端点处时,鼠标会自动捕捉对应的连接处,按下左键拖动至目标出,再次松开鼠标即可完成一次连线操作如下图所示:

6. 完成连线后也可对相应的端口名进行命名,鼠标左键双击端口名,如图示74138电路A端连接的input端口命名为A,如下图所示:

完成管脚命名后保存设计,即完成原理图的设计.

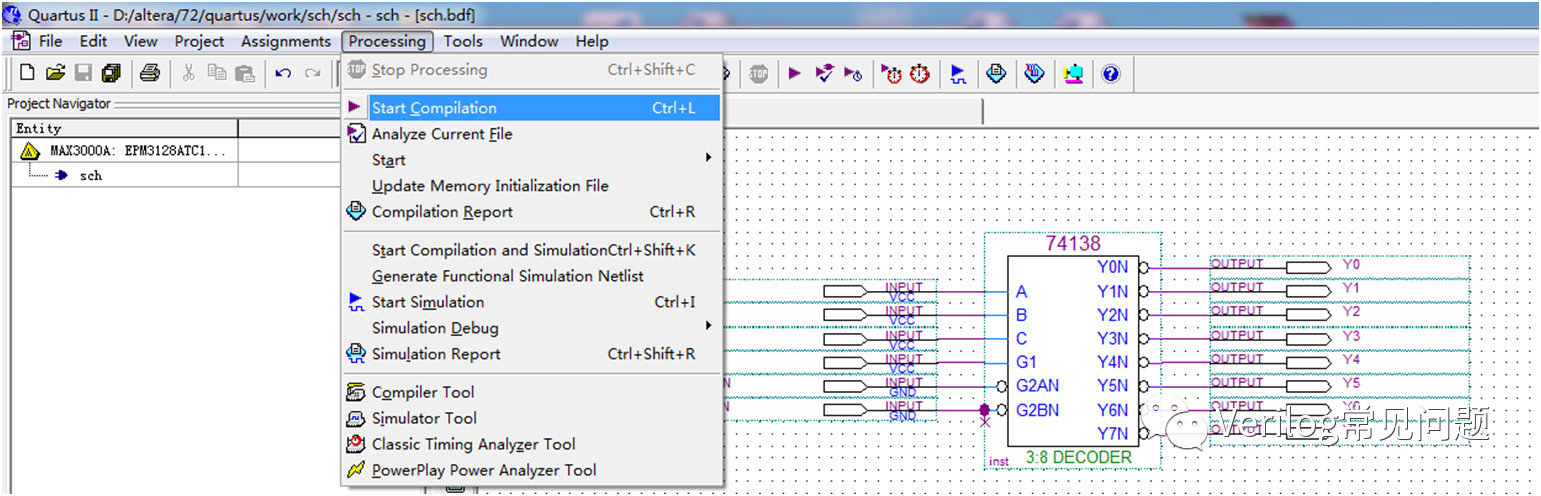

7.在下拉菜单Processing中选择Start Compilation,启动编译:

8.工程编译完成后,设计结果是否满足设计要求,可以通过时序仿真来分析;建立波形矢量文件(具体仿真矢量如何建立可参考"Quartus II 功能仿真设置流程").

更多资讯可扫描下方二维码!

以上是关于Quartus II 6.0的报错!的主要内容,如果未能解决你的问题,请参考以下文章