systemC全加器建模

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了systemC全加器建模相关的知识,希望对你有一定的参考价值。

博主今天刚看完systemC的时序建模和组合建模部分,就开始写sc代码了,但遇到了很多错误。。。

base.h头文件:

#ifndef _base_ #define _base_ #include "systemc.h" #include <iostream> #endif

关于全加器的定义 full_adder.h :

#include "base.h"

#ifndef _full_adder_

#define _full_adder_

SC_MODULE(Full_Adder)

{

sc_in<bool> a , b , carry_in ;

sc_out<bool> sum , carry_out ;

void Full_Adder_Proc();

SC_CTOR(Full_Adder){

SC_METHOD(Full_Adder_Proc);

sensitive<<a<<b<<carry_in ;

}

};

#endif关于全加器的函数 full_adder.cpp :

#include "full_adder.h"

void Full_Adder::Full_Adder_Proc(){

sum = a^b^carry_in ;

carry_out = a&carry_in | b&carry_in | a&b ;

}关于信号驱动的头文件 driver.h:

#include "base.h"

#ifndef _driver_

#define _driver_

SC_MODULE(driver)

{

sc_out<bool > d_a , d_b , d_cin;

void driver_proc();

SC_CTOR(driver){

SC_METHOD(driver_proc);

}

};

#endif关于信号驱动的实现代码driver.cpp:

#include "driver.h"

void driver::driver_proc(){

sc_uint<3> temp;

temp = 0 ;

while(1){

d_a = temp[0];

d_b = temp[1];

d_cin = temp[2];

wait(5,SC_NS);

temp++;

};

}关于monitor的头文件:

#include "base.h"

#ifndef _monitor_

#define _monitor_

SC_MODULE(Monitor){

sc_in<bool> a , b , carry_in , sum , carry_out ;

void Monitor_Proc();

SC_CTOR(Monitor){

SC_METHOD(Monitor_Proc);

sensitive<<a<<b<<carry_in<<sum<<carry_out ;

}

};

#endif关于monitor的实现:

#include "monitor.h"

void Monitor::Monitor_Proc(){

std::cout<<" a:"<<a<<" b:"<<b<<" cin:"<<carry_in;

std::cout<<"sum:"<<sum<<" cout:"<<carry_out<<std::endl;

}期间博主犯了两个很傻的错误:

(1) 其中一个文件把#ifndef 写成了 #ifdef

(2) 构造函数SC_CTOR写成了SC_STOR

导致一直编译不能通过。。。。。。。。。。

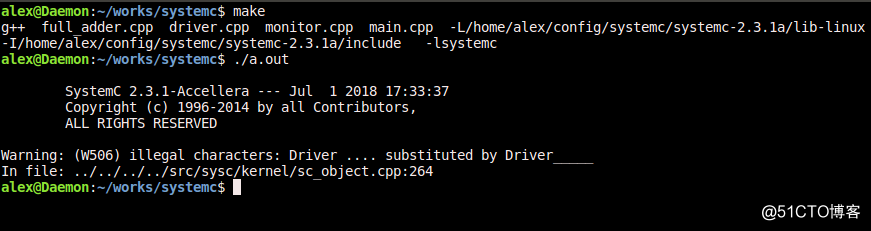

在解决这些问题后,终于正常通过了,正打算看看结果,却发现:

似乎和systemC内建的关键字冲突了,后来改了Driver,但还是显示相同的警告。

由于还没开始学习如何编写sc测试平台,所以暂时还不知道为什么会这样。。

暂且把问题留在这吧,等博主过段时间再来解答

以上是关于systemC全加器建模的主要内容,如果未能解决你的问题,请参考以下文章