Verilog设计流程问题

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Verilog设计流程问题相关的知识,希望对你有一定的参考价值。

请问用Verilog HDL设计一个数字系统的具体步骤,从建立基本模块到生产出具体的物理芯片,请哪位大虾简单说明一下,小弟刚刚接触。

1. 设计规划阶段(Design Specification)一个Design Specification的建立有赖于市场人员对所设计芯片的大致功能和成本提出要求,市场人员和工程师互相合作提出芯片的功能

2. 架构与设计划分阶段(Architecture and Design Partition)

拟订开发部门的工程规格(Engineering spec),必须决定系统的架构

3. 编程有测试环境阶段

完成基本的设计和仿真。在初期,设计人员就应该考虑个信号的走线问题!在高速电路和多信号设计中,必须考虑到将产生的串扰(Cross Talk)。

4. 集成和仿真阶段(Integration and Simulation)

l 文件对比验证:预计输出(Expected Value)文件和电路真正的输出结果(Exact Result)的对比。

l 穿越整个CHIP:测试向量(Test Vector)要求能穿越整个CHIP到达外部。

l 合并测试向量:合理的合并测试向量并适度地打散激励(EXCIATION)

l 共享测试环境:在各模块已做整合的前提之下,各模块应该共享测试环境。

l 对模拟器件的处理:需要针对模拟器件做特殊的仿真。

5. 综合阶段(Synthesis)

综合阶段对程序代码的逻辑做部分简化,并从标准单元中选取合适的单元组合成最佳的实际电路。而这个原则就是约束(CONSTRAINT FILE),这个文件决定了最后CHIP的SIZE和功能的实现。基本上综合就是Timing与Area之间求得一个平衡。

这个时候最好完成功耗分析(POWER ANALYSIS)

6. 布局前仿真

待测对象:由逻辑门(GATE-LEVEL)所组成的网表文件(NETLIST)。这个阶段的仿真结果必须和INTEGRATION AND SIMULAION阶段一致。

特点:这个阶段仿真时间一般比较长,利用操作系统所提供的工具程序来做自动化的批处理就显得重要,例如UNIX提供的MAKE等工具程序

7. 布局与布线阶段(AUTO PLACEMENT AND ROUTE ,AP&R)

利用netlist和SYNTHESIS产生的CONSTRAINT FILE文件

目的:将实体的单元(CELL)组合成芯片上真正的电路。

l FloorPlan:决定管脚的排列和IP,MACRO等在IC内部摆放的位置。

l Placement:布局,将元件摆到适当的位置。何谓合适的位置,就要根据具体电路的功能,工程师的经验和不断地对结果的分析了。

l CTS(Clock Tree Synthesis):将时序器件所需要的时钟所需要的缓冲器放在合适的位置,避免产生CLOCK SKEW。

l ROUTE:将各元件(包括时钟缓冲器)正确地走线。

l SDF(Standard Delay Format):此文件的目的在于描述确切地元件及布线时间延迟,以作为前端设计者再仿真的延迟计算,或作为静态时序分析之用。这些Timing 数值的前提是必须将线路的负载的R,C值提取出来。

8. 布局后仿真/静态时序分析/形式验证阶段(Post-Sim/STA/Formal Verification)

l Post-sim: 和前仿真必须的结果必须完全相同,但是因为有了更精确的TIMING数据,所以花费更大量的时间

l STA:仿真本身可分为动态和静态

动态性:从仿真的起始至结束有许多个时间(EVENT)发生来校验其功能。耗时长

静态时序分析:它并不管其待分析电路的功能如何,只要给定Constraint,静态时序分析就会分析电路结构,检查所有时序上不满足的地方。

l Formal Verification:?

9.DRC/LVS检查阶段

DRC(Design Rule Check):针对最后的LAYOUT结果做检查,以校验其是否违反元件本身的性能限制。

LVS(Layout VS Schematics):针对电路图和LAYOUT图做一致性验证。

10.Design sign-off阶段

即掩膜生产之用,就是一般所称的Tape-Out.

11.手动修正(Engineering Change Order,ECO)

如果最后阶段发现了BUG,如果不大的话,那么如果从头改起将十分耗时,比较经济的做法是以手动的方式对电路进行修改,或者对布局修改。

因为手动修改非常容易出错,所以需要非常深厚的基本电路知识和经验!

如果已经TAPE-OUT才发现设计上的错误,则最后的补救只能在金属层的掩膜上修改 参考技术A 逻辑分析-构架-Verilog程序-综合-验证-时序分析-验证-布线-版图

大概就这样吧

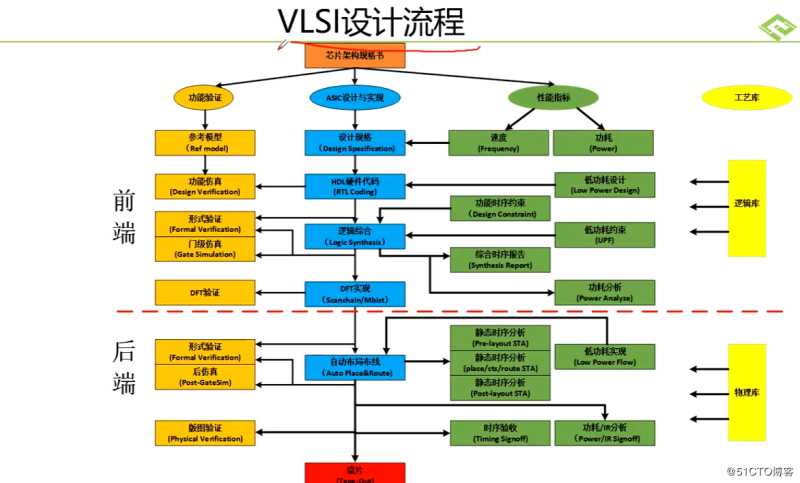

1.数字IC设计全流程

一、基于standcell的ASIC设计流程??所谓standcell library即为标准单元库,主要指数字电路,反相器,与非门,或非门,异或门,施密特触发器之类的 基本元器件。

设计流程为:

?算法模型(C/C++/Matlab)--->RTL HDL VHDL/Verilog--->NetlistVerilog--->Layout GDSII--->Tape-Out

standcell library包含:NetlistVerilog和Layout GDSII

RTL HDL VHDL/Verilog--->NetlistVerilog 逻辑综合工具根据基本单元库的功能-时序模型,将行为级代码翻译成具体的电路实现结构

Netlist Verilog--->Layout GDSII 布局布线工具根据基本单元库的时序-几何模型,将电路单元布局布线成实际电路板图

Layout GDSII--->Tape-Out 对功能,时序,制造参数进行检查二、数字IC设计全流程

Marketing request -->Architecture Spec.-->Arch/Algorithm Emulation -->Design Spec.-->RTL Coding-->IP Level RTL coding-->IP Level RTL simulation-->Unit/chip Level RTL simulation-->Logic Synthesis(逻辑综合)-->形式验证-->STA(静态时序分析)-->DFT(design for test)-->PR版图生成,自动布局布线-->时钟树插入-->DRC/LVS -->Post layout STA -->生成GDSII

在上面的流程中,工程师职责与使用工具可总结为下表

| 流程 | 工程师 | 工作 | 工具 |

|---|---|---|---|

| Marketing request | - | - | - |

| Architecture Spec. | Architecture engineer | Top atchitect,Project function spec | - |

| Arch/Algorithm Emulation | Algorithm Engineer | - | C/C++/Matlab |

| Design Spec. | - | Design spec example | - |

| RTL Coding | RTL design engineer | - | 使用VHDL/Verilog/System Verilog实现 |

| IP Level RTL coding | - | - | - |

| IP Level RTL coding | IP level verification engineer | IP level verification | Make file;仿真验证工具,Cadence:Incisive,Synopsys:VCS,Mentor:QuestaSim |

| Unit/chip Level RTL simulation | Integrate engineer | Unit/chip level verification(full chip verification engineer) | - |

| Logic Synthesis | ASIC Design Engineer | Gate Level verification | 逻辑综合工具,Cadence:Genus,Synopsys:Design Compiler |

| 形式验证 | ASIC Front-End Design Engineer | - | 形式验证工具,Cadence:Conformal,Synopsys:Formality |

| STA(静态时序分析) | ASIC Front-End Design Engineer | TCL Script | 静态时序分析工具,Cadence:Tempus,Synopsys:Prme Time |

| DFT(design for test) | DFT engineer | 插入可测试链scan chain | - |

| PR版图生成,自动布局布线 | Physical Design Engineer | - | 自动布线工具,Cadence:Innovus,Synopsys:IC Compiler |

| 时钟树插入 | - | - | - |

| DRC/LVS | - | - | 物理验证工具,Cadence:Diva/dracula,Synopsys:Hercules,Mentor:Calibre |

| Post layout STA | - | - | - |

| 生成最终GDSII | - | - | - |

| Tap-Out | - | - | - |

逻辑综合就是把设计实现的RTL代码映射到特定的工艺库,输出成门级网表Netlist

从功能上(STA是时序上)对综合后的网表进行验证。常用的就是等价性检查(Equivalence Check),以功能验证后的HDL设计为参考,对综合后的网表功能,他们是否在功能上存在等价性。

静态时序分析,主要在时序上对电路进行验证,检查电路是否存在建立时间,保持时间的违例前端设计与后端设计

前端设计(RTL to Netlist)

RTL(Register Transfer Level)利用引荐描叙语言对电路以寄存器之间的传输进行描述

逻辑综合:将RTL级设计中所得的程序代码翻译成实际电路的各种元器件以及他们的连接关系,用一张图来表示成为网表(Netlist)

STA(static timing analysis,静态时序分析),套用特定的时序模型,针对电路分析是否违反给定的时序限制

后端设计(Netlist to Layout)

APR(自动布局布线)-->Extract RC(提取延时信息)-->DRC(设计规则检查)-->LVS(版图电路一致性检查)VSLI设计流程

以上是关于Verilog设计流程问题的主要内容,如果未能解决你的问题,请参考以下文章