IIC总线协议和时序

Posted xuexizhe

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了IIC总线协议和时序相关的知识,希望对你有一定的参考价值。

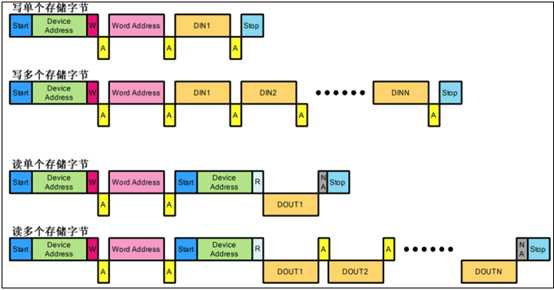

IIC标准速率为100Kbit/s,快速模式400Kbit/s,支持多机通信,支持多主控模块,但是同一时刻只允许有一个主控。由数据线SDA和时钟SCL构成串行总线;每个电路模块都有唯一地址。I2C设备的操作可分为写单个字节存储,写多个字节存储,读单个存储字节和读多个存储字节,操作如下:

a) 总线空闲状态

I2C总线的SDA和SCL两条信号线同时处于高电平时,规定为总线的空闲状态。此时各个器件的输出级的场效应管均处于截止状态,即释放总线,由两条信号线各自的上拉电阻把电平拉高。

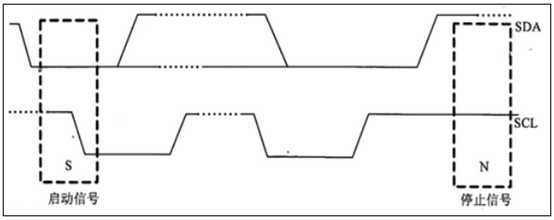

b) 启动信号(start)

在时钟线SCL保持高电平期间,数据线SDA上的电平被拉低(负跳变),定义为I2C总线的启动信号,它标志着一次数据传输的开始。启动信号是由主控器主动建立的,在建立该信号之前 I2C 总线必须处于空闲状态。

c) 停止信号(stop)

在时钟线SCL保持高电平期间,数据线SDA被释放,使得SDA返回高电平(即正跳变),称为I2C总线的停止信号,它标志着一次数据传输的终止。停止信号也是由主控器主动建立的,建立该信号之后,I2C总线将返回空闲状态。

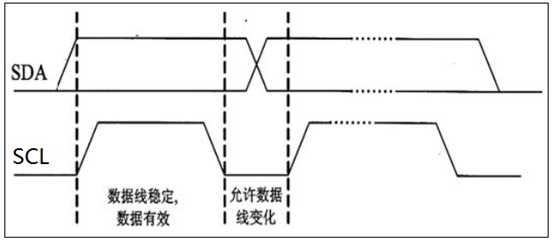

d) 数据位传送

在I2C总线上传送的每一位数据都有一个时钟脉冲相对应(或同步控制),即在SCL串行时钟的配合下,在SDA上逐位地串行传送每一位数据。进行数据传送时,在SCL呈现高电平期间,SDA上的电平必须保持稳定,低电平为数据0,高电平为数据1。只有在SCL为低电平期间,才允许SDA上的电平改变状态。

e) 应答信号(ACK和NACK)

I2C总线上的所有数据都是以8位传送的,发送器每发送一个字节,就在时钟脉冲9期间释放数据线,由接收器反馈一个应答信号。应答信号为低电平时,规定为有效应答位(ACK简称应答位),表示接收器已经成功地接收了该字节;应答信号为高电平时,规定为非应答位(NACK),一般表示接收器接收该字节没有成功。对于反馈有效应答位ACK的要求是,接收器在第9个时钟脉冲之前的低电平期间将 SDA 线拉低,并且确保在该时钟的高电平期间为稳定的低电平。

如果接收器是主控器,则在它收到最后一个字节后,发送一个NACK信号,以通知被控发送器结束数据发送,并释放SDA线,以便主控接收器发送一个停止信号。

以上是关于IIC总线协议和时序的主要内容,如果未能解决你的问题,请参考以下文章

: IIC(I2C Inter-Intergrated Circuit 集成电路总线) IIC时序图(IIC协议) I2C模拟时序STM32F4XX的IIC通信重载print

: IIC(I2C Inter-Intergrated Circuit 集成电路总线) IIC时序图(IIC协议) I2C模拟时序STM32F4XX的IIC通信重载print

: IIC(I2C Inter-Intergrated Circuit 集成电路总线) IIC时序图(IIC协议) I2C模拟时序STM32F4XX的IIC通信重载print

STM32第七章: IIC(I2C Inter-Intergrated Circuit 集成电路总线) IIC时序图(IIC协议) I2C模拟时序STM32F4XX的IIC通信重载print