PCIE协议解析 synopsys IP PCI Express Capability 读书笔记(13)

Posted yijingjing17

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了PCIE协议解析 synopsys IP PCI Express Capability 读书笔记(13)相关的知识,希望对你有一定的参考价值。

1.1.1 PF PCI Express CapabilityRegister Details

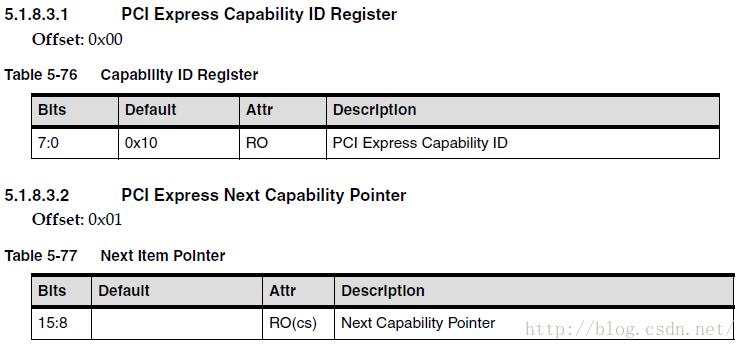

Core实现了PCIe 3.0定义的所有Capability Structure,除了Root Port register。

| Byte Offset | Byte 3 | Byte 2 | Byte 1 | Byte 0 |

|

| PCI Express Capabilities Register | Next Capability Pointer | Capability ID (0x10) | |

| +0x4 | Device Capabilities | |||

| +0x8 | Device Status | Device Control | ||

| +0xC | Link Capabilities | |||

| +0x10 | Link Status | Link Control | ||

| +0x24 | Device Capabilities 2 | |||

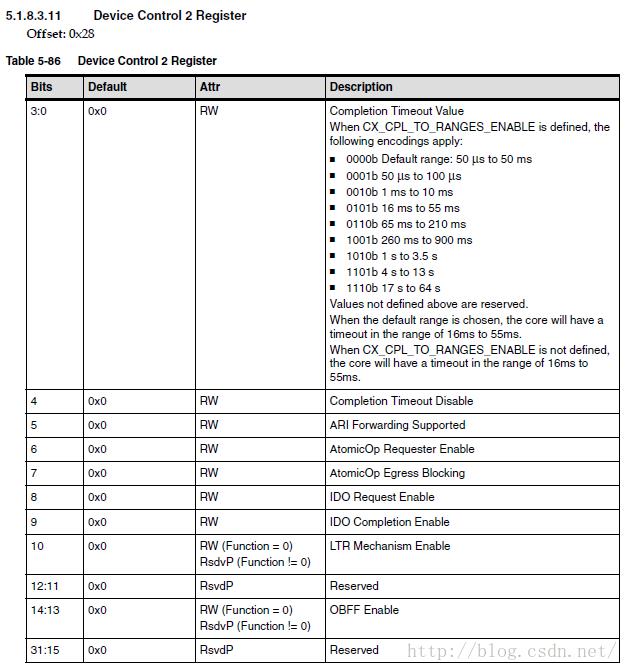

| +0x28 |

| Device Control 2 | ||

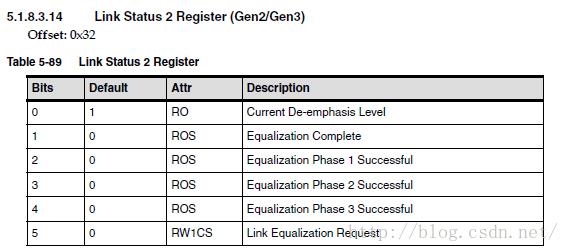

| +0x30 | Link Status 2 | Link Control 2 | ||

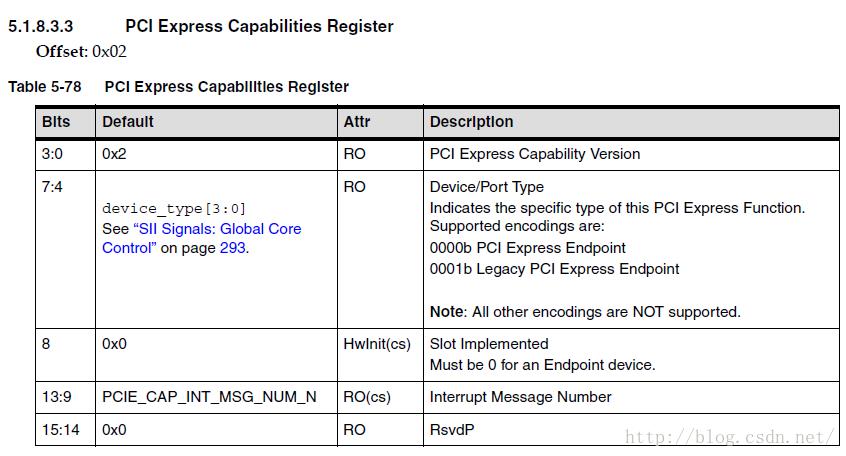

Ø PCI ExpressCapability Version:存放PCIe设备的版本号,PCIe总线规范1.x,该字段对应值为0x01。

PCIe总线规范2.x,该字段对应值为0x02

Ø Device/Port Type:000b:PCIe endpoint

0001b:legacy PCIe endpoint

针对EP模式下,其他都不支持

Ø Slot Implemented:0:PCIe设备 1:代表当前端口为PCIe插槽

Ø Interrupt MessageNumber:当PCIe Capability结构的Slot Statue寄存器或者Root Status寄存器的状态发生变化时,该PCIe设备可以通过MSI/MSI-X中断机制向处理器提交中断请求。该字段存放MSI/MSI-X中断机制需要的Message Data字段。

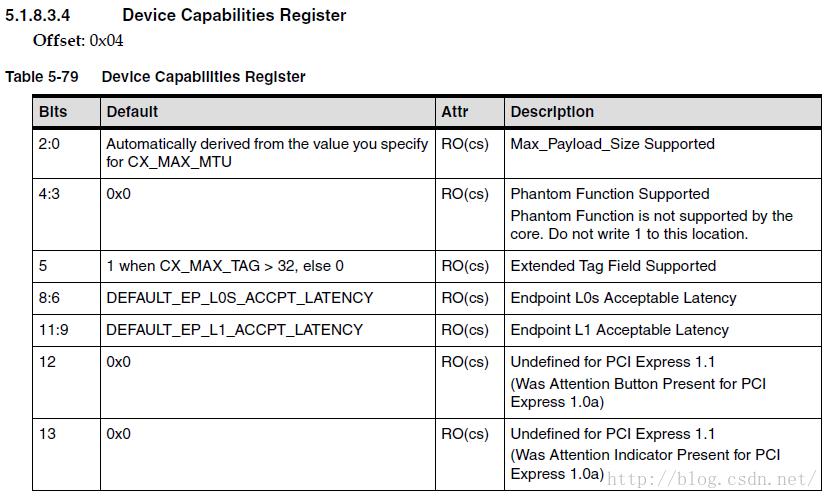

Ø Max_Payload_Size Supported:该字段决定TLP报文可能使用的最大有效负载,PCIe总线规定Max_Payload_Size参数最大值为4096B,但是许多PCIe设备并不一定支持这么大的有效负载。实际应用中,一个PCIe设备支持的Max_Payload_Size参数通常为128B、256B、512B。

Max_Payload_Size Supported字段表示该PCIe设备允许使用的Max_payload_szie参数。在Device Control寄存器中,还有一个Max_payload_Size参数,该字段可以由软件设置,表示实际使用的Max_Payload_Size参数大小。

| Bit[2:0] | 支持的Max_Payload_Size |

| 0b000 | 128B |

| 0b001 | 256B |

| 0b010 | 512B |

| 0b011 | 1024B |

| 0b100 | 2048B |

| 0b101 | 4096B |

实际中,Max_Payload_Size Supported参数和Max_Payload_Size参数值可能不同,前者为PCIe设备能够支持的最大的Payload的大小,而后者是链路两端的PCIe设备进行协商,确定的实际使用值。

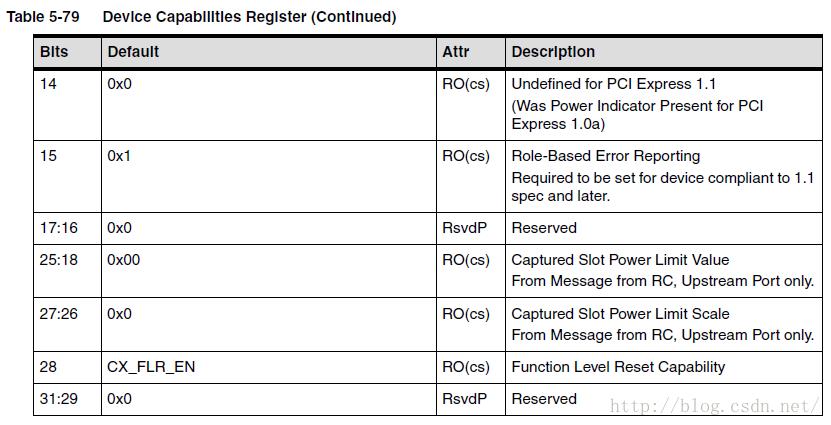

Ø Phantom FunctionSupported:Core不支持

Ø Extended Tag FieldSupported:为1时:TLP的Tag字段为8bit,为0时:表示Tag字段为0bit。

Ø Correctable ErrorReporting Enable:为1是表示PCIe设备可以发出ERR_CORMessage报文。否则不支持。

Ø Non-Fatal ErrorReporting Enable:为1是表示PCIe设备可以发出ERR_ Non-Fatal Message报文。否则不支持。

Ø Fatal ErrorReporting Enable:为1是表示PCIe设备可以发出ERR_ Fatal Message报文。否则不支持。

Ø Unsupported RequestReporting Enable:为1是表示PCIe设备可以发出Unsupported RequestReporting Enable报文。否则不支持。

Ø Enable RelaxedOrdering:在CORE无效

Ø Max_Payload_Size:PCIe设备根据DeviceCapability寄存器的Bit[2:0]字段设置PCIe设备的TLP的最大payload。系统软件根据PCIe链路两端的实际情况,确认该字段的值。但是该值不能大于Device Capability寄存器的“Max_payload_sizeSupport”字段。PCIe设备发送TLP时,其最大的Payload不能大于Max_Payload_Size;当PCIe设备接收TLP时,必须能够处理小于该字段的TLP,而大于该字段的TLP将被认为错误报文。

Ø Extended Tag FieldEnable :该位为1:发送端可以使用8bit的Tag字段,该位为0时,使用5bit的字段。

Ø Phantom FunctionEnable:该位为1:使能Phantom Function。

Ø AUX Power PM Enable:该位为1:PCIe设备可以使用总线提供的辅助电源。

Ø Enable No Snoop:该位为1:PCIe设备可以发生TLP时,该TLP的Attribute字段可以设置为NoSnoop;该位为:TLP的Attr字段不能设置为NO Snoop。

Ø Max_Read_Request_Size:该字段记录在一个PCIe设备中,存储器读请求TLP可以请求的最大数据区域。当PCIe设备发送存储器读请求TLP时,该TLP所请求的数据大小不能超过Max_Read_Request_Size。

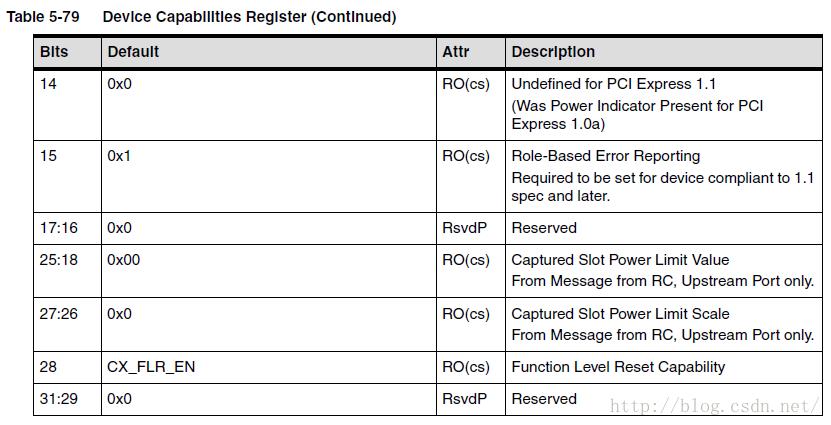

Ø Initiate FLR:该位为1:启动functionLevel Reset

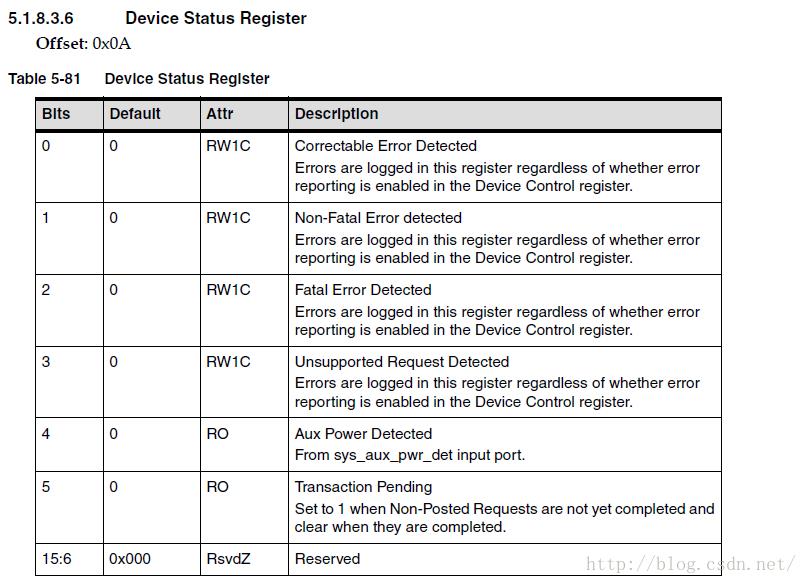

Ø Correctable ErrorDetected:该位为1表示PCIe检测到CorrectableError,对该位写1将清除此位。

Ø Non-Fatal Errordetected:该位为1表示PCIe检测到Non-FatalError,对该位写1将清除此位。

Ø FatalError Detected:该位为1表示PCIe检测到Fatal Error ,对该位写1将清除此位。

Ø Unsupported RequestDetected:该位为1表示PCIe检测到不支持的报文,对该位写1将清除此位。

Ø Aux Power Detected:当PCIe设备检测到辅助电源的存在时,而且如果该设备需要使用辅助电源,则该位置1

Ø Transaction Pending:对于EP而言,该位为1表示当前的PCIe设备发送了一个Non-Posted的数据请求,但是没有收到完成的报文应答;对于RC和Switch而言,该位为1表示RC和Switch自身发送了一个Non-Posted的数据请求,但是没有收到完成的报文应答。

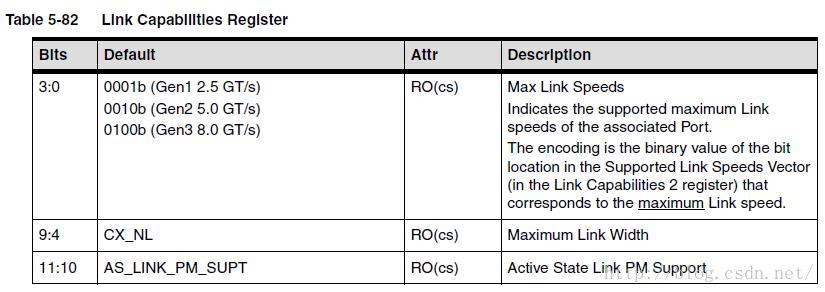

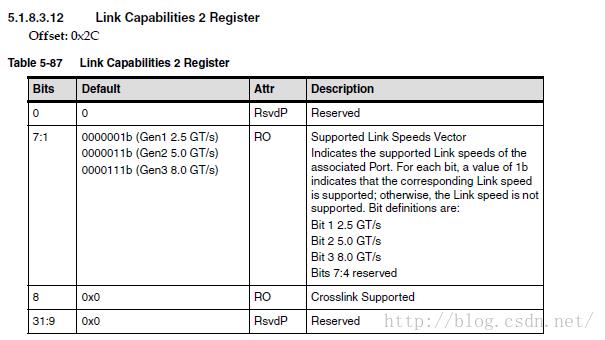

Ø Max Link Speeds:0b0001表示PCIe链路支持2.5GT/s,0b0010表示PCIe链路支持5.0GT/s,0b0100表示PCIe链路支持8GT/s.

Ø Maximum Link Width:PCIe设备支持的最大链路宽度。000001:表示支持x1的PCIe链路。000010:表示支持x2的PCIe链路。000100:表示支持x4的PCIe链路。001000:表示支持x8的PCIe链路。001100:表示支持x12的PCIe链路。010000:表示支持x16的PCIe链路。100000:表示支持x32的PCIe链路。

Ø Active State Link PMSupport:0b00和0b10为系统保留字段。当该字段为0b01时,表示ASPM支持L0s状态;当该字段为0b11时,表示ASPM支持L0s和L1状态。PCIe设备除了支持PCI PM电源管理方式之外,还执行ASPM机制进行电源管理。ASPM机制是CPIe设备进行的主动电源管理方式,与系统的软件没有直接的联系。

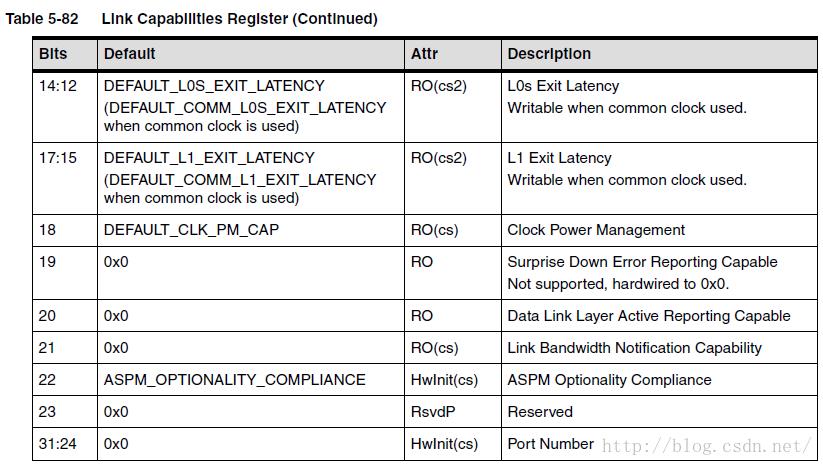

Ø L0s Exit Latency 和L1 Exit Latency:定义了PCIe设备从L0s和L1状态退出的最小延时。

Ø Port Number:如果多端口的RC和Switch支持多个下游的端口,则使用该字段对这些端口进行编号。

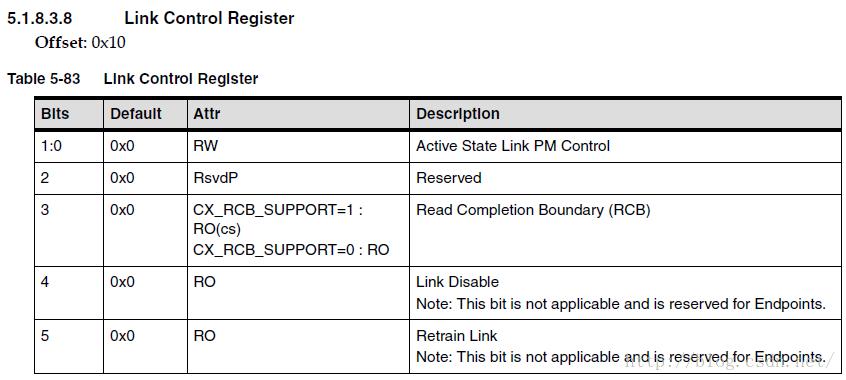

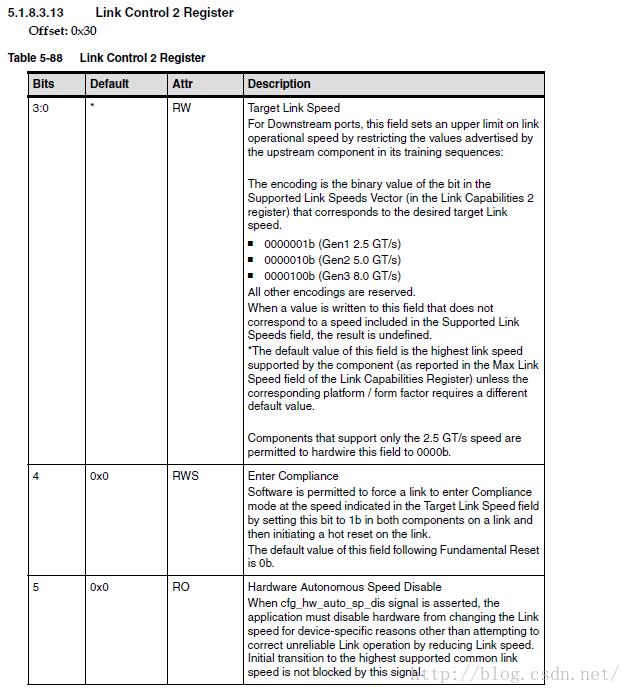

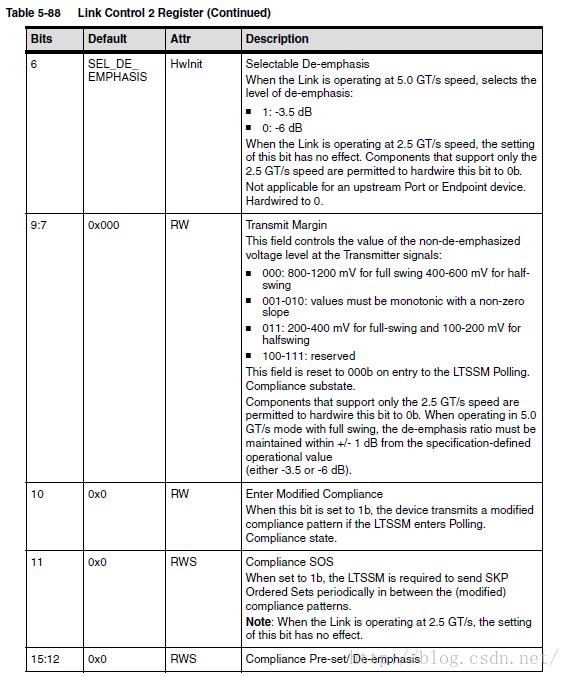

Ø Active State Link PMControl:该字段为0b00是表示禁止PCIe设备的ASPM机制;为0b01是表示PCIe设备可以进入L0s状态;为0b10时表示PCIe设备可以进入L1状态;为0b11是表示PCIe设备可以进入L0s和L1状态。值得注意的是系统软件不能通过修改该字段使PCIe链路进入相应的状态,仅是通知硬件逻辑,可以进入相应的状态。

Ø Read CompletionBoundary (RCB):该位为0:表示RCB为64B,该位为1:表示RCB为128B。

Ø Link Disable:向该位写1,将禁止PCIe链路。

Ø Retrain Link:向此位写1,将从新训练PCIe链路。

Ø Common ClockConfiguration:该位为1:表示PCIe的链路两端设备使用同源的参考时钟;该位为0:表示PCIe链路两端的设备使用参考时钟不同源。

Ø Extended Synch:该位为1时,表示PCIe设备退出L0s和进入Re-Covery状态时,需要额外的发出一些同步序列。

Ø Hardware AutonomousWidth Disable:CORE不支持。为1:表示PCIe设备不能改变当前已经协商好的PCIe链路宽度,除非为了修正PCIe链路中已经出现错误的Lane。

Ø Link BandwidthManagement Interrupt Enable:当该位为1时,且Link Status寄存器的Link Bandwidth Management Status位为1时,PCIe设备将向处理器提交中断请求。此时这中断请求使用的中断向量由PCI ExpressCapability寄存器的Interrupt MessageNumber字段确定。

Ø Link AutonomousBandwidth Interrupt Enable:该位为1时,且Link Status寄存器的Link Autonomous Bandwidth Status位为1时,PCIe这边将向处理器提交中断请求。

Ø Link Speed:0b0001表示PCIe链路支持2.5GT/s,0b0010表示PCIe链路支持5.0GT/s,0b0100表示PCIe链路支持8GT/s。

Ø Negotiated LinkWidth:PCIe设备当前的链路宽度。000001:表示支持x1的PCIe链路。000010:表示支持x2的PCIe链路。000100:表示支持x4的PCIe链路。001000:表示支持x8的PCIe链路。001100:表示支持x12的PCIe链路。010000:表示支持x16的PCIe链路。100000:表示支持x32的PCIe链路。

Ø Link Training:未使用

Ø Slot ClockConfiguration:该位由PCIe设备在初始化时确定,该位为1表示PCIe插槽和Add-In卡使用的参考时钟相同。

Ø Data Link LayerActive:该位表示PCIe链路的状态。该位为1时,表示PCIe链路处于DL_Active,即正常工作状态。

Ø Data Link LayerActive:该位由PCIe硬件设置。当CPIe链路重训练结束,或者PCIe设备完成PCIe链路的宽度和链路速度设定后,该位置1.该位写1清除。

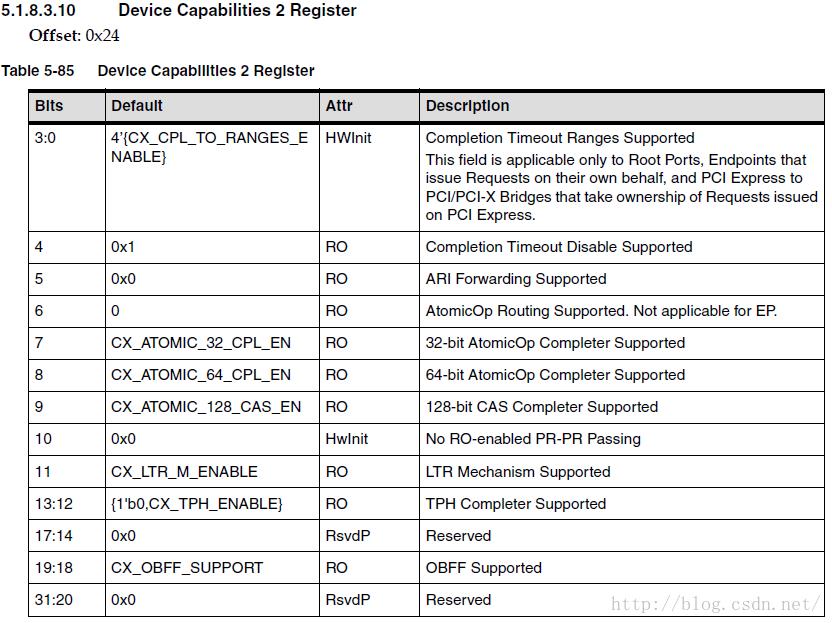

Ø AtomicOp RoutingSupported: Switch的上下游端口和RC端口支持该位,在PCIe V2.1总线规范定义了原子操作。该位为1,标准原子操作TLP可以通过当前的Switch或者RC。

Ø 32-bit AtomicOpCompleter Supported:为1:表示支持32位的原子操作。

Ø 64-bit AtomicOpCompleter Supported:为1:表示支持64位的原子操作。

Ø 128-bit CASCompleter Supported:为1:表示支持128位的原子操作。

Ø TPH CompleterSupported:为0b00:表示接收端不支持TPH和扩展TPH报文;为0b01:表示接收端仅支持TPH报文;为0b11:表示接收端支持TPH和扩展TPH报文;0b10保留。

Ø AtomicOp RequesterEnable:该位和Command寄存器的“Bus Master Enable“位同时有效,EP或者RC可以发出原子操作请求TLP。

Ø AtomicOp EgressBlocking:对Switch的上下游端口和RC端口有效。当AtomicOPRouting Supported位为1时,该位可以为1,否则该位只能为0.该位为1时,Egress端口将阻止原子操作TLP通过。

Ø IDO Request Enable:该位为1时,TLP中的IDO(ID-Based Ordering)位可以根据实际的情况设置为1.IDO是PCIeV2.1总线规范引入的新的“序“模型。

Ø IDO CompletionEnable:该位为1时,EP可以出来IDO位为1的完成报文。

以上是关于PCIE协议解析 synopsys IP PCI Express Capability 读书笔记(13)的主要内容,如果未能解决你的问题,请参考以下文章