STA相关概念

Posted KuoGavin

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了STA相关概念相关的知识,希望对你有一定的参考价值。

文章目录

- 2.1 CMOS逻辑设计(CMOS Logic Design)

- 2.2 CMOS单元建模(Modeling of CMOS Cells)

- 2.3 电平切换波形(Switching Waveform)

- 2.4 传播延时(Propagation Delay)

- 2.5 波形的压摆(Slew of a Waveform)

- 2.6 信号偏斜(Skew between Signals)

- 2.7 时序弧(Timing Arcs and Unateness)

- 2.8 最小与最大时序路径(Min and Max Timing Paths)

- 2.9 时钟域(Clock Domains)

- 2.10 工作条件(Operating Condition)

- 相关术语

- 知乎翻译圣经

本章节介绍CMOS技术的基础知识以及执行静态时序分析所涉及的术语。

2.1 CMOS逻辑设计(CMOS Logic Design)

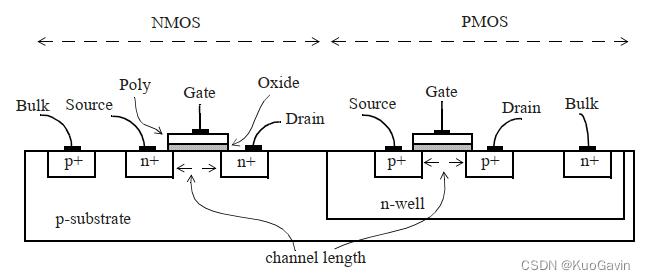

2.1.1 基本MOS结构(Basic MOS Structure)

基本MOS结构:MOS晶体管可分为PMOS和NMOS,区别见:nmos和pmos有什么区别。相较于三极管是电流控制电流,MOS是通过电压控制电流。其中源极和漏极间的距离(channel length)是MOS晶体管的长度,而用于构建MOS晶体管的最小长度即为CMOS技术工艺的最小特征尺寸(feather size)。

2.1.2 CMOS逻辑门(CMOS Logic Gate)

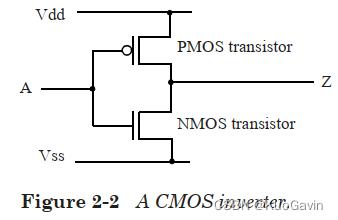

CMOS逻辑门使用NMOS和PMOS晶体管搭建而成:

- CMOS反相器两种稳定状态,取决于输入 A A A: A = l o w ( 0 ) A=low(0) A=low(0),NMOS截止,PMOS导通,进而 Z = h i g h ( 1 ) Z=high(1) Z=high(1); A = h i g h ( 1 ) A=high(1) A=high(1),NMOS导通,PMOS截止,进而 Z = l o w ( 0 ) Z=low(0) Z=low(0)。所以称为反相器(可脑补一下输入输出对照表);

- CMOS逻辑门中,输出节点通过上拉结构(由PMOS晶体管构成)连接至 V d d V_dd Vdd,并通过下拉结构(由NMOS晶体管构成)连接至 V s s V_ss Vss。且任何CMOS逻辑门,输出节点通过上拉结构(由PMOS晶体管构成)连接至 V d d V_dd Vdd,,并通过下拉结构(由NMOS晶体管构成)连接至 V s s V_ss Vss。

- 对于逻辑0或逻辑1的输入,由于上拉和下拉结构不能同时开启,因此处于稳态的CMOS逻辑门不会对输入或电源汲取任何电流。CMOS逻辑的另一个重要方面是,输入仅对前一级构成容性负载。

2.1.3 标准单元(Standard Cells)

芯片中复杂的逻辑功能大多是由具有简单逻辑功能的基本构建块(basic building blocks)像乐高一样搭建设计出来的。这些基本构件块是预先设计的,称为标准单元(standard cell)。其功能和时序已预先确定,供设计人员使用。

前面小节中描述的CMOS逻辑门的关键特性适用于所有CMOS数字设计。当输入处于稳定的逻辑状态时,所有数字CMOS单元的设计都能够保证不从电源汲取电流(漏电流除外)。因此,大多数功耗与设计的功能有关,并且是由设计中CMOS单元输入端的充放电引起的。

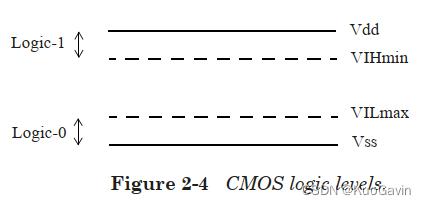

逻辑 0 0 0和逻辑 1 1 1的定义如下图所示。VIHmin(之上是1)和VILmax(之下是0)的值是从标准单元的直流传输特性中得出的。

2.2 CMOS单元建模(Modeling of CMOS Cells)

如果元件输出针脚驱动了数个扇出元件,那么该输出针脚的总电容:

t o t a l c a p a c i t a n c e = ∑ a l l c e l l s i t i s d r i v i n g i n p u t c a p a c i t a n c e s + ∑ a l l w i r e s e g m e n t s ′ c a p a c i t a n c e s w h i c h c o m p r i s e s n e t + o u t p u t c a p a c i t a n c e o f t h e d r i v i n g c e l l total\\;capacitance=\\sum_all \\;cells\\; it\\; is \\;drivinginput\\;capacitances\\\\+\\sum_allwire \\;segments'\\;capacitances\\;which\\;comprises\\;net\\\\+output\\;capacitance \\;of\\;the\\;driving\\;cell totalcapacitance=allcellsitisdriving∑inputcapacitances+all∑wiresegments′capacitanceswhichcomprisesnet+outputcapacitanceofthedrivingcell

总电容值是元件进行电平切换是需要充放电的电容值,因此该总电容值会影响该元件的时序特性。

当输出为逻辑1时,输出级的上拉结构导通,并提供了一条从输出到Vdd的路径。同样,当输出为逻辑0时,输出级的下拉结构提供了一条从输出到 V s s V_ss Vss的路径。当CMOS单元切换电平状态时,切换的速度取决于输出引脚上的电容被充放电的速度。输出引脚上的电容分别通过上拉和下拉结构充电和放电。注意,上拉和下拉结构中的通道会对输出的充放电路径构成电阻,充放电路径的电阻是决定CMOS单元速度的主要因素。上拉电阻的倒数称为单元的输出高电平驱动(output high drive)。输出上拉结构越大,上拉电阻就越小,即单元的输出高电平驱动就越大,较大的输出结构也意味着该单元的面积较大。而输出上拉结构越小,单元的面积就越小,其输出高电平驱动也就越小。上拉结构的相同概念可用于下拉结构,输出下拉结构决定了下拉路径的电阻值以及输出低电平驱动(output low drive)。通常,单元的上拉和下拉结构具有相似的驱动强度。

输出驱动

→

d

e

t

e

r

m

i

n

e

可驱动最大电容负载

→

d

e

t

e

r

m

i

n

e

扇出的最大数量

输出驱动\\xrightarrowdetermine 可驱动最大电容负载\\xrightarrowdetermine 扇出的最大数量

输出驱动determine可驱动最大电容负载determine扇出的最大数量

输出驱动决定了可以驱动的最大电容负载,最大电容负载又决定了扇出的最大数量,即可以驱动多少个其他单元。较高的输出驱动对应较低的输出上拉/下拉电阻,这使单元可以在输出引脚上对较大的负载进行充电和放电。

|

|

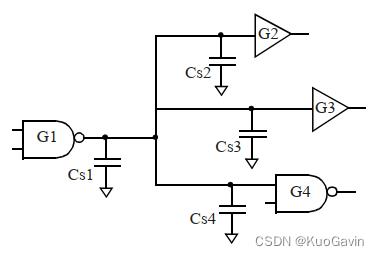

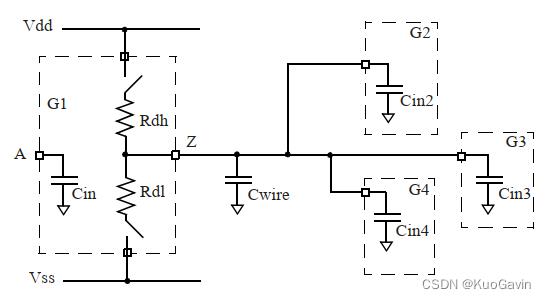

以上两图具有相同的网络,右图是左图使用等效模型表示CMOS单元的结果:

- C w i r e = C s 1 + C s 2 + C s 3 + C s 4 C_wire=C_s1+C_s2+C_s3+C_s4 Cwire=Cs1+Cs2+Cs3+Cs4

- 输出充放电延迟 = R o u t × ( C w i r e + C i n 2 + C i n 3 + C i n 4 ) 输出充放电延迟=R_out\\times (C_wire+C_in2+C_in3+C_in4) 输出充放电延迟=Rout×(Cwire+Cin2+Cin3+Cin4)

其中 R o u t R_out Rout是 R d h R_dh Rdh或者 R d l R_dl Rdl之一,分别对应上拉的输出驱动电阻和下拉的输出驱动电阻。引申:电容充电放电时间计算,充电: t = R C l n [ E / ( E − V t ) ] t=RCln[E/(E-V_t)] t=RCln[E/(E−Vt)],放电: t = R C l n ( E / V t ) t=RCln(E/V_t) t=RCln(E/Vt)。

2.3 电平切换波形(Switching Waveform)

如下图所示,按下SW0后电压将施加到RC网络,输出将变为逻辑1。若是按下时 V o u t = 0 V_out=0 Vout=0,那么充电过程的变化为: V o u t = V d d × [ 1 − e − t R d h × C l o a d ] V_out=V_dd\\times [1-e^\\frac-tR_dh\\times C_load] Vout=Vdd×[1−eRdh×Cload−t],如下图中间所示。乘积( R d h × C l o a d R_dh\\times C_load Rdh以上是关于STA相关概念的主要内容,如果未能解决你的问题,请参考以下文章