PCIe 驱动流程(LTSSM)

Posted yijingjing17

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了PCIe 驱动流程(LTSSM)相关的知识,希望对你有一定的参考价值。

本次的工作是完成刚流片的FPGA中PCIe IP核的bring up,也就是芯片的中PCIe的第一个使用者,将PCIe IP核正常使用起来,并配合公司的EDA团队,完成PCIe IP核到用户的呈现。

经过两个月的调试和文档阅读,对PCIe也有了初步的认识,对于PCIe的学习主要来自3个方面:

1、 王齐老师的《PCI Express 体系结构导读》和王齐老师的博客http://blog.sina.com.cn/s/blog_6472c4cc0100qbvp.html。非常感谢王齐老师的书,对于学习PCIe协议无疑是最佳的学习资料。

2、《PCI Express Base Specification 3.0》PCIe的标准协议。

3、 Synopsys公司提供 PCIe ip相关的data sheet。

以下是对PCIe建立链接过程的记录,主要针对Sysnosys 的PCIe的IP,但是同时应该也有普遍的适用性:

1.1 端口身份的识别

该部分是PCIe 底层Core识别PCIe端口的过程,PCIe总线中的有3中角色:RC(root complex)、EP(end point)、switch。他们在PCIe总线中拓扑结构如下图所示:

PCIe的IP Core在上电后首要的任务就是通过外部的IO或者寄存器,识别自身在PCIe的系统中扮演的角色,不同的角色也决定其在后续的过程中不同的启动和配置流程。

作为用户,在例化这个IP核时,需要做的第一个事情就是通过接口配置PCIe的device_type。

1.2 关注时钟与复位

在使用PCIe的IP时,再需要关注的是该内核的时钟和复位过程。可能作为用户,该过程硬件已经帮你做完了,但是也最最好熟悉一下结构和流程,并确保core的内部时钟已经启动,复位已经成功。

在实际的应用过程中,测试的第一步就是将PCIe core的时钟拉到芯片外部进行测试。

1.3 Disable PCIe的LTSSM的状态机

LTSSM(Link Training and Status State Machine )是PCIe最为核心的一个状态机,PCIe总线在进行链路训练时,将使用LTSSM状态机。而在启动LTSSM之前,用户一般需要进行参数的配置,所以在Core启动后,先会将LTSSM状态机disable。

1.4 通过DBI配置参数

该部分是配置PCIe参数的部分,DBI(data bus interface)是synopsys定义的访问PCIe寄存器的接口,PCIe协议规定了两种配置空间:PCI Configuration Space和 PCIe Extend configuration Space。而往往IP的生成商,会加入一个属于自己的配置空间,synopsys添加的配置空间为:Port logic Synosys Register。

其中PCI Configuration Space中主要由:PCI configuration header、PCI Power Management Capability、PCI Express Capability 、MSI Capability、MSI-X Capability VPD Capability组成。

PCI configuration header:提供了关于Vendor ID和Device ID等信息,其中比较重要的是Base Address Register(BAR),该寄存器设计到PCIe设备的地址空间的分配。

PCI Power Management Capability:该部分是系统电源管理的寄存器,这些Capability一般都会包含一个Status寄存器、一个Control寄存器、一个Capability寄存器。其中control寄存器通常是需要用户配置的,而Capability主要是供用户访问,以知道当前部分的参数设置的情况,而status寄存器是提供用户访问,以获得当前部分(比如电源)的具体的状态。

PCI Express Capability:该结构存放了一些和PCIe总线相关的信,包括PCIe链路和插槽的信息。

MSI、MSI-X:为中断控制的capability,与Power Management capability寄存器的结构是类似的。

PCIe Extend configuration Space是PCIe设备独有的,PCI设备并不支持该结构,实际上绝大多数的PCIe设备也不支持该结构。

Port logic SynosysRegister:是synopsys公司针对自身的IP,定义的与接口相关的寄存器,该部分寄存器多与物理层相关。

在此时的测试过程中,以进行Loopback测试为例,主要需要设置的参数包括PCI configurationheader和Port logicSynosys Register。

1、 Set the PIPE Loopback Enable bit

2、 Set the Loopback Enable bit

3、 设置BAR地址分配寄存器。

1.5 启动LTSSM

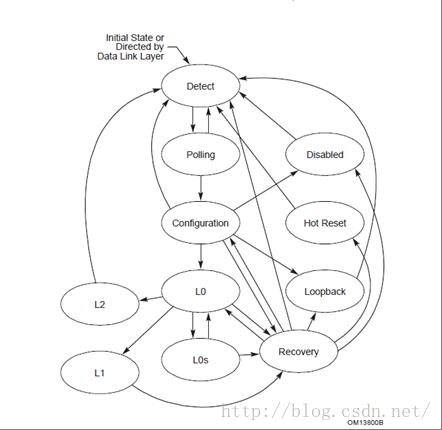

app_ltssm_enable=1;LTSSM状态机的跳转如下图所示,而当状态机进入Loopback状态机后,表示PCIe工作正常。

1.6 检测LTSSM状态机

检测LTSSM状态的方式有两种:

1、 通过Port logic Synosys Register中寄存器Debug Register 0中的最低6bit查询

2、 通过cxpl_debug_info IO直接查询。

在确认LTSSM状态机进入Loopback之后,用户需要查询数据链路层的状态,通过PCI ExpressCapability register中的 Link status Register 的Data Link Layer Active位,可以确认PCIe数据链路层正常工作,用户可以进行TLP包的发送与接收。

以上是关于PCIe 驱动流程(LTSSM)的主要内容,如果未能解决你的问题,请参考以下文章