FPGA的学习:基于SPI协议的Flash驱动写操作控制

Posted 石小舟

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了FPGA的学习:基于SPI协议的Flash驱动写操作控制相关的知识,希望对你有一定的参考价值。

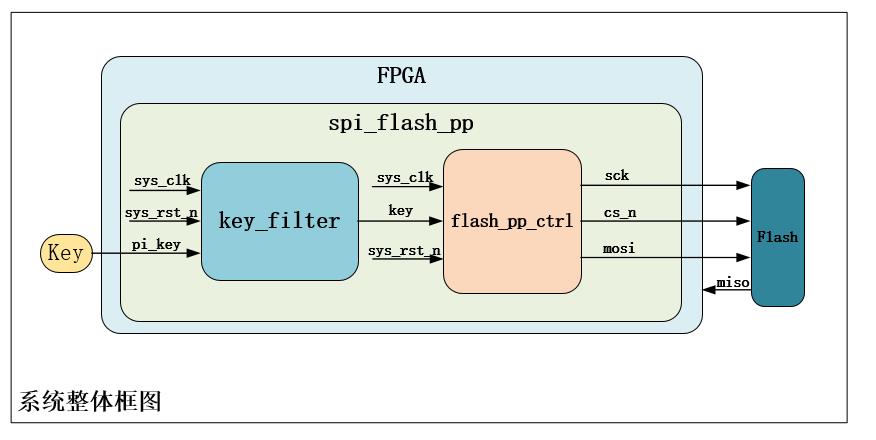

系统整体框图如图:

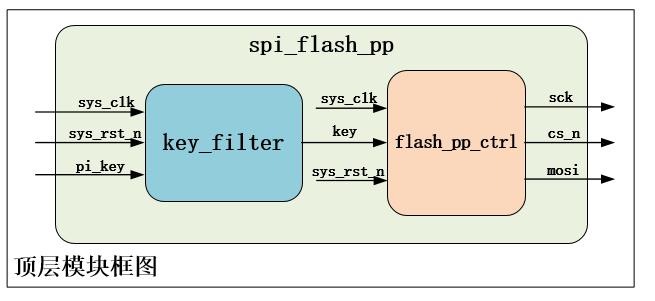

顶层模块的设计:

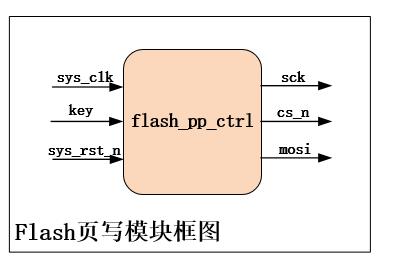

flash页写模块的设计:

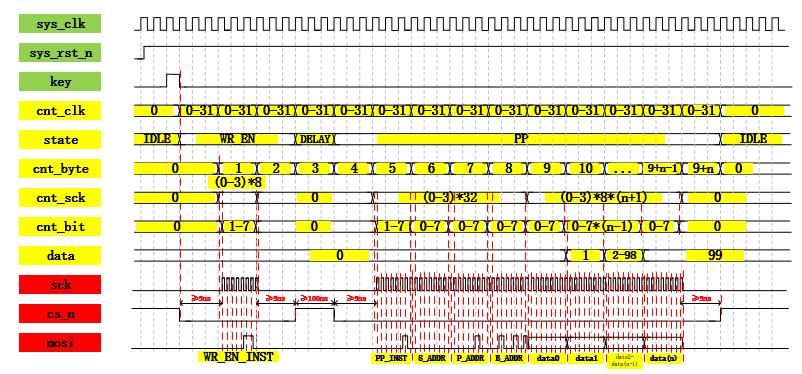

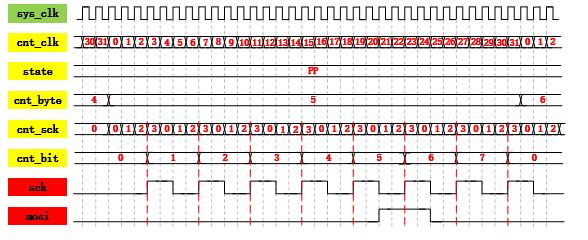

时序图:

页写的时序:

各个代码块如下:

`timescale 1ns/1ns

module key_filter

#(

parameter CNT_MAX = 20'd999_999 //计数器计数最大值

)

(

input wire sys_clk , //系统时钟50Mhz

input wire sys_rst_n , //全局复位

input wire key_in , //按键输入信号

output reg key_flag //key_flag为1时表示消抖后检测到按键被按下

//key_flag为0时表示没有检测到按键被按下

);

//********************************************************************//

//****************** Parameter and Internal Signal *******************//

//********************************************************************//

//reg define

reg [19:0] cnt_20ms ; //计数器

//********************************************************************//

//***************************** Main Code ****************************//

//********************************************************************//

//cnt_20ms:如果时钟的上升沿检测到外部按键输入的值为低电平时,计数器开始计数

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt_20ms <= 20'b0;

else if(key_in == 1'b1)

cnt_20ms <= 20'b0;

else if(cnt_20ms == CNT_MAX && key_in == 1'b0)

cnt_20ms <= cnt_20ms;

else

cnt_20ms <= cnt_20ms + 1'b1;

//key_flag:当计数满20ms后产生按键有效标志位

//且key_flag在999_999时拉高,维持一个时钟的高电平

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

key_flag <= 1'b0;

else if(cnt_20ms == CNT_MAX - 1'b1)

key_flag <= 1'b1;

else

key_flag <= 1'b0;

endmodule

`timescale 1ns/1ns

module spi_flash_pp

(

input wire sys_clk , //系统时钟,频率50MHz

input wire sys_rst_n , //复位信号,低电平有效

input wire pi_key , //按键输入信号

output wire cs_n , //片选信号

output wire sck , //串行时钟

output wire mosi //主输出从输入数据

);

//********************************************************************//

//****************** Parameter and Internal Signal *******************//

//********************************************************************//

//parameter define

parameter CNT_MAX = 20'd999_999; //计数器计数最大值

//wire define

wire po_key ;

//********************************************************************//

//*************************** Instantiation **************************//

//********************************************************************//

//------------- key_filter_inst -------------

key_filter

#(

.CNT_MAX (CNT_MAX ) //计数器计数最大值

)

key_filter_inst

(

.sys_clk (sys_clk ), //系统时钟,频率50MHz

.sys_rst_n (sys_rst_n ), //复位信号,低电平有效

.key_in (pi_key ), //按键输入信号

.key_flag (po_key ) //消抖后信号

);

//------------- flash_pp_ctrl_inst -------------

flash_pp_ctrl flash_pp_ctrl_inst

(

.sys_clk (sys_clk ), //系统时钟,频率50MHz

.sys_rst_n (sys_rst_n ), //复位信号,低电平有效

.key (po_key ), //按键输入信号

.sck (sck ), //片选信号

.cs_n (cs_n ), //串行时钟

.mosi (mosi ) //主输出从输入数据

);

endmodule

`timescale 1ns/1ns

module flash_pp_ctrl(

input wire sys_clk , //系统时钟,频率50MHz

input wire sys_rst_n , //复位信号,低电平有效

input wire key , //按键输入信号

output reg cs_n , //片选信号

output reg sck , //串行时钟

output reg mosi //主输出从输入数据

);

//********************************************************************//

//****************** Parameter and Internal Signal *******************//

//********************************************************************//

//parameter define

parameter IDLE = 4'b0001 , //初始状态

WR_EN = 4'b0010 , //写状态

DELAY = 4'b0100 , //等待状态

PP = 4'b1000 ; //页写状态

parameter WR_EN_INST = 8'b0000_0110, //写使能指令

PP_INST = 8'b0000_0010; //页写指令

parameter SECTOR_ADDR = 8'b0000_0000, //扇区地址

PAGE_ADDR = 8'b0000_0100, //页地址

BYTE_ADDR = 8'b0010_0101; //字节地址

parameter NUM_DATA = 8'd100 ; //页写数据个数(0-99)

//reg define

reg [7:0] cnt_byte ; //字节计数器

reg [3:0] state ; //状态机状态

reg [4:0] cnt_clk ; //系统时钟计数器

reg [1:0] cnt_sck ; //串行时钟计数器

reg [2:0] cnt_bit ; //比特计数器

reg [7:0] data ; //页写入数据

//********************************************************************//

//***************************** Main Code ****************************//

//********************************************************************//

//cnt_clk:系统时钟计数器,用以记录单个字节

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt_clk <= 5'd0;

else if(state != IDLE)

cnt_clk <= cnt_clk + 1'b1;

//cnt_byte:记录输出字节个数和等待时间

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt_byte <= 8'd0;

else if((cnt_clk == 5'd31) && (cnt_byte == NUM_DATA + 8'd9))

cnt_byte <= 8'd0;

else if(cnt_clk == 5'd31)

cnt_byte <= cnt_byte + 1'b1;

//cnt_sck:串行时钟计数器,用以生成串行时钟

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt_sck <= 2'd0;

else if((state == WR_EN) && (cnt_byte == 8'd1))

cnt_sck <= cnt_sck + 1'b1;

else if((state == PP) && (cnt_byte >= 8'd5)

&& (cnt_byte <= NUM_DATA + 8'd9 - 1'b1))

cnt_sck <= cnt_sck + 1'b1;

//cs_n:片选信号

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cs_n <= 1'b1;

else if(key == 1'b1)

cs_n <= 1'b0;

else if((cnt_byte == 8'd2) && (cnt_clk == 5'd31) && (state == WR_EN))

cs_n <= 1'b1;

else if((cnt_byte == 8'd3) && (cnt_clk == 5'd31) && (state == DELAY))

cs_n <= 1'b0;

else if((cnt_byte == NUM_DATA + 8'd9) && (cnt_clk == 5'd31) && (state == PP))

cs_n <= 1'b1;

//sck:输出串行时钟

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

sck <= 1'b0;

else if(cnt_sck == 2'd0)

sck <= 1'b0;

else if(cnt_sck == 2'd2)

sck <= 1'b1;

//cnt_bit:高低位对调,控制mosi输出

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

cnt_bit <= 3'd0;

else if(cnt_sck == 2'd2)

cnt_bit <= cnt_bit + 1'b1;

//data:页写入数据

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

data <= 8'd0;

else if((cnt_clk == 5'd31) && ((cnt_byte >= 8'd9)

&& (cnt_byte < NUM_DATA + 8'd9 - 1'b1)))

data <= data + 1'b1;

//state:两段式状态机第一段,状态跳转

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

state <= IDLE;

else

case(state)

IDLE: if(key == 1'b1)

state <= WR_EN;

WR_EN: if((cnt_byte == 8'd2) && (cnt_clk == 5'd31))

state <= DELAY;

DELAY: if((cnt_byte == 8'd3) && (cnt_clk == 5'd31))

state <= PP;

PP: if((cnt_byte == NUM_DATA + 8'd9) && (cnt_clk == 5'd31))

state <= IDLE;

default: state <= IDLE;

endcase

//mosi:两段式状态机第二段,逻辑输出

always@(posedge sys_clk or negedge sys_rst_n)

if(sys_rst_n == 1'b0)

mosi <= 1'b0;

else if((state == WR_EN) && (cnt_byte== 8'd2))

mosi <= 1'b0;

else if((state == PP) && (cnt_byte == NUM_DATA + 8'd9))

mosi <= 1'b0;

else if((state == WR_EN) && (cnt_byte == 8'd1) && (cnt_sck == 5'd0))

mosi <= WR_EN_INST[7 - cnt_bit]; //写使能指令

else if((state == PP) && (cnt_byte == 8'd5) && (cnt_sck == 5'd0))

mosi <= PP_INST[7 - cnt_bit]; //页写指令

else if((state == PP) && (cnt_byte == 8'd6) && (cnt_sck == 5'd0))

mosi <= SECTOR_ADDR[7 - cnt_bit]; //扇区地址

else if((state == PP) && (cnt_byte == 8'd7) && (cnt_sck == 5'd0))

mosi <= PAGE_ADDR[7 - cnt_bit]; //页地址

else if((state == PP) && (cnt_byte == 8'd8) && (cnt_sck == 5'd0))

mosi <= BYTE_ADDR[7 - cnt_bit]; //字节地址

else if((state == PP) && ((cnt_byte >= 8'd9)

&& (cnt_byte <= NUM_DATA + 8'd9 - 1'b1)) && (cnt_sck == 5'd0))

mosi <= data[7 - cnt_bit]; //页写入数据

endmodule

以上是关于FPGA的学习:基于SPI协议的Flash驱动写操作控制的主要内容,如果未能解决你的问题,请参考以下文章