数字ic设计|ASIC芯片开发过程

Posted IC观察者

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了数字ic设计|ASIC芯片开发过程相关的知识,希望对你有一定的参考价值。

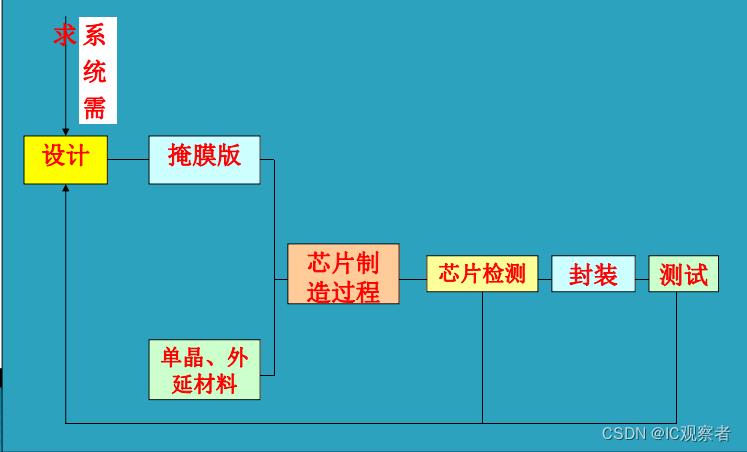

ASIC芯片开发过程,本文包含两个部分:ASIC芯片设计开发及ASIC芯片生产,今日给大家分享ASIC芯片设计开发,大家也可以去下载原文件:ASIC芯片设计生产流程

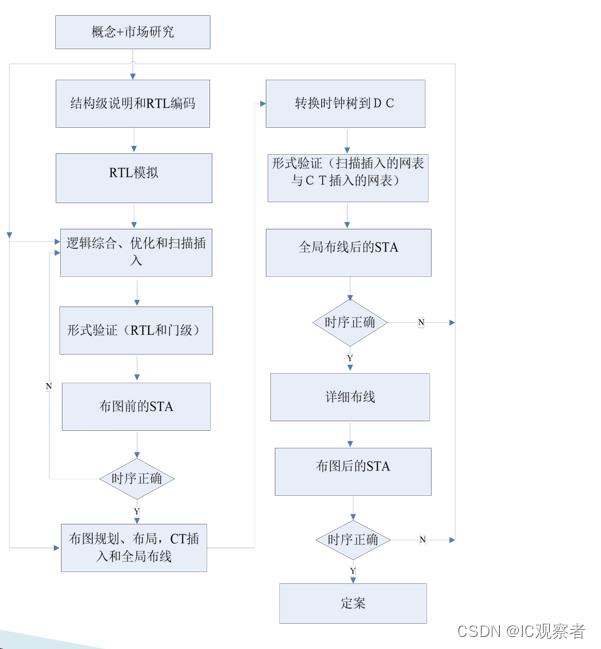

- 集成电路设计与制造全流程中的主要流程框架

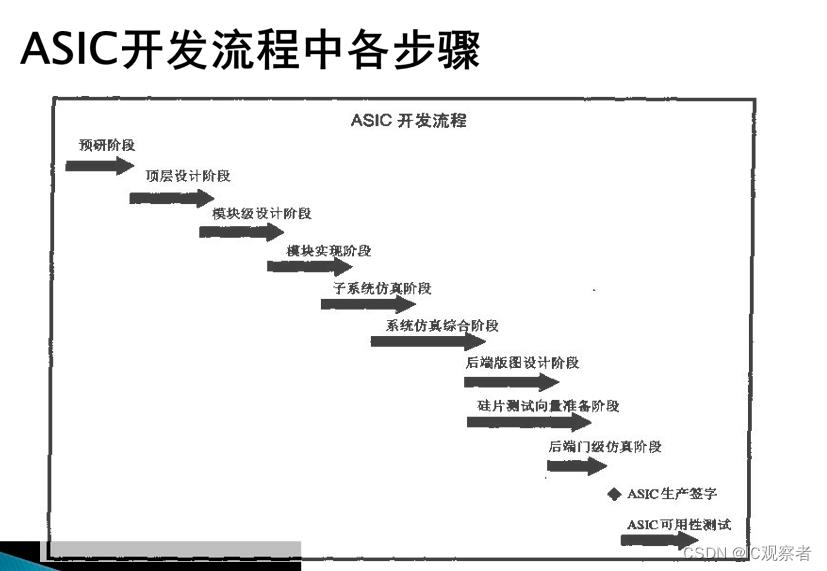

- ASIC项目的主要步骤包括:

预研阶段;

顶层设计阶段;

模块级设计阶段;

模块实现阶段;

子系统仿真阶段;

系统仿真,综合和版图设计前门级仿真阶段;

后端版面设计阶段;

测试向量准备阶段;

后端仿真阶段;

生产签字;

硅片测试阶段。

- 传统设计流程

- 设计的一般步骤(1)

1.结构及电学特性编码

2.HDL中的RTL编码

3.为包含存储单元的设计插入DFT memory BIST

4.为了验证设计功能,进行详尽的动态仿真

5.实际环境设置,包括将使用的工艺库及其他环境属性

6.使用Design Compiler工具对具有扫描插入的设计进行 约束和综合设计

7.使用Design Compiler的内建静态时序分析机进行模块级静态时序分 析

8.设计的形式验证,使用Formality将TRL和综合后的网表进行对比

9.使用PrimeTime进行整个设计布图前的静态时序分析 - 设计的一般步骤(2)

对布图工具进行时序约束的前标注

具有时序驱动单元布局,时钟树插入和全局布线的初始布局划分

将时钟树转换到驻留在Design Compiler中原始设计(网表)

在Design Compiler中进行设计的布局优化

使用Formality在综合网表和时钟树插入的网表之间进行形式验证

在全局布线后(11步)从版图提取估计的延时

从全局布线得到的估计时间数据反标注到PrimeTime

使用在全局布线后提取的估计延时数据在PrimeTime在中进行静态时 序分析。 - 设计的一般步骤(3)

- 设计的详细布局

提取来自详细布局设计的实际时间延迟

实际提取时间数据反标注到PrimeTime

使用PrimeTime进行布图后的静态时序分析

布图后的门级功能仿真(如果需要)

在LVS(版图对原理图)和DRC(设计规则检查)验证后定案

规范和RTL编码

结构规范定义了芯片的功能并划分为一些能够处理的模块,电学特性 规范通过时序信息定义模块之间的关系

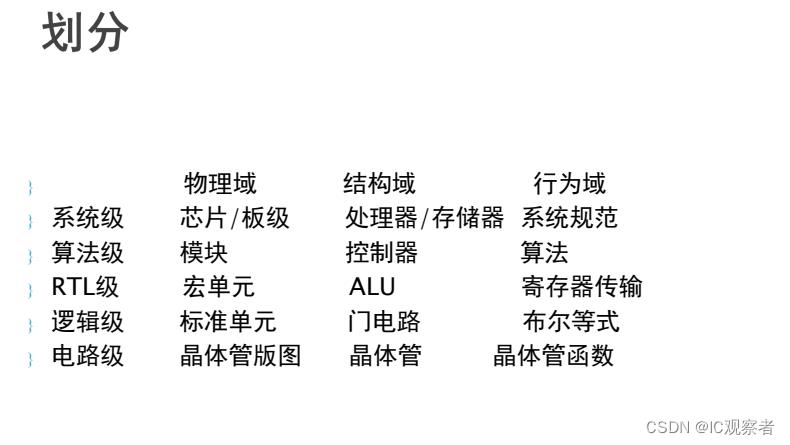

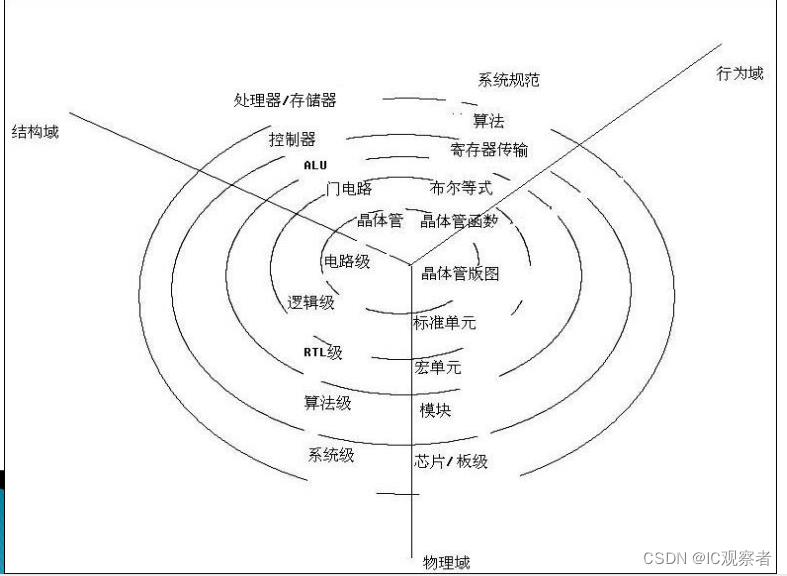

设计可用三个抽象层次来表示:行为级,寄存器传输级RTL和结构级。

动态仿真

通过仿真RTL代码以检查设计的功能,目前的仿真器都能够仿真行为 级及RTL级编码。

约束、综合和扫描插入

以前:手工将HDL转换为电路图并描述元件间的互连来产生一个门 级网表。

综合:用工具完成RTL级到门级网表的转换,这个过程就称为综合

定义综合环境的文件,详细说明了工艺单元库和

DC在综合过程中使用的其它相关信息。

形式验证

形式验证技术使用数学的方法来确认一个设计,不考虑工艺因素,如 时序,通过与参考设计的对比了检查一个设计的逻辑功能。

形式验证和动态仿真,形式验证技术通过证明两个设计的结构和功能 是逻辑等价的来验证设计;动态仿真只能检查敏感路经。

形式验证的目标是要验证RTL与RTL ,门级网表与RTL代码,两个门 级网表之间的对应关系是否正确。

静态时序分析

在整个设计中,静态时序分析是最重要的步骤,一个迭代过程。

静态时序分析充许用户详细分析设计的所有关键路经并给出一个有条 理的报告。

对布图前后的门级网表进行静态时序分析,在布图前,PrimeTime使 用由库指定的线载模型估计线网延时。如果所有关键路径的时序是可 以接受的,则由PrimeTime或DC得到一个约束文件,目的是为了预 标注到布图工具。

在布图后,实际提取的延迟被反标注到PrimeTime以提供真实的延迟 计算。

布局、布线和验证

布图工具完成布局和布线。布图规划包括单元的布局和时种树的综 合,在步图工具中完成。布线一般有两步,全局布线和详细布线。

以上是关于数字ic设计|ASIC芯片开发过程的主要内容,如果未能解决你的问题,请参考以下文章