verilog网站刷题记录

Posted 揭航

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了verilog网站刷题记录相关的知识,希望对你有一定的参考价值。

verilog网站刷题记录

网站

题目

https://hdlbits.01xz.net/wiki/Wire

答案

Basic

simple wire(一根线)

Create a module with one input and one output that behaves like a wire.

module top_module( input in, output out );

assign out = in;

endmodule

four wires(四根线)

Create a module with 3 inputs and 4 outputs that behaves like wires that makes these connections:

a -> w

b -> x

b -> y

c -> z

module top_module(

input a,b,c,

output w,x,y,z );

assign w = a;

assign x = b, y = b;

assign z = c;

endmodule

Inverter(非门)

Create a module that implements a NOT gate.

module top_module( input in, output out );

assign out = ~in;

endmodule

Andgate(与门)

Create a module that implements an AND gate.

module top_module(

input a,

input b,

output out );

assign out = a & b;

endmodule

Norgate(或非)

或非门的坑!

要用! or

Create a module that implements a NOR gate. A NOR gate is an OR gate with its output inverted. A NOR function needs two operators when written in Verilog.

创建一个实现NOR门的模块。NOR门是输出倒置的或门。在Verilog中编写NOR函数时需要两个运算符。

module top_module(

input a,

input b,

output out );

assign out = ! (a | b);

endmodule

XNOR gate(同或)

Create a module that implements an XNOR gate.

module top_module(

input a,

input b,

output out );

assign out = a ~^ b;

endmodule

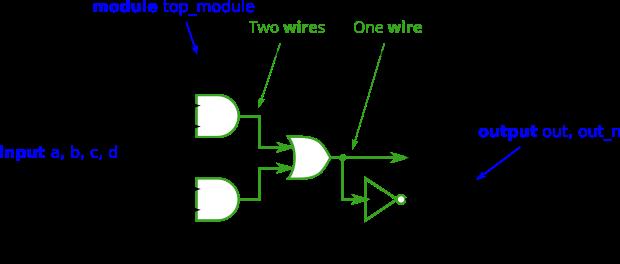

Declaring wires

`default_nettype none

module top_module(

input a,

input b,

input c,

input d,

output out,

output out_n );

wire a_b, c_d;

assign a_b = a & b; // 与

assign c_d = c & d;

assign out = a_b | c_d; // 或

assign out_n = !out; // 非

endmodule

选择器

Mux2to1(2选1)(1位)

Create a one-bit wide, 2-to-1 multiplexer. When sel=0, choose a. When sel=1, choose b.

module top_module(

input a, b, sel,

output out );

assign out = sel == 1 ? b : a;

endmodule

module top_module(a, b, sel,out);

input a, b;

input [3:0] sel;

output reg out;

// 有always 才有a b sel

always @(a, b, sel)

if (sel == 4'd1)

begin

out = b;

end

else

begin

out = a;

end

// assign out = sel == 1 ? b : a;

endmodule

Mux2to1v(100位)

Create a 100-bit wide, 2-to-1 multiplexer. When sel=0, choose a. When sel=1, choose b.

module top_module(

input [99:0] a, b,

input sel,

output [99:0] out );

assign out[99:0] = sel == 1 ? b[99:0] : a[99:0];

endmodule

Mux9to1v(9选1)

Create a 16-bit wide, 9-to-1 multiplexer. sel=0 chooses a, sel=1 chooses b, etc. For the unused cases (sel=9 to 15), set all output bits to '1'. // 后面这里说所有位都是1

module top_module(

input [15:0] a, b, c, d, e, f, g, h, i,

input [3:0] sel,

output [15:0] out );

always@(*)

begin

case (sel)

4'b0000: begin out = a; end

4'b0001: begin out = b; end

4'b0010: begin out = c; end

4'b0011: begin out = d; end

4'b0100: begin out = e; end

4'b0101: begin out = f; end

4'b0110: begin out = g; end

4'b0111: begin out = h; end

4'b1000: begin out = i; end

default begin out = 16'hffff; end

endcase

end

endmodule

Mux256to1

Create a 1-bit wide, 256-to-1 multiplexer. The 256 inputs are all packed into a single 256-bit input vector. sel=0 should select in[0], sel=1 selects bits in[1], sel=2 selects bits in[2], etc.

module top_module(

input [255:0] in,

input [7:0] sel,

output out );

assign out = in[sel];

endmodule

Mux256to1v

Create a 4-bit wide, 256-to-1 multiplexer. The 256 4-bit inputs are all packed into a single 1024-bit input vector. sel=0 should select bits in[3:0], sel=1 selects bits in[7:4], sel=2 selects bits in[11:8], etc

module top_module(

input [1023:0] in,

input [7:0] sel,

output [3:0] out );

// sel=1 selects bits in[7:4]

assign out = in[sel * 4 + 3], in[sel * 4 + 2], in[sel * 4 + 1], in[sel * 4];

endmodule

加法器

half_add半加器

Create a half adder. A half adder adds two bits (with no carry-in) and produces a sum and carry-out.

module top_module(

input a, b,

output cout, sum );

// cout 是 与

assign cout = a & b;

// sum 是异或

assign sum = a ^ b;

endmodule

full_add全加器

Create a full adder. A full adder adds three bits (including carry-in) and produces a sum and carry-out.

Sequential Logic

Shift Registers

Shift4

asynchronous是异步,synchronous是同步

Build a 4-bit shift register (right shift), with asynchronous reset, synchronous load, and enable.

areset: Resets shift register to zero.

load: Loads shift register with data[3:0] instead of shifting.

ena: Shift right (q[3] becomes zero, q[0] is shifted out and disappears).

q: The contents of the shift register.

If both the load and ena inputs are asserted (1), the load input has higher priority.

module top_module(

input clk,

input areset, // async active-high reset to zero

input load,

input ena,

input [3:0] data,

output reg [3:0] q);

always @ (posedge clk , posedge areset)

begin

if (areset)

q <= 4'd0;

else

begin

if (load)

q <= data;

else if (ena)

q <= q >> 1;

end

end

endmodule

Rotate100

Build a 100-bit left/right rotator, with synchronous load and left/right enable. A rotator shifts-in the shifted-out bit from the other end of the register, unlike a shifter that discards the shifted-out bit and shifts in a zero. If enabled, a rotator rotates the bits around and does not modify/discard them.

-

load: Loads shift register withdata[99:0]instead of rotating. -

-

ena[1:0]

- Chooses whether and which direction to rotate.

2'b01rotates right by one bit2'b10rotates left by one bit2'b00and2'b11do not rotate.

-

q: The contents of the rotator.

module top_module(

input clk,

input load,

input [1:0] ena,

input [99:0] data,

output reg [99:0] q);

always @(posedge clk)

begin

if (load)

q <= data;

else

begin

case (ena)

2'b01: q <= q[0], q[99:1]; // 右移

// 99 98 ... 1 0

2'b10: q <= q[98:0], q[99]; // 左移

default: q <= q;

endcase

end

end

endmodule

以上是关于verilog网站刷题记录的主要内容,如果未能解决你的问题,请参考以下文章