vscode环境玩转verilog设计仿真--比较器

Posted 海里的鱼2022

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了vscode环境玩转verilog设计仿真--比较器相关的知识,希望对你有一定的参考价值。

1. 环境配置参见前文

vscode完成verilog编辑仿真环境配置(带完整源码包)_海里的鱼2022的博客-CSDN博客_vscode配置verilog

本例的代码包下载:

https://download.csdn.net/download/pocean2012/85553267

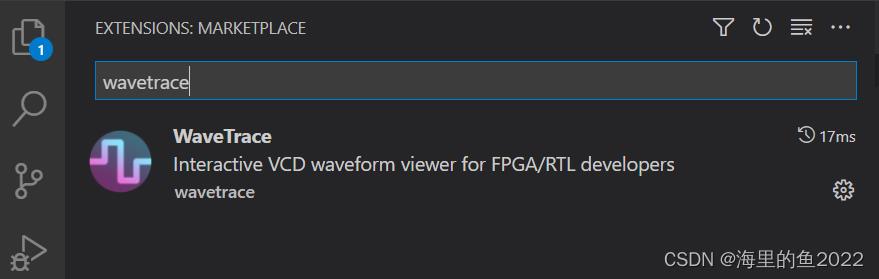

上篇文章里用的gtkwave查看波形,也很方便,但万能的vscode也是可以搞定这个小尾巴的, 所i再安装个wavetrace插件,就可以直接看VCD仿真波形了。

2. 开始最简单的比较器例子

电路原理:

在数字电路中,经常需要对两个位数相同的二进制数进行比较,以判断它们的相对大小

或者是否相等,用来实现这一功能的逻辑电路就成为数值比较器。

逻辑实现:

数值比较器就是对两数A、B进行比较,以判断其大小的逻辑电路。比较结果有A>B、

A<B以及A=B三种情况。

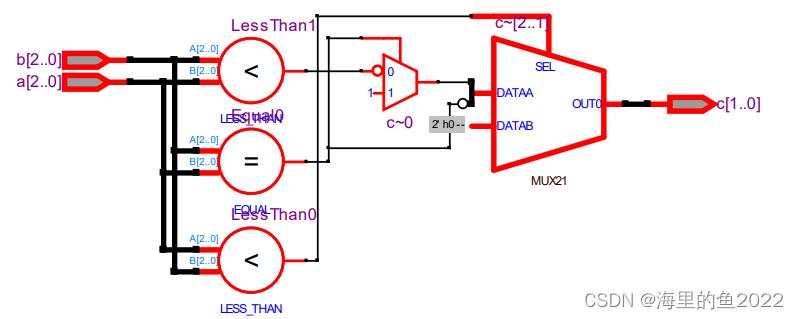

端口示意图:

在EDA工具里可以生成RTL示意图

不过,这都是老套路,我们今天的环境只需要vscode!

上代码,设计个三位比较器,在vscode里直接编辑保存comp.v文件:

module comp(a,b,c); //例化a,b,c

input [2:0]a,b; //输入两个三位二进制数a,b;相互比较

output reg [1:0] c; //比较后输出结果:一个两位二进制数c

always @ (a or b) //当a或b发生变化时,进入循环

begin //进入a,b的判断比较得到c

if(a<b)

begin

c<=2'b00; //如果a<b,c的值为00b

end

else if (a==b)

begin

c<=2'b01; //如果a=b,c的值为01b

end

else if (a>b)

begin

c<=2'b10; //如果a>b,c的值为10b

end

/* 异常情况 */

/* 不包含异常情况时,电路会多2个锁存器;包含异常情况时,则电路不会多出2个锁存器 */

// //------------------------------------------------

// else

//

// begin

// c<=2'b11; //出现异常情况,c的值为11b;且不会出现其他情况

// end

// //------------------------------------------------

end

endmodule

注意, 多位数据比较器与三位数据比较器类似,需要注意的是如果使用 if...else,需要设置条件

完全,否则也会产生锁存器。此方式为行为描述方式,如果多位数据比较器位数过多,会造

成程序繁琐,此时可以使用门级结构描述方式(使用 and,or,not 等语句实现,如 and(c,

a,b);即直接将 a,b 相与后的值赋给 c)、或是数据流描述方式(使用 assign 直接定义描

述,如 assign c=(a>b)?1:0;即直接判断 a 是否大于 b,如果为真,c 为 1,如果为假,c 为 0)、

又或是行为描述方式中使用 case 语句选择。

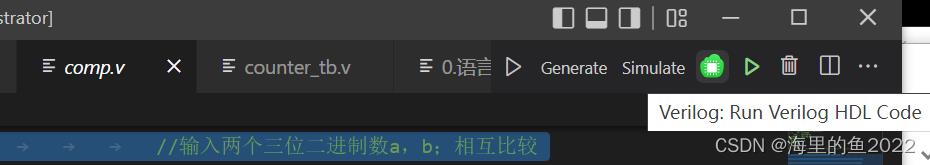

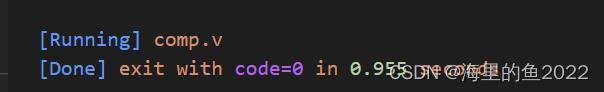

2. 按运行可以检查代码错误

无错误,会出现运行提示(是不是和C代码运行有点像)

3. 生成testbench框架

ctrl+shift+p打开运行菜单

选择testbench

可以看出调用的python脚本运行,得到testbench框架

python c:\\Users\\xxxx\\.vscode\\extensions\\truecrab.verilog-testbench-instance-0.0.5\\out\\vTbgenerator.py d:\\FPGA-DEV\\Verilog-study\\_1_comp\\comp.v

//~ `New testbench

`timescale 1ns / 1ps

module tb_comp;

// comp Parameters

parameter PERIOD = 10;

// comp Inputs

reg [2:0] a = 0 ;

reg [2:0] b = 0 ;

// comp Outputs

wire [1:0] c ;

initial

begin

forever #(PERIOD/2) clk=~clk;

end

initial

begin

#(PERIOD*2) rst_n = 1;

end

comp u_comp (

.a ( a [2:0] ),

.b ( b [2:0] ),

.c ( c [1:0] )

);

initial

begin

$finish;

end

endmodule向量激励还是要自己写,另外本例没有clk和rst,所以要删掉,另外时钟间隙要改一下,否则仿真波形文件太大了,把硬盘都占满了(无限硬盘空间的老友掠过)。

由此,得到最后编写的tb文件:

//~ `New testbench

`timescale 1ns / 1ns

module tb_comp;

// comp Parameters

parameter PERIOD = 10;

// comp Inputs

reg [2:0] a = 0 ;

reg [2:0] b = 0 ;

// comp Outputs

wire [1:0] c ; // 比较器输出结果

integer i,j;

comp u_comp (

.a ( a [2:0] ),

.b ( b [2:0] ),

.c ( c [1:0] )

);

initial

begin

a=0;b=0;

while(1)

begin

for(i=1;i<8;i=i+1)

#10 a=i;

end

end

initial

begin

for(j=1;j<8;j=j+1)

#10 b=j;

end

initial

begin

$monitor($time,,,"%d comp %d = %b",a,b,c);

#200 $finish;

end

initial

begin

$dumpfile("comp_tb.vcd"); //生成的vcd文件名称

$dumpvars(0, tb_comp); //tb模块名称

end

endmodule就是a循环变化,b只变化一轮,然后观察输出c的值(也可以自己另外设计)

4. 编译, 仿真,生成波形

注意要在工作目录下运行

编译

iverilog -o comp_1.vpp comp.v comp_tb_1.v

执行仿真,可以观察到打印输出

vvp comp_1.vpp

VCD info: dumpfile comp_tb.vcd opened for output.

0 0 comp 0 = 01

10 1 comp 1 = 01

20 2 comp 2 = 01

30 3 comp 3 = 01

40 4 comp 4 = 01

50 5 comp 5 = 01

60 6 comp 6 = 01

70 7 comp 7 = 01

80 1 comp 7 = 00

90 2 comp 7 = 00

100 3 comp 7 = 00

110 4 comp 7 = 00

120 5 comp 7 = 00

130 6 comp 7 = 00

140 7 comp 7 = 01

150 1 comp 7 = 00

160 2 comp 7 = 00

170 3 comp 7 = 00

180 4 comp 7 = 00

190 5 comp 7 = 00

comp_tb_1.v:48: $finish called at 200 (1ns)

200 6 comp 7 = 00

因为我们在testbench文件中指定了仿真波形输出到指定文件

$dumpfile("comp_tb.vcd"); //生成的vcd文件名称

目录下会生成上述波形文件

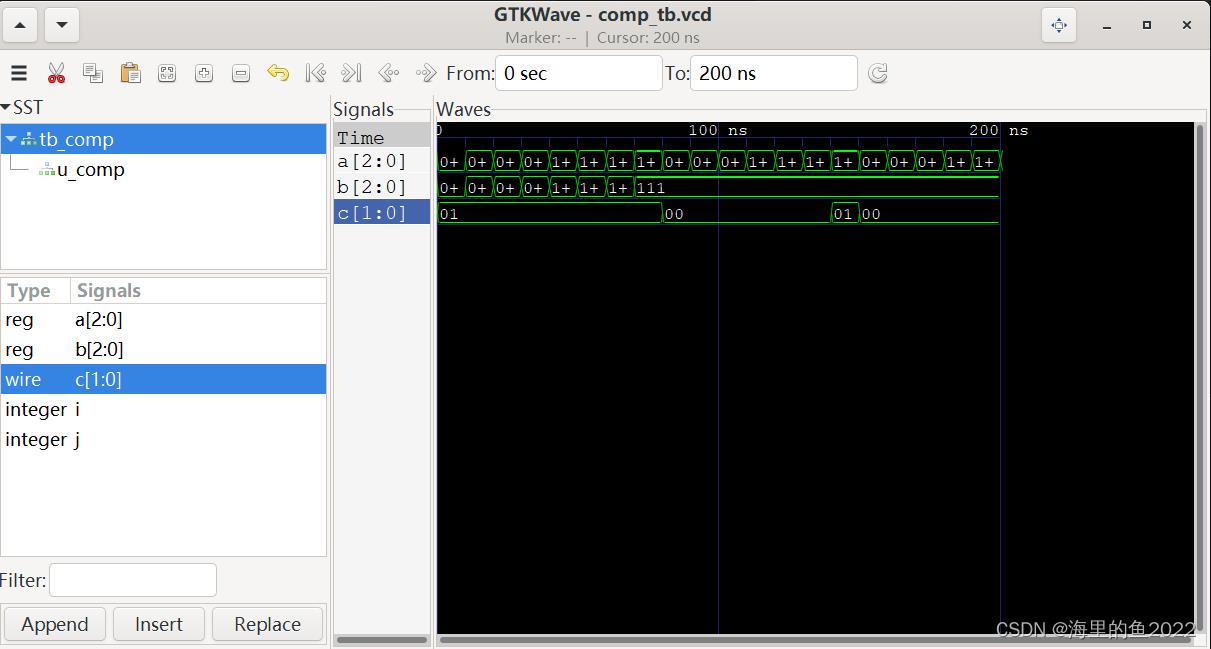

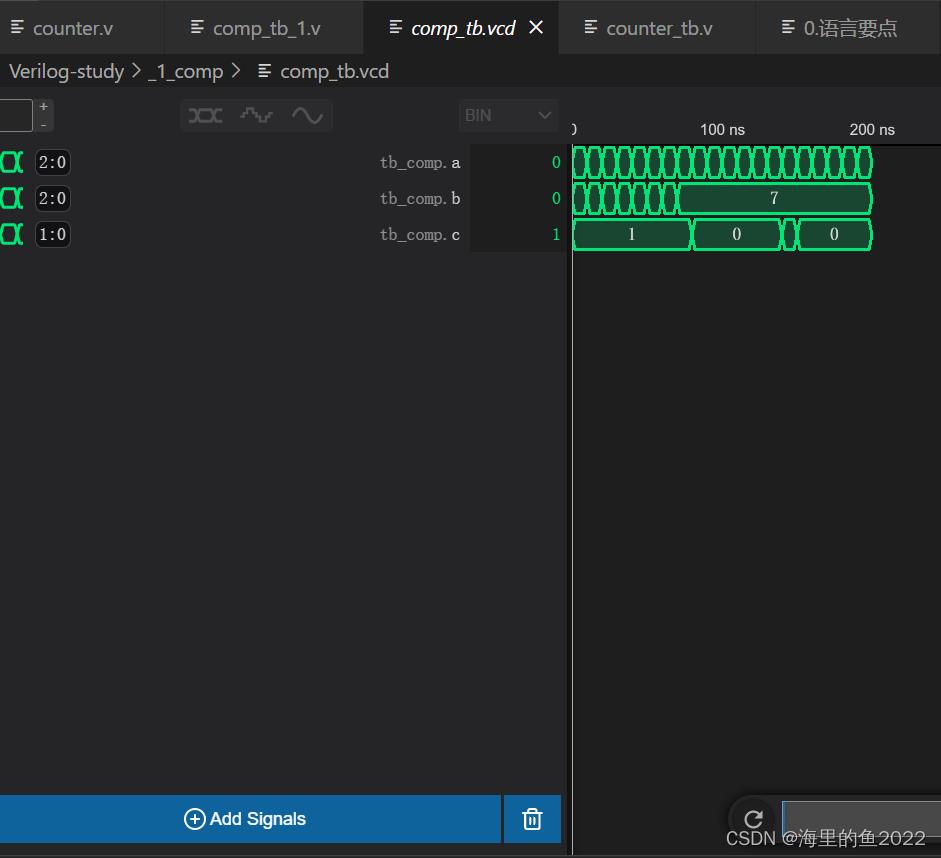

5. VCD文件可以用gtkwave打开,或者直接用插件打开观察

gtkwave comp_tb.vcd

vscode里直接点选vcd文件,就会调用插件打开

页面也是相当的nice。

OK, 小伙伴们可以不用安装任何EDA工具,就可以在vscode里愉快的玩耍verilog了,爽。

以上是关于vscode环境玩转verilog设计仿真--比较器的主要内容,如果未能解决你的问题,请参考以下文章