4*4空分时分矩阵基于fpga的4*4空分,时分矩阵操作处理的verilog设计

Posted fpga&matlab

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了4*4空分时分矩阵基于fpga的4*4空分,时分矩阵操作处理的verilog设计相关的知识,希望对你有一定的参考价值。

1.软件版本

quartusii12.1

2.本算法理论知识

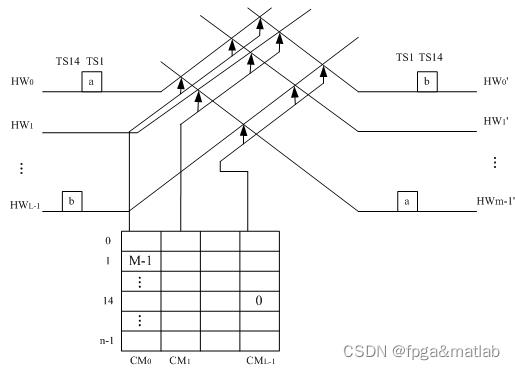

空分交换是指利用空分交换矩阵对同一类型的信号的一组信号进行交叉连接,在连接过程中不对信号进行处理,只对信号通路进行交叉连接,因此可以保证信号做到无损连接。它主要由电子交叉点矩阵及控制存储器(CM)组成。按其中控制存储器对交叉点的控制方式可分为输入控制方式与输出控制方式两种。

1.输入控制方式

图1为输入控制方式S交换的原理图。图中所示为LXM的交叉点矩阵,即有L条入线,M条出线。每条输入输出线上有n个时隙。对应每一条输入线有一个控制存储器,所以共有L个控制存储器(CM0-CML-1)。由这些控制存储器决定该输入线上各时隙中的信号经过哪一个交叉点要交换到哪一条输出线的相应时隙中去。

在图中,输入HW0的TS1时隙中的信号“a”要交换到输出HWm-1’的TS1时隙时,处理机在CM0的第一号单元中写入“M-1",即CM的单元号与时隙号相对应,CM的单元中写入的内容是输出线的线路号。之后在每帧的TS1时间内,CM0控制交叉点“0 (M-1)”

以上是关于4*4空分时分矩阵基于fpga的4*4空分,时分矩阵操作处理的verilog设计的主要内容,如果未能解决你的问题,请参考以下文章