PCIe+Switch高速存储方案设计

Posted HeroKern

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了PCIe+Switch高速存储方案设计相关的知识,希望对你有一定的参考价值。

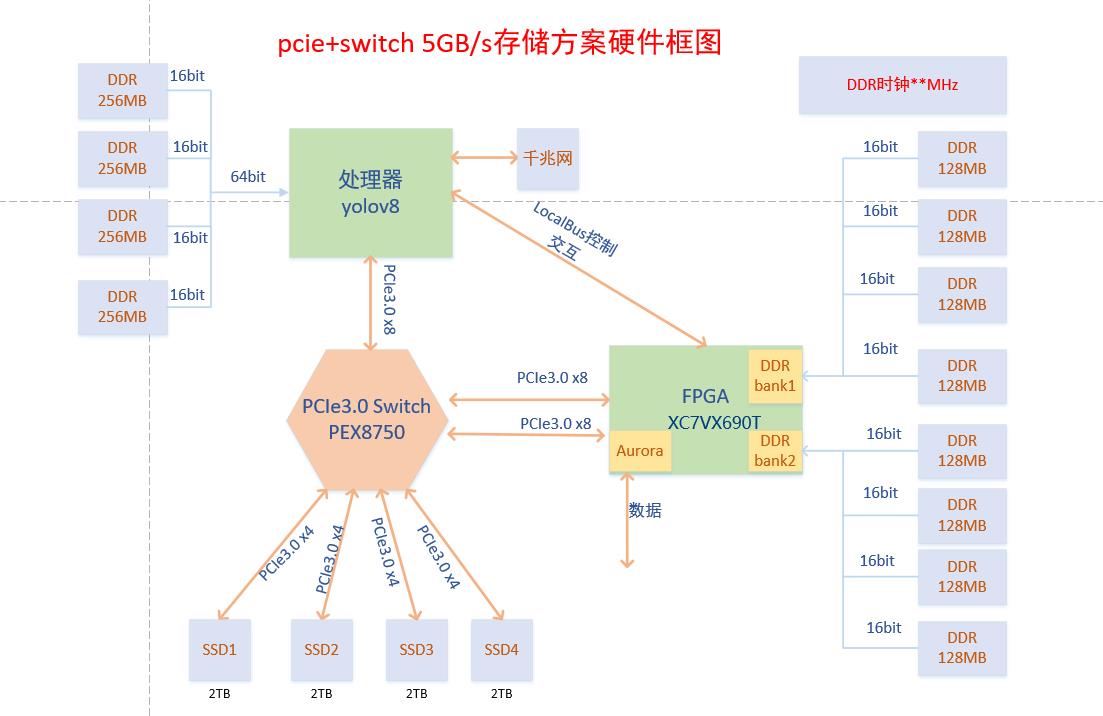

上篇文章分享了《zynq高速存储方案》,zynq存储方案实现了1.2GB/s的存储速率,这篇文章分享pcie+switch常规方案,这种方案在存储领域很常见,目前作者实现switch方案存储速度有5GB/s和6.5GB/s,以及没有国产化要求并且不使用switch方案储存速率5GB/s。具体速度多少根实际的SSD盘数和switch选择都有很大关系,高速存储在设计存储方案时会有很多考虑,比如是否全国产化,速度指标,SSD盘容量,数据是否需要备份,硬件成本,开发难度系数等诸多因素,只有结合实际项目的需求才能设计出性价比高的方案。下面分享5GB/s一种国产化方案的设计,硬件框图如下图所示。

上面框图中处理器选型这里根据具体项目需求,如果没得国产化需求推荐选择zynq zu系列芯片,处理器DDR选择一般32bit就够了,switch存储方案对处理器DDR要求不高,满足基本软件运行就行,对switch选择看是否是透明桥,pcie lane数量和最大带宽,端口数量,是否支持P2P模式,是否支持超车功能等。对于FPGA选择只要确定高速接口数量满足,资源满足,PCIe硬核满足,以及DDR带宽满足。对于SSD数量选择需要根据项目需求的具体带宽。

上面框图中处理器选型这里根据具体项目需求,如果没得国产化需求推荐选择zynq zu系列芯片,处理器DDR选择一般32bit就够了,switch存储方案对处理器DDR要求不高,满足基本软件运行就行,对switch选择看是否是透明桥,pcie lane数量和最大带宽,端口数量,是否支持P2P模式,是否支持超车功能等。对于FPGA选择只要确定高速接口数量满足,资源满足,PCIe硬核满足,以及DDR带宽满足。对于SSD数量选择需要根据项目需求的具体带宽。

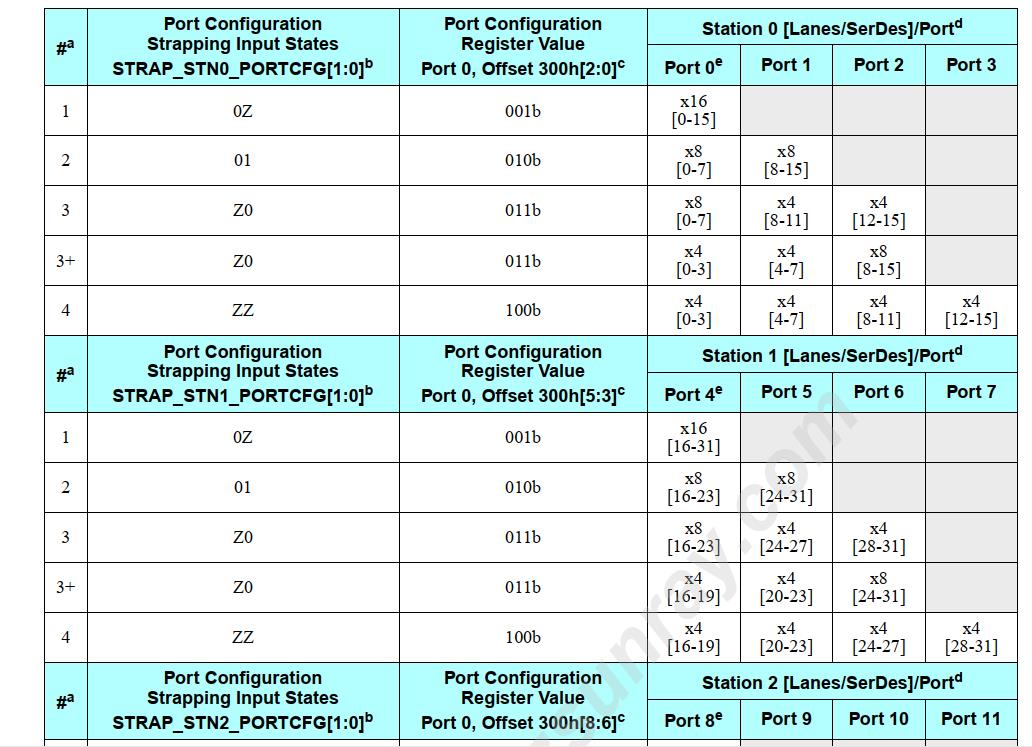

软件处理方式根zynq高速存储思路基本一致,只是增加了对switch通道的选择,这里需要阅读手册,如果端口分错误,轻则速度性能受损,重则数据链路直接不同,这里对switch的硬件配置很重要,具体配置可以参考下图表格。

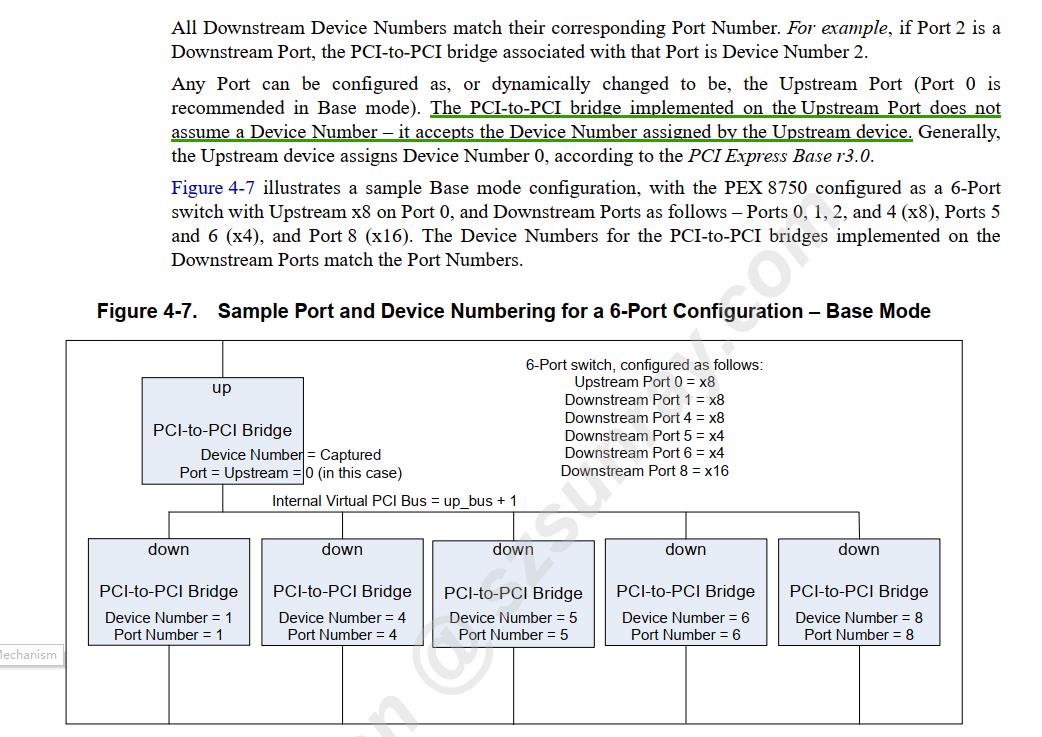

软件整体方案思路就是将FPGA内的数据通过Switch直接下盘,或者SSD盘中的数据直接卸载到FPGA的高速接口上,处理器上的软件用于实现PCIe驱动,NVME驱动,Raid0驱动,文件系统,以及应用程序。PCIe驱动用于初始化Host,枚举PCIe树(枚举总线部分规则如下图所示),分配总线,BAR空间等,NVME驱动用于实现与SSD控制器数据交互,raid0驱动实现将多张SSD盘虚拟成一张盘,自定义驱动是整个项目的枢纽,将完成NVME驱动,Raid0驱动以及FPGA和SSD之间交互的耦合工作。

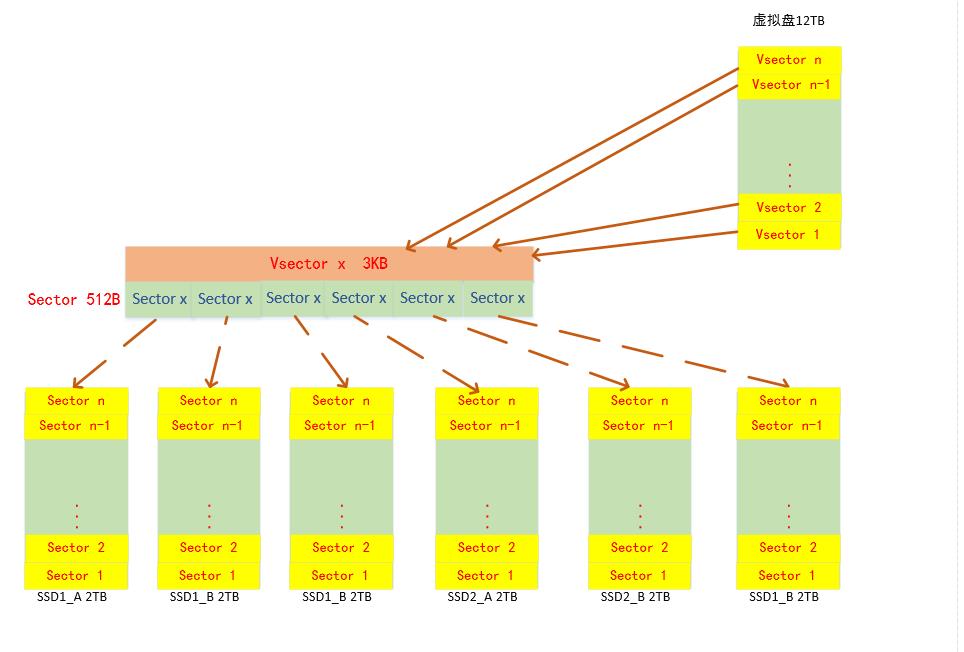

Raid0驱动负责将多张SSD盘结合虚拟成一张盘处理,嵌入式应用程序看到的只是一张磁盘,只是访问扇区最小单位变大,如果项目磁盘数量变了,应用程序还是可以通用,只需要更换驱动程序,如果驱动做的做够好,完全可以自适应盘的数量实现raid0,应用程序通过查询ssd盘的数量确定虚拟盘的扇区最小访问单位,如果不能自适应盘的数量,也可以通过配置项确定ssd盘的数量,容量大小,支持的队列深度,NVME block大小等可变参数。Raid0实现框图如下图所示。

目前作者以及完成1GB/s,5GB/s,6.5GB/s三种速率的存储方案,速度不超过5GB/s的项目就不建议用该方案,可以尝试多host方案,实现的switch方案硬件如下图所示。

该存储方案实现了自定义文件系统,通过linux平台网络卸载速率高达90MB/s,支持nfs卸载文件。下篇文章分享多host存储方案。

以上是关于PCIe+Switch高速存储方案设计的主要内容,如果未能解决你的问题,请参考以下文章