quartus中怎么把自己编的程序生成一个模块符号?

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了quartus中怎么把自己编的程序生成一个模块符号?相关的知识,希望对你有一定的参考价值。

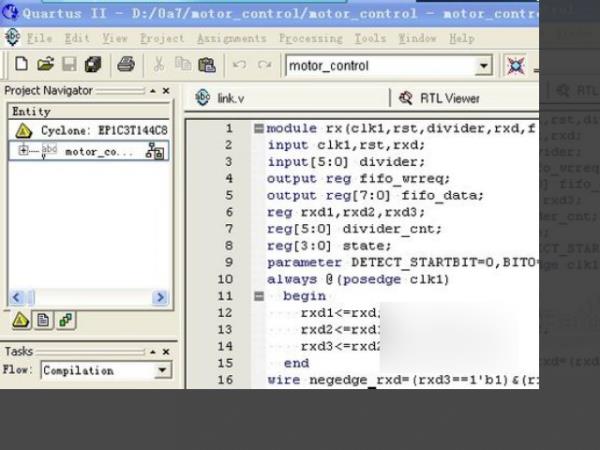

1、执行菜单【File】-【Open Project…】命令,在quartus中打开一个设计项目。

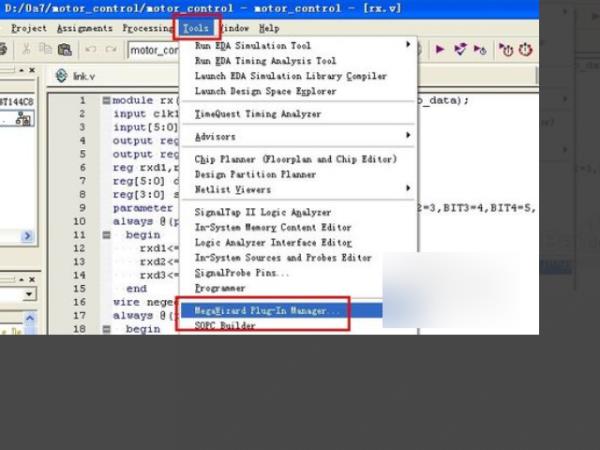

2、执行菜单【Tools】-【Megawizard Plug-In Manager…】命令,打开Megawizard Plug-In Manager设置向导。

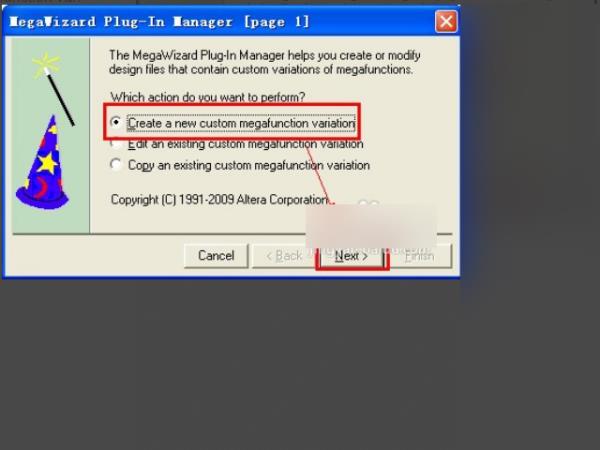

3、这里我们是添加一个全新的宏模块,所以选择【Creat a new custom megafunction variation】,点击【next】按钮。

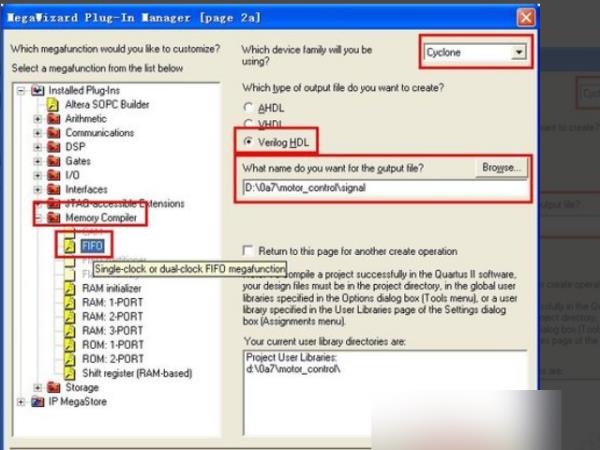

4、右上方会显示你所用的芯片系列,在左侧树形列表里选择你需要的宏模块,这里选择【Memory Compiler】-【FIFO】先进先出模块,选择所要生成的语言和FIFO模块的存储路径及文件名,点击【next】按钮。

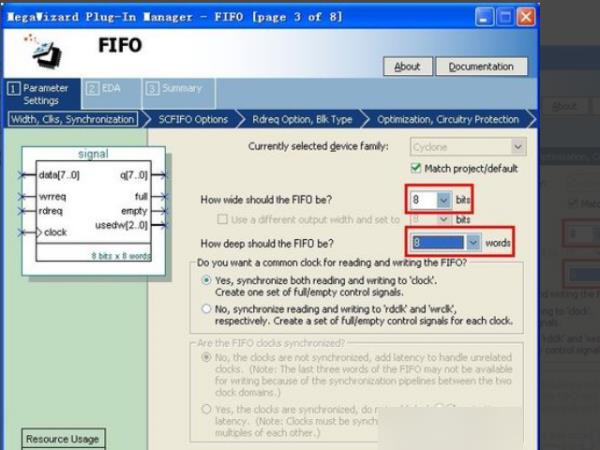

5、How wide should the FIFO be?后填写你建立的FIFO位宽多少,How deep should the fifo be?后填写你的FIFO深度,也就是能装多少个数据,下一步【next】。

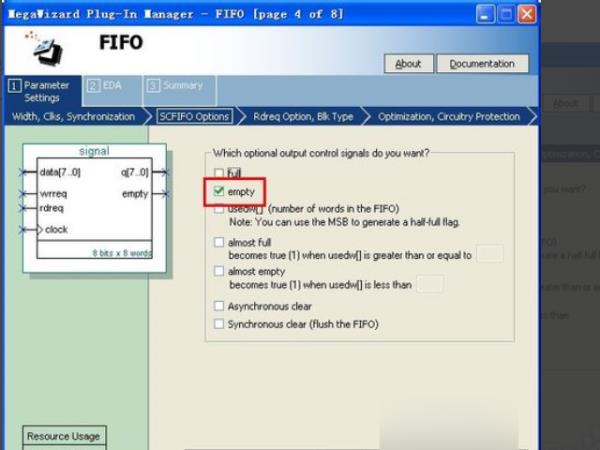

6、FIFO输出我们只选择数据q[#:0]和empty就可以了,所以去掉empty以为所有项目前的对勾,下一步【next】。

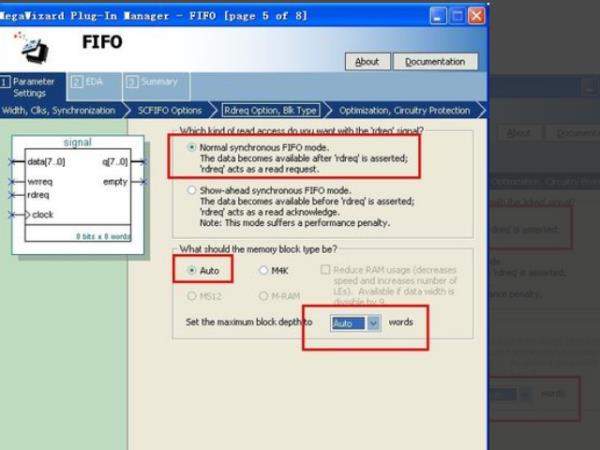

7、这一步可以默认设置不变,下一步【next】。

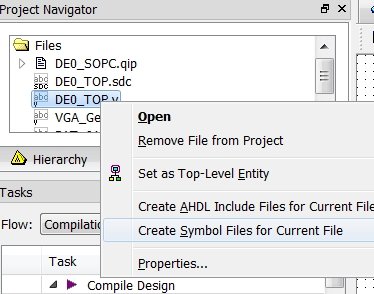

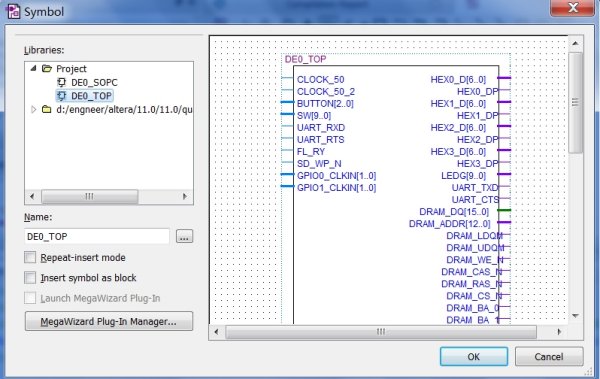

然后新建原理图文件,双击原理图的空白处,就有了

用 quartus ii 如何综合生成网表文件

需要quartus II 和Modelsim来后仿真,要.v格式的网表文件,现在有Error:Gate Level Simulation Netlist not found--run EDA Netlist writer to generate Gate Level Simulation Netlist ,求解啊,顺便告诉我后仿真怎么做

是Modelsim--altera

以上是关于quartus中怎么把自己编的程序生成一个模块符号?的主要内容,如果未能解决你的问题,请参考以下文章

关于怎么将Quartus和Nios程序一起固化到FPGA里面

Quartus II 里面,MegaWizard字体过小,根本看不清。如何调整?