P0-logisim简单部件与有限状态机

Posted buaa-wander

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了P0-logisim简单部件与有限状态机相关的知识,希望对你有一定的参考价值。

前言:众所周知,北航计算机学院大二的第一块难啃的硬骨头就是计算机组成课程设计,它的难度来源于以下几个方面(根据个人体会逐步更新中,各位看官请实时关注):一是课程开始之前需要自己通过cscore网站自学logisim,verilog以及mips汇编语言这三样工具,如果在预习期间没有合理安排好任务(比如我沉迷于数学竞赛+国庆活动+国庆封网站),那么很有可能无法按时完成预习部分的教程,然后在第六周的pre考试中炸裂。二是……to be continued

本人情况:由于上面所说的因素,在封网站之前只写了logisim的教程,另外两部分完全没看。虽然任务没有分配好,并且遇到了封cscore网站长达半个月这种70年一遇的操作,但是凭借自己国庆5天的啃课本+刷另一个网站(学习verilog用,移步 hdlbits.01xz.net)+暑假足量coding的基础,在10月8号网站解封之后三天时间几乎刷完了verilog以及mips部分(代价很大,三天总共睡了十二三小时)。以上突击仅属个例,仍然希望大家前期就把任务分配好并且按时完成,国庆有机会的话就重刷一些教程保持手感,那么相信大家的pre考试会体验感比较好,前两三个project到时候也能比较有底,那么就有时间学数学竞赛了(滑稽一波)。

///////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////////

下面开始本文的正题:P0课下测试+课上测试经验心得记录与分享(课上还没开始,请各位看官实时关注):

P0课下测试部分的题目是CRC校检,4-bit ALU,GRF,正则表达式匹配。

CRC校检:

这个题比较简单,在这个题之前有一节讲解搭建CRC校检电路的教程,该教程的意义不只是告诉我们CRC咋搞,它更重要的意义在于:告诉我们设计出符合题目要求电路的基本步骤:找输入输出(有哪些?多少位?)、分析输入与输出的关系(暴力真值表 or 找到计算规律,比如模2除法)、分块搭建(和程序设计里写函数并调用类似),测试(平凡数据、极限数据、非法数据、搭测试电路自动化测试)。注意,电路是解决问题的一种工具,而不是解决问题的方案,通俗一点来说就是给你一把枪并不代表你能打中人。所以,在搭建电路之前,一定要把问题的模型抽象出来,算法想清楚(最好写一下),这样就相当于保证了你掌握了射击技术,这时拿到枪,才有更高的概率打中人。

经验教训:在看CRC前面的教程的时候,以为只能是8位数,所以在模2除法之前没有对8位的原数据帧进行补0操作,导致错误(题目其实已经提示要补成11位了但我只是认为只要结果是11位就好);模2除法开始没有看懂余数的生成规则。

正则表达式匹配:

吸取了CRC的经验,先认真读了题,了解了正则表达式的生成规则,以及检验规则:在输入到某一个字符x的时候,发现从这个字符前面的某个字符y开始,一直到x所组成的字符串如果符合要求,就输出1。本题要求同步复位,是一个容易错的地方:一是可能会忘记按同步复位连,二是即使想同步复位但连错了。我属于后者。不知为什么我这个题用到了15个状态,要不是有analyse circuit我就死了

经验教训:1.有限状态机搭建关键操作:

只有状态存储电路中有寄存器,也就是说,在搭建状态转移电路时,可以使用analyse circuit,注意先把输入数据全部用spliter分开 (这条纯属废话,只是提醒我这个好久没搭建过状态机的人)

填写真值表的时候,操作规模主要取决于输入的个数,如果输入为n个,输出为m个,则需要操作的次数为m*2^n,所以一般不超过7个输入都可以接受,不要太害怕

状态少可以用独热编码,状态多就必然得用二进制编码或者其他更优秀的编码

看清楚是搭建Moore型还是Mealy型状态机,这两种状态机的输出不同,Mealy型状态机设计输出的时候需要传递寄存器保存的状态以及当前输入

如果在搭建完毕状态转移电路之后发现自己类型搭建错误了,不要着急,这两种类型的状态机的状态转移部分基本是一样的,所以可能不需要修改状态转移电路

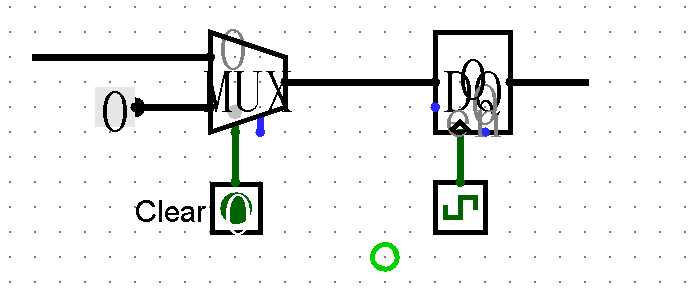

有限状态机中的同步复位:一种实现方法:二选一多路选择器法。利用复位信号reset选择是输出算出的状态(即状态转移电路刚算出来的那部分)还是初始置零状态。

看图便于理解:

(某巨佬的图)

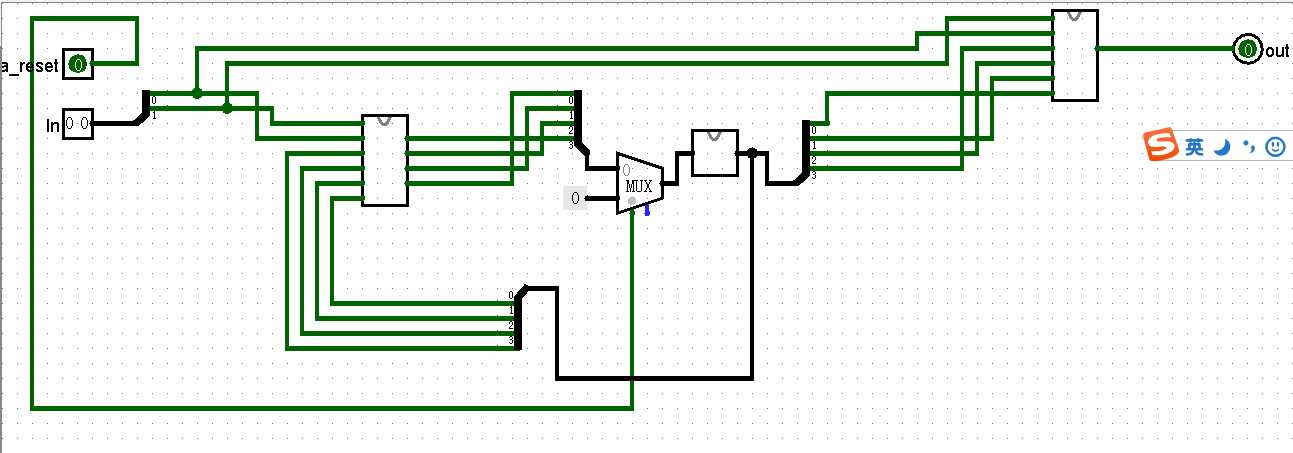

下面是我对于该同步复位方法的应用(看中间)

Warning:错误的“同步复位”:首先如果仅仅将CLR与寄存器的reset相连肯定不能实现同步的操作,比如在时钟处于某个电平时,如果CLR置1,那寄存器状态会立马改变,不能按照题目要求的在时钟上升沿才实现复位操作。 其次,如果上面直接连reset行不通,很容易想到直接在CLR后面加一个寄存器,然后同步清除状态寄存器的值,但是这个方法也有问题,虽然在CLR为1时复位寄存器没有问题,但是由于CLR置0之后需要一个上升沿才能到reset,这个上升沿状态寄存器是不能存储状态的,所以后面要延迟了一个周期,所以这种方法也不是同步的,这样的话输出就有可能出错。

2.模块外观的重要性:模块和要求的有一点不一样,就会running time error输出xxxxx。看测试电路是怎么连接的,别输入的顺序连接反了,不然也是running time error

以上是关于P0-logisim简单部件与有限状态机的主要内容,如果未能解决你的问题,请参考以下文章