DDR2学习之SRAM,SDRAM,DDR,DDR2的区别

Posted gallion8689

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了DDR2学习之SRAM,SDRAM,DDR,DDR2的区别相关的知识,希望对你有一定的参考价值。

第一次写博客,写博客的目的是为了将自己的学习过程记录下来,方便自己今后进行复习。最近在做一个视频采集压缩系统,现在正学习到了DDR2的配置,等系统调出来会将之前的部分记录下来。废话不多说,正文开始。

SRAM:异步静态随机存储器,一个SRAM单元由4-6个CMOS晶体管组成,数据只有在新的数据来或者断电才会丢失,单片SRAM芯片容量低,价格昂贵。SRAM不需要刷新,速度可以非常快,现在基本可以和CPU主频同速,其工作时不需要外部提供时钟。

SDRAM:同步动态随机存储器,SDRAM使用电荷存储数据,功耗较SRAM低,需要不断的进行数据的刷新来保证数据不丢失,SDRAM最多可以做到64M字节,突发长度支持1,2,4,8,page。

DDR,DDR2是双速率同步动态随机存储器,是更快速率的SDRAM,在内存时钟的上升沿和下降沿都可以进行数据的传输。

DDR:封装为TSOPII,电压等级为SSTL_25(2.5V),速度可以达到400Mbit/s,内部有2bit预读结构,突发长度支持2,4,8。

DDR2:封装为FBGA,电压等级为SSTL_18(1.8V),速度可以达到1066Mbit/s,内部有4bit预读结构,突发长度支持4,8。DDR2较DDR引入了OCD, ODT, POST线

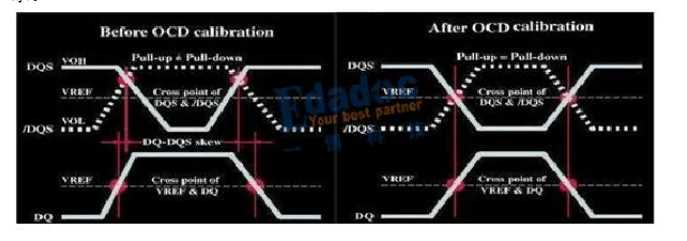

OCD:(off chip driver)离线驱动调整,OCD的主要作用在于调整IO接口端的电压来补偿上拉与下拉电阻,从而调整DQS与DQ之间的同步,确保信号的完整和可靠性。调校期间,分别测试DQS高电平和DQ高电平,以及DQS低电平和DQ低电平的同步情况,如果不满足要求,则通过设定突发长度的地址线来传送上拉或者下拉电阻的等级(加一档或者减一档),直到测试合格才退出OCD操作。具体过程如图所示

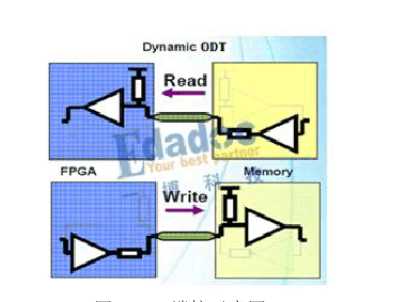

ODC:(on die termination)片内终结,DDR主板上面为了防止数据线终端反射信号需要大量的终结电阻,大大增加了主板的制造成本,终结电阻的大小决定了数据线的信号比和反射率,终结电阻小则数据线信号反射低但是信噪比也比较低;终结电阻大,数据线的信噪比高,但是信号反射也会增加,因而主板上的终结电阻并并不能很好的匹配内存模组,还会在一定程度上影响信号的品质。DDR2可以根据自己的特点内建合适的终结电阻,当DRAM模组工作时把终结电阻关掉,对于不工作的DRAM模组进行终结操作,这样可以保证最佳的信号波形,不仅降低了成本而且得到了最佳的信号品质。

posted CAS:他是为了结局DDR内存中指令冲突问题,提高DDR2内存利用效率而设计的,其功能优势只有在那些读写非常频繁的运作环境才能体现。

以上是关于DDR2学习之SRAM,SDRAM,DDR,DDR2的区别的主要内容,如果未能解决你的问题,请参考以下文章

s3c2440中为啥sdram一定要安装在bank6-7这两个bank上,我可以安装在别的bank上面吗?

小梅哥FPGA进阶学习之旅基于Altera FPGA 的DDR2+千兆以太网电路设计

采用激励driver模块IP核模拟DDR2控制器的用户侧,来调度DDR2控制器。 请问你的激励driver模块IP核是哪里来