刚在咸鱼买了块开发板,比较老了14年的,SOC为imx6solo,内核3.10,uboot2009的,准备先移植一个较新的uboot

到nxp的git下获取他们维护的uboot,网址http://git.freescale.com/git/cgit.cgi/imx/uboot-imx.git

选择imx_v2016.03_4.1.15_2.0_ga的brance,git太慢了,直接下载rel_imx_4.1.15_1.2.0_ga.tar.bz2源码包。

到Makefile中更改CROSS_COMPILE

make riotboard_defconfig

make -j8

出现

riotboard/rel_imx_4.1.15_1.2.0_ga/arch/arm/imx-common/cpu.c:199: undefined reference to `uclass_get_device‘

查看配置文件是没定义CONFIG_DM相关的就是驱动模型,因为这个板子uboot是维护的,所以就换了个版本

仓库地址https://gitlab.denx.de/u-boot/u-boot/tree/v2016.09

这次顺利通过编译,下载到tf卡上启动没有反应,串口无输出。中间反复检查了很多方面,到最终成功启动有两个问题

1.烧写命令dd iflag=dsync oflag=dsync if=u-boot.imx of=/dev/sdb seek=2

seek=blocks:从输出文件开头跳过blocks个块后再开始复制

uboot.imx = ivt + dcd + uboot.bin

imx的soc通过sd启动时,u-boot.imx要有一个0x400的offset,也就是1024字节,sd卡一个扇区512byte,所以跳过2个扇区,从第三个扇区烧写

开始时没搞清seek的定义,一直用的seek=3....

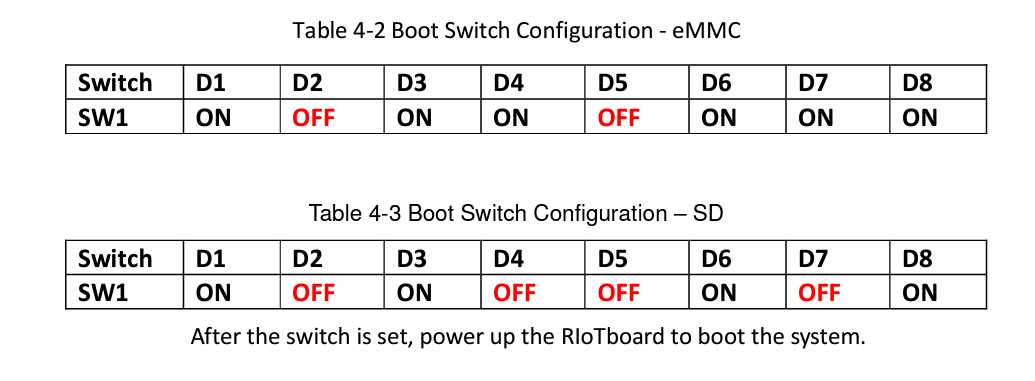

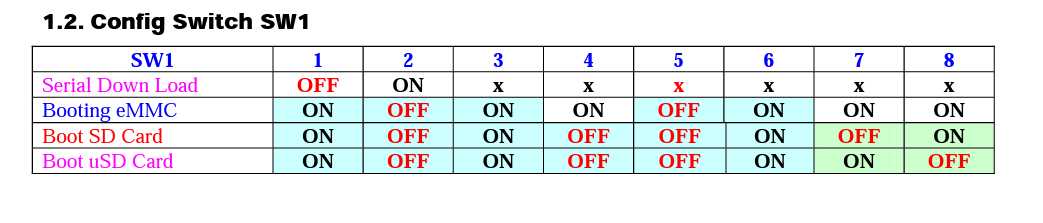

2.拨码开关

使用手册的截图

重点来了,这个是背后的SD大卡的启动选项。。。。

发现这点是在网上搜到的一个pdf

调整后顺利启动

调老板子运气真的挺重要的,这个开发板国内资料真的没多少,而且都是3.x的。

还有个小细节,上面说的u-boot.imx是通过uboot自带的工具./tool/imximage实现的在正常的uboot.bin前加上必要的数据(例如内存初始化等),其中的数据想DCD等都是保存在/board/xxx/xxx.cfg 里的,但是这块开发板下没有 .cfg,而在/configs/riotboard_defconfig中指定了CONFIG_SYS_EXTRA_OPTIONS="IMX_CONFIG=board/boundary/nitrogen6x/nitrogen6s1g.cfg,MX6S,DDR_MB=1024,ENV_IS_IN_MMC"

即nitrogen6s的板子,查看发现其中一句 BOOT_FROM spi ,修改为sd。后来测试即使是spi也可以正常启动,没有深入研究。

最终uboot还是用的rel_imx_4.1.15_2.0.0_ga,就是nxp git下的,make riotboard_defconfig 出现找不到ldo_mode_set这个函数的定义,

因为在board/embest/mx6boards/mx6boards.c中没有实现,在bug信息的xxx/cpu.c中有如下代码

#if defined(CONFIG_LDO_BYPASS_CHECK)

ldo_mode_set(check_ldo_bypass());

#endif

于是在include/configs/embestmx6boards.h 最后 #undef CONFIG_LDO_BYPASS_CHECK

编译通过。

启动后ping不通:

Using FEC device

ARP Retry count exceeded; starting again

ping failed; host 192.168.0.12 is not alive

试了网上说的增加TIMEOUT的值,试了也没有效果。后来参考embest维护的3.x的uboot

注释掉board/embest/mx6boards/mx6boards.c中

#if 1

int mx6_rgmii_rework(struct phy_device *phydev)

{

/* from linux/arch/arm/mach-imx/mach-imx6q.c :

* Ar803x phy SmartEEE feature cause link status generates glitch,

* which cause ethernet link down/up issue, so disable SmartEEE

*/

phy_write(phydev, MDIO_DEVAD_NONE, 0xd, 0x7);

phy_write(phydev, MDIO_DEVAD_NONE, 0xe, 0x805d);

phy_write(phydev, MDIO_DEVAD_NONE, 0xd, 0x4003);

return 0;

}

#endif

添加

int mx6_rgmii_rework(struct phy_device *phydev)

{

unsigned short val;

/* To enable AR8031 ouput a 125MHz clk from CLK_25M */

phy_write(phydev, MDIO_DEVAD_NONE, 0xd, 0x7);

phy_write(phydev, MDIO_DEVAD_NONE, 0xe, 0x8016);

phy_write(phydev, MDIO_DEVAD_NONE, 0xd, 0x4007);

val = phy_read(phydev, MDIO_DEVAD_NONE, 0xe);

val &= 0xffe3;

val |= 0x18;

phy_write(phydev, MDIO_DEVAD_NONE, 0xe, val);

/* introduce tx clock delay */

phy_write(phydev, MDIO_DEVAD_NONE, 0x1d, 0x5);

val = phy_read(phydev, MDIO_DEVAD_NONE, 0x1e);

val |= 0x0100;

phy_write(phydev, MDIO_DEVAD_NONE, 0x1e, val);

return 0;