mos工艺中工艺角(tt ff ss)都是代表啥

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了mos工艺中工艺角(tt ff ss)都是代表啥相关的知识,希望对你有一定的参考价值。

希望能够详细点,先谢啦

Finish-to-Start (TT),把这个任务的开始日期和前提条件任务的结束日期对齐,一般用于串行的任务安排,前一个任务必须完成后才能启动下一个新任务。

Start-to-Start (SS),把这个任务的开始日期和前提条件任务的开始日期对齐,一般用于并行任务的安排,也可以一个任务启动后,第二个任务延后或提前数日启动。

Finish-to-Finish (FF),把这个任务的结束日期和前提条件任务的结束日期对齐,可以用于协调任务的统一时间完成,这样可以定义好任务的开始时间

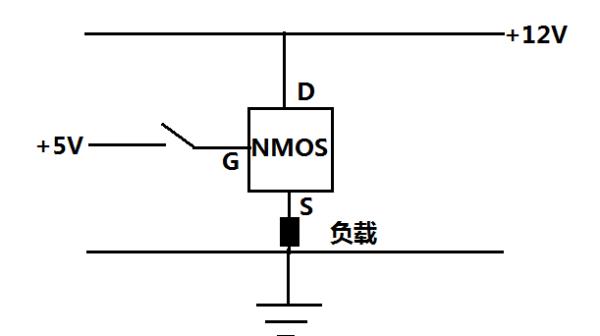

NMOS的结构如下:在一块掺杂浓度较低的P型硅衬底上,制作两个高掺杂浓度的N+区,并用金属铝引出两个电极,分别作漏极d和源极s。

然后在半导体表面覆盖一层很薄的二氧化硅(SiO2)绝缘层,在漏——源极间的绝缘层上再装上一个铝电极,作为栅极g。在衬底上也引出一个电极B,这就构成了一个N沟道增强型MOS管。

扩展资料:

当vGS数值较小,吸引电子的能力不强时,漏——源极之间仍无导电沟道出现,如图1(b)所示。vGS增加时,吸引到P衬底表面层的电子就增多,当vGS达到某一数值时,这些电子在栅极附近的P衬底表面便形成一个N型薄层。

且与两个N+区相连通,在漏——源极间形成N型导电沟道,其导电类型与P衬底相反,故又称为反型层,如图1(c)所示。

vGS越大,作用于半导体表面的电场就越强,吸引到P衬底表面的电子就越多,导电沟道越厚,沟道电阻越小。

开始形成沟道时的栅——源极电压称为开启电压,用VT表示。

N沟道MOS管在vGS<VT时,不能形成导电沟道,管子处于截止状态。只有当vGS≥VT时,才有沟道形成。

这种必须在vGS≥VT时才能形成导电沟道的MOS管称为增强型MOS管。沟道形成以后,在漏——源极间加上正向电压vDS,就有漏极电流产生。

参考资料来源:百度百科-NMOS

参考技术A 由于工艺偏差,即使在同一圆片上的芯片,就是不同位置的器件属性会有所不同,就拿MOS管来说(电阻、电容类似),会有FF、SS、TT、FNSP、SNFP情形,表现出来的特性除了阈值电压不一样以外,还有其他一些参数会有所不同,详情可参见Spicemodel工艺文件.Foundry提供这些工艺角是因为他们的工艺在制作过程中会有所偏差,所以我们在设计芯片时需要考虑工艺偏差,在设计阶段使其在各种工艺角下都能正常工作,这样才能使最后的芯片可靠。拉扎维,模拟CMOS集成电路设计,中文版,490页

单一器件所测的结果为正态分布,均值为tt,最小最大限制值为ss与ff。本回答被提问者采纳 参考技术B 由于工艺偏差,即使在同一圆片上的芯片,就是不同位置的器件属性会有所不同,就拿MOS管来说(电阻、电容类似),会有FF、SS、TT、FNSP、SNFP情形,表现出来的特性除了阈值电压不一样以外,还有其他一些参数会有所不同,详情可参见Spicemodel工艺文件.Foundry提供这些工艺角是因为他们的工艺在制作过程中会有所偏差,所以我们在设计芯片时需要考虑工艺偏差,在设计阶段使其在各种工艺角下都能正常工作,这样才能使最后的芯片可靠。

拉扎维,模拟CMOS集成电路设计,中文版,490页

单一器件所测的结果为正态分布,均值为tt,最小最大限制值为ss与ff。

以上是关于mos工艺中工艺角(tt ff ss)都是代表啥的主要内容,如果未能解决你的问题,请参考以下文章