VLSI基础-- 第六章 时序逻辑电路

Posted lyc-seu

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了VLSI基础-- 第六章 时序逻辑电路相关的知识,希望对你有一定的参考价值。

第六章 时序逻辑电路

1. 组合电路和时序电路的区别

- 组合电路:输出是当前输入的函数

- 时序电路: 输出是当前输入和之前输入(状态)的函数

2. 状态机

Moore状态机:输出仅仅与当前状态有关;

Mealy状态机: 输出同输入和当前状态均有关。

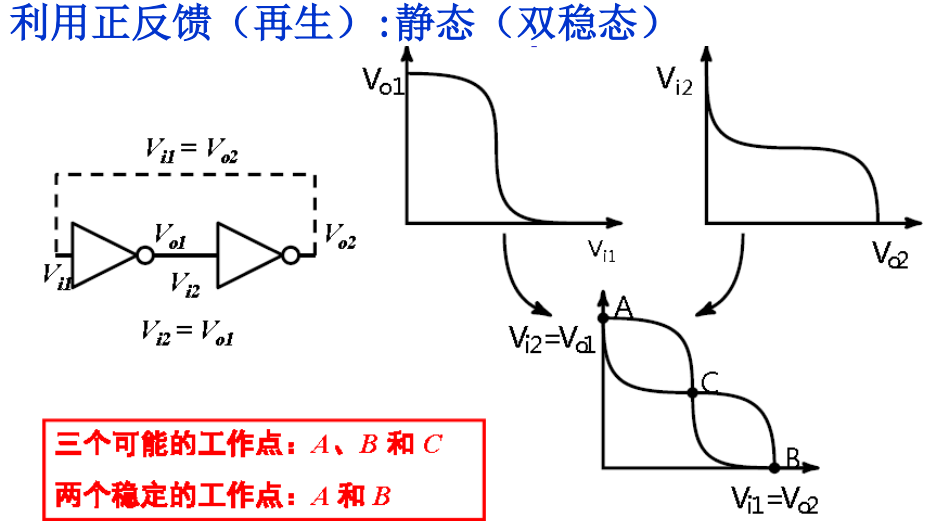

3. 双稳态结构

双稳态器件是存储器件的基本模块,双稳器件的的一种电路结构是:交叉耦合反相器 结构。

双稳态器件存在两种状态:稳定态和亚稳态。

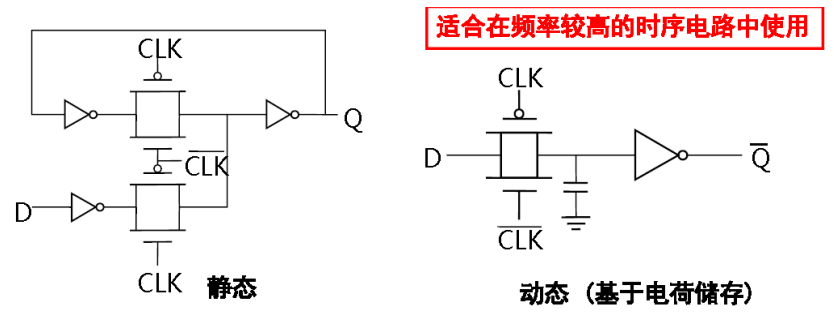

双稳态器件一般都有两种存储机理:

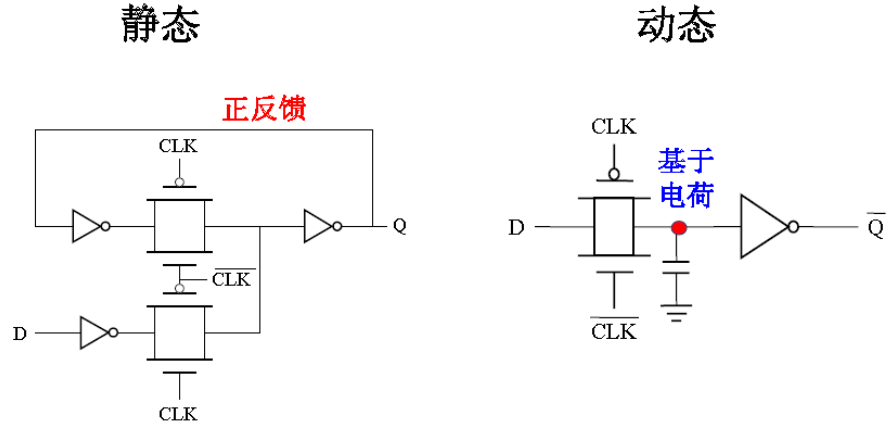

- 基于正反馈(静态)

- 基于电荷存储(动态)

4. 静态存储电路

- 锁存器(Latch)是电平敏感的

- 一般是时钟低电平时锁存数据

- 寄存器(Reister)是边沿触发的(edge-triggered)

- 寄存器是存放二进制数据的器件,通常由Latch构成

- 通常是边沿触发的

- 触发器(Flip-flops)是交叉耦合的门构成的任何双稳态器件

- Latch和Register都可能包含Flip-flop结构

- 包括单稳态、不稳态(震荡)电路

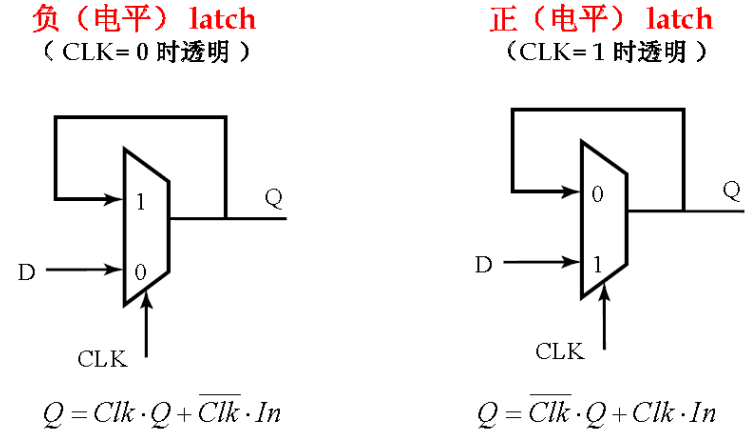

a. Latch

latch的实现方式可以是Mux构成的:

基于传输门实现的Mux的latch:

优点:

- 尺寸设计容易

- 晶体管数目多(时钟负载因而功耗大)

基于传输管Mux的Latch:

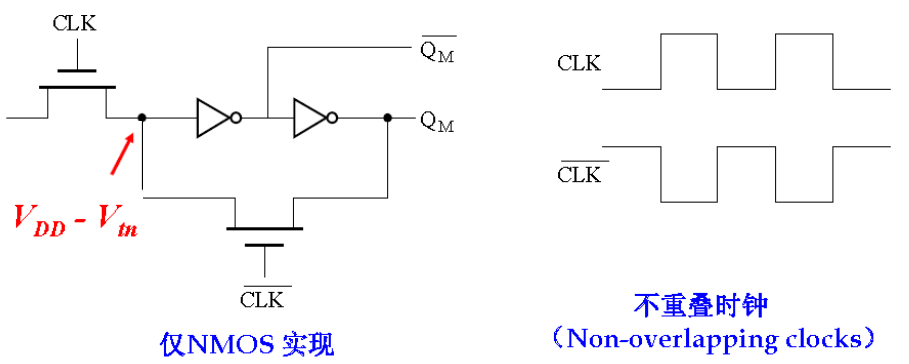

- 仅使用NMOS实现,电路简单,减少了时钟负载

- 由电压阈值损失(影响噪声容限和性能,可能引起静态功耗)

基于三态缓冲器的Latch:

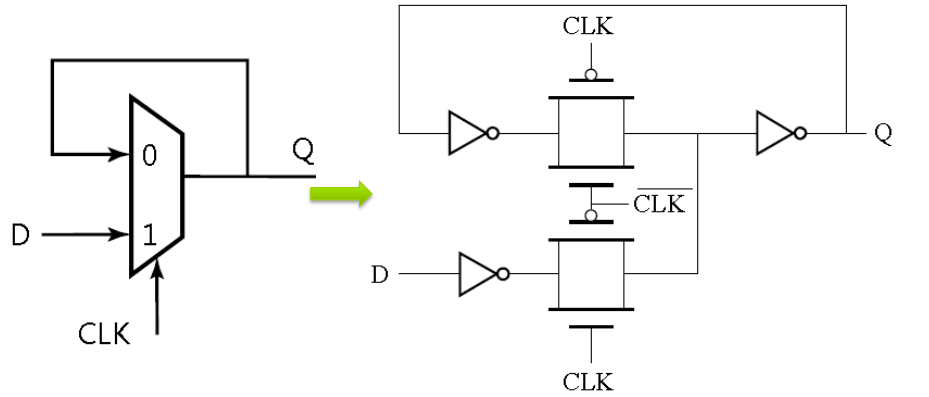

b. D触发器/寄存器

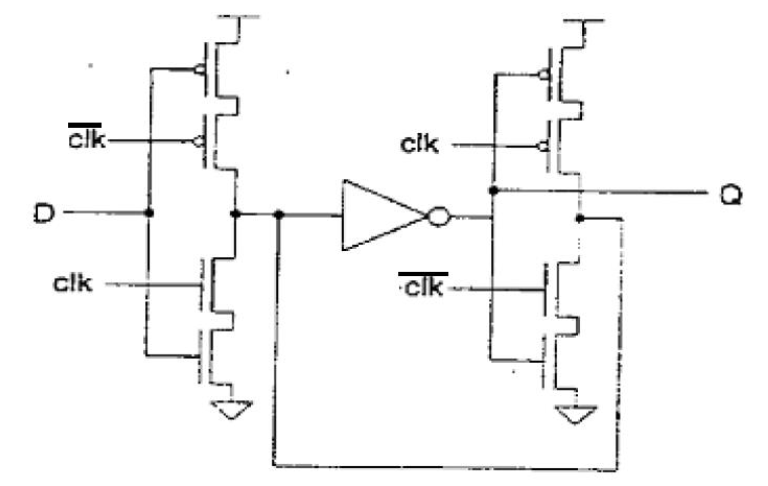

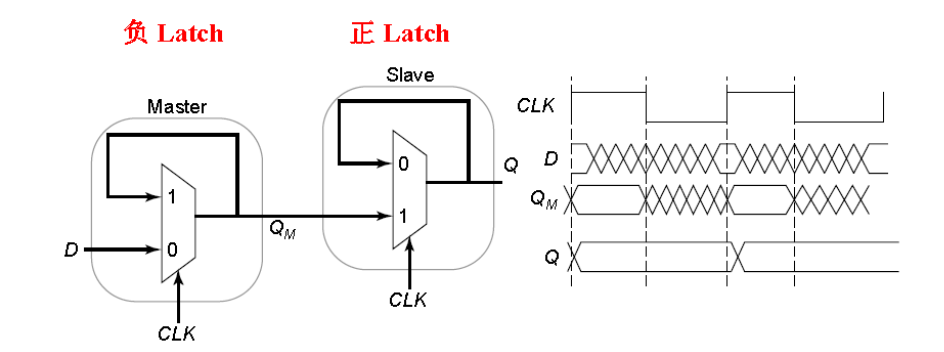

通常是主-从结构, 由一个正电平灵敏Latch和一个负电平灵敏Latch 构成( 主从Latch 对)

输出状态在效果上表现为在时钟边沿处发生变化(正边沿处或负边沿处),确保整个寄存器可能的反馈路径被切断,防止由于反馈造成的信号“竞争”问题。

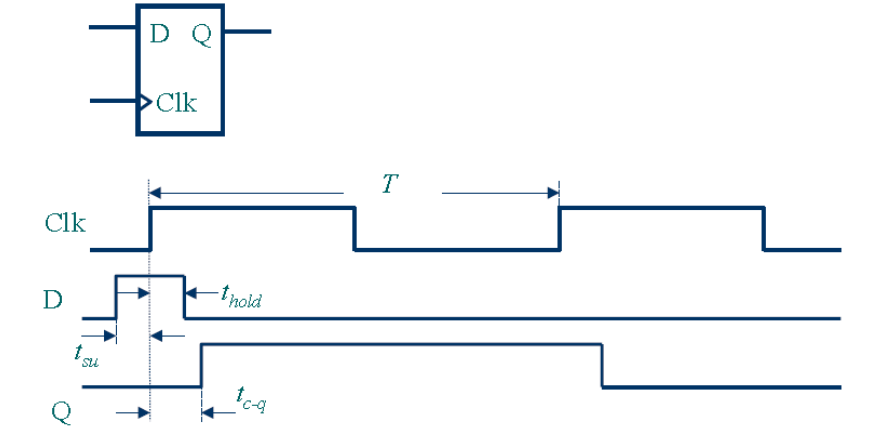

时序参数:

Register的时序参数:

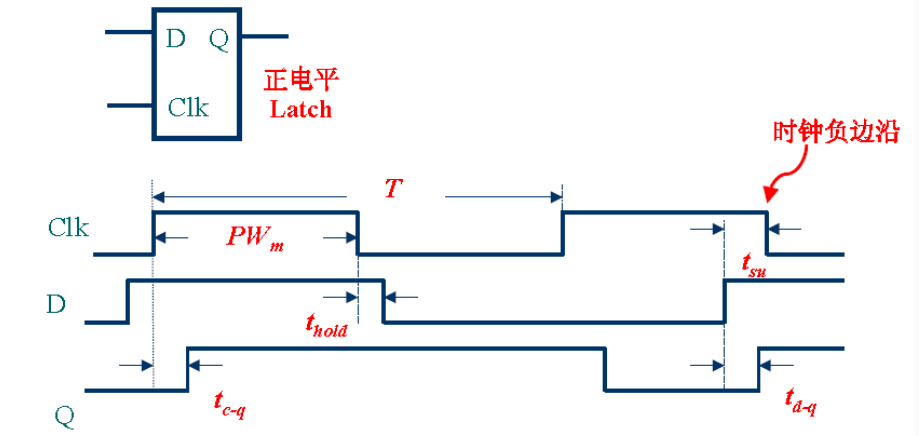

Latch的时序参数:

latch的hold时间实际上是半个周期多,如果数据在时钟正半个周期发生变化,输出也将变化。跟register不同的是,latch还有d-q的概念,即数据在透明期间改变到输出响应的时间。

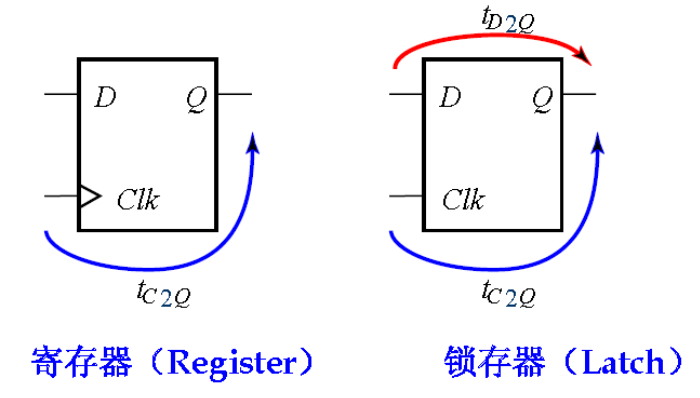

两者的示意图也由差别:

latch的clk没有三角,有三角的代表register。

一般,两个电平灵敏的latch构成主从(Master-Slave)边沿触发寄存器:

高电平时主latch保持,Qm输出不变,Q等于时钟上升沿前的输入D值。效果相当于正沿触发。因此,在时钟上升沿时刻,如果数据D端发生改变,寄存器中仍然存的是D改变之前的值。

Register的工作方式与Verilog中非阻塞赋值的匹配

例如如下verilog代码使用非阻塞赋值语句:

always @(posedge clk or negedge rst_n) begin

if(!rst_n) begin

b <=0;

c <=0;

d <=0;

end

else begin

b <=in;

c <=b;

d <=c;

end

end生成的电路图以及仿真波形如下:

在代码中,b,c,d信号使用非阻塞语句赋值,因为非阻塞语句的特性,在编译器中实际上这几个赋值的表达式会全部依次存入时间队列中,当当前仿真时间内所有活动事件结束后同步执行这些语句,形成了非阻塞的效果。

查看c和b的信号可以发现,在b信号发生跳变的时钟上升沿,c寄存器的主latch开始保持,而从latch的输出仍然是上升沿之前b寄存器的q端值0,因此在当前上升沿结束后,c寄存器的输出仍然是0.

因此时序逻辑中常常是在一个上升沿更新数据,下一个上升沿采样刚更新的数据。

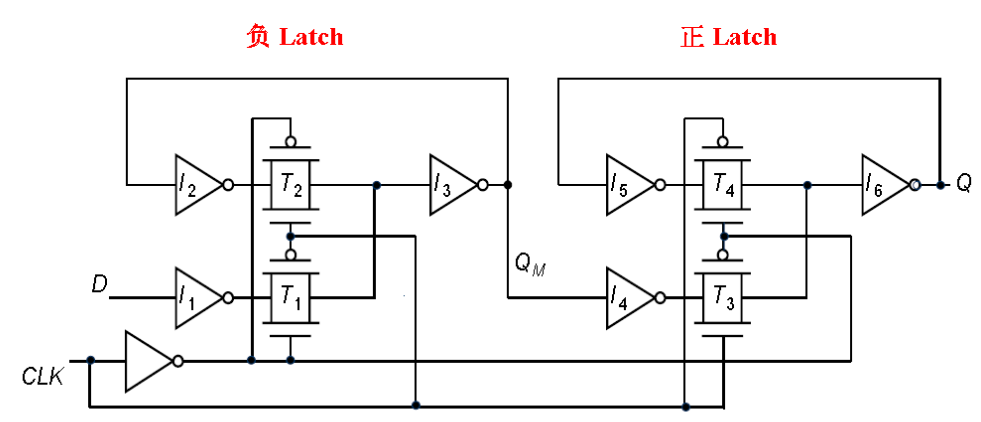

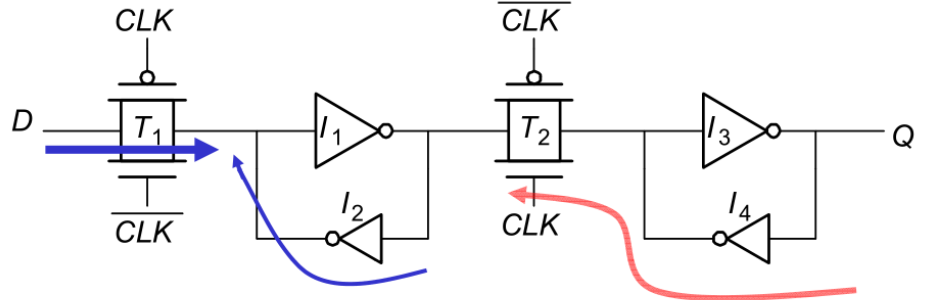

回到正题,由传输门实现的正负电平灵敏latch也可以构成主从边沿触发寄存器:

但是这种结构的缺点在于:时钟负载大,需要8个时钟晶体管。

减少时钟负载的静态主从寄存器

--用强制写入代替Mux

通过两个交叉耦合的反相器实现数据的锁存。前提是T1以及其源驱动必须比(I_2)强,否则无法打断反馈。

优点:时钟晶体管数目从8->4

缺点:

- 是有比逻辑,需要强制写入。

- 存在反向传导,(T_2)和(I_4)会共同影响存储在(I_1-I_2)环路中的数据。

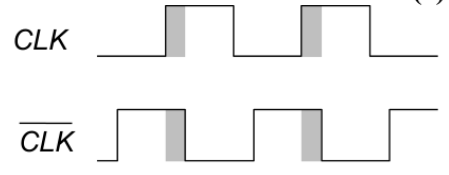

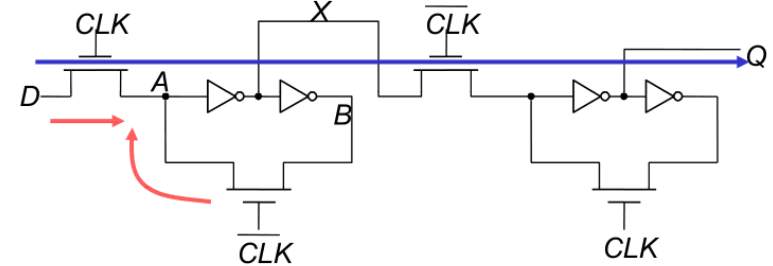

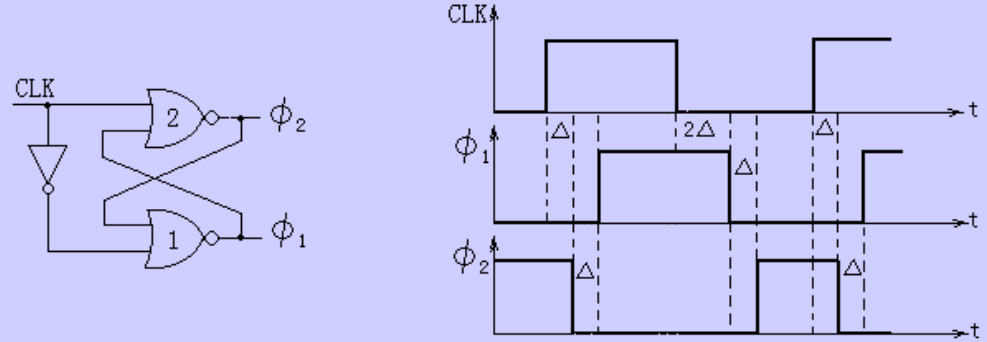

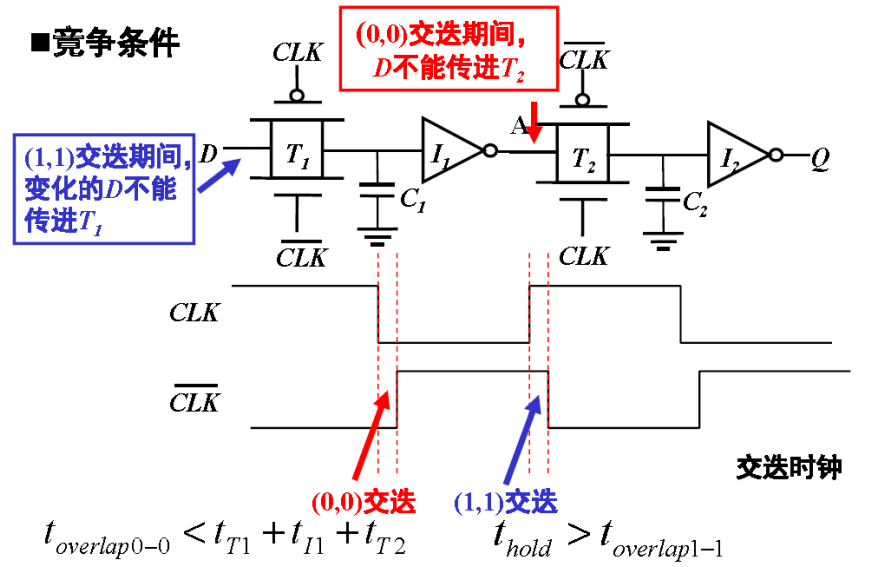

非理想时钟的影响-时钟交迭(overlap)

由于时钟的反向信号与原始时钟之间通常存在一个overlap(组合逻辑延迟),因此进入两级latch的时钟会有交叠的区域,从而导致触发器D-Q的直接通路,形成竞争(race):

此外,节点A会同时被D和B驱动,导致不确定态。

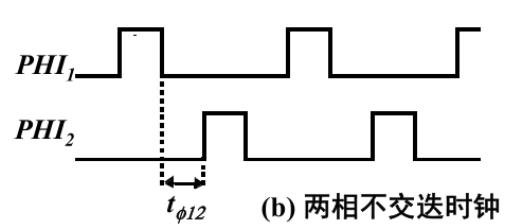

解决办法:两相不交迭时钟

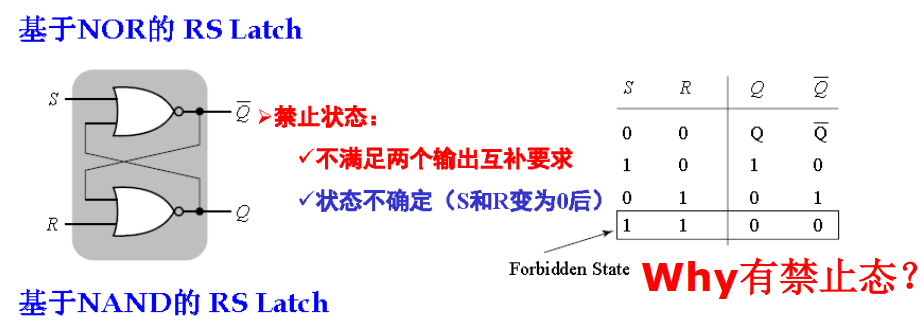

c. RS-触发器(Flip-Flop)

由交叉的NOR或NAND门构成。

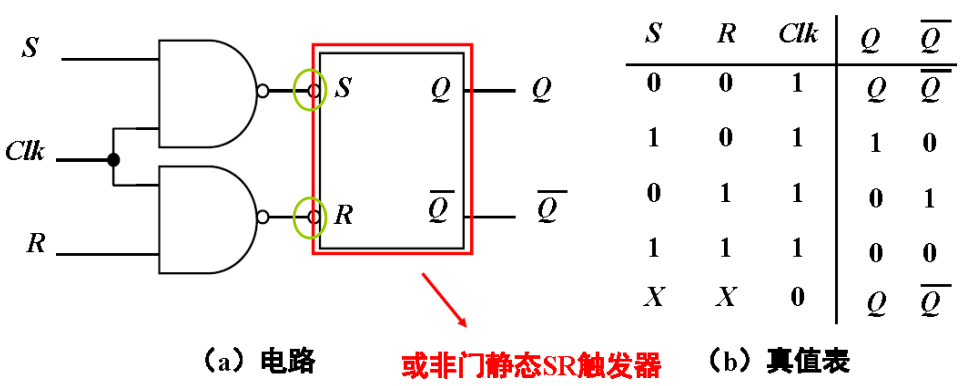

时钟控制的SR触发器:

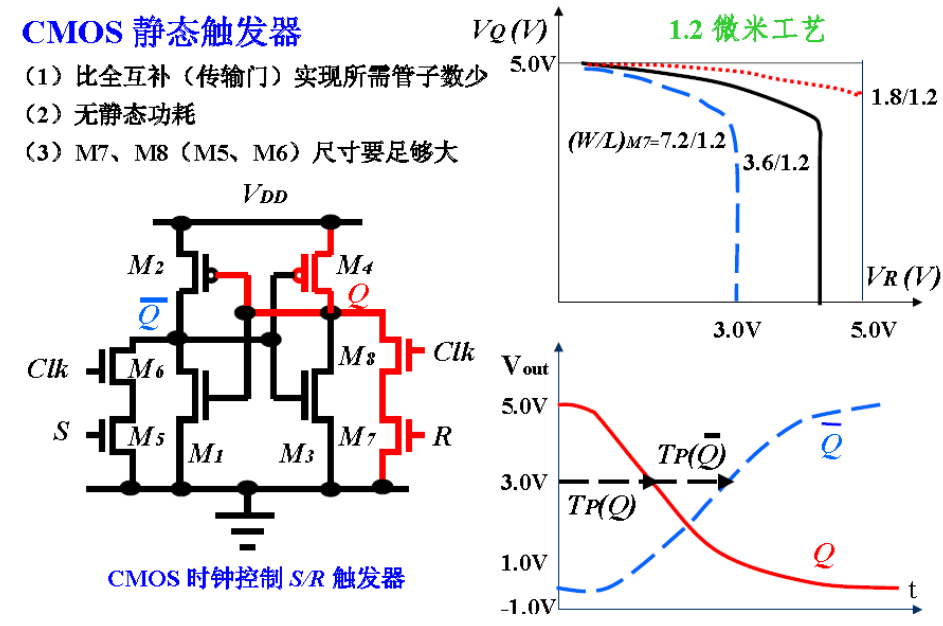

CMOS静态触发器:

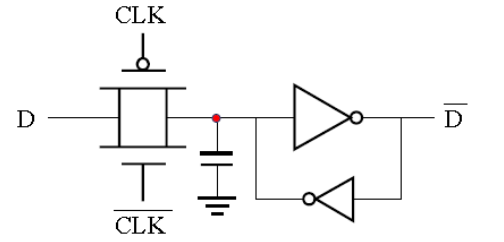

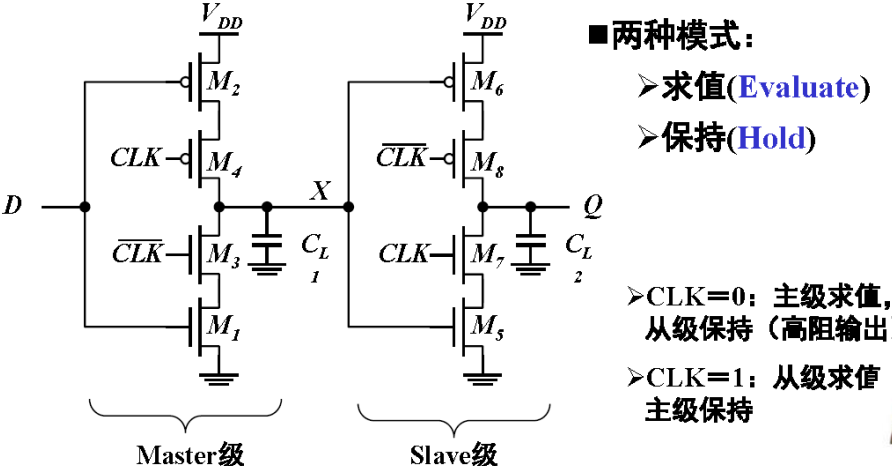

动态Latch和Register

- 比静态latch和register简单

- 不会破坏的读信息:需要输入高阻抗的器件

缺点:

- 漏电问题:基于在寄生电容上存储电荷,由于漏电需要周期刷新

- 高阻抗的内部动态节点容易受噪声干扰

- 漏电影响了低功耗技术(例如无法停止时钟节省功耗)

解决办法:增加一个弱反馈的反相器

- 会增加抗噪声能力,但会增加延时

- 除了高性能数据通路外,一般均应使寄存器成为伪静态或静态

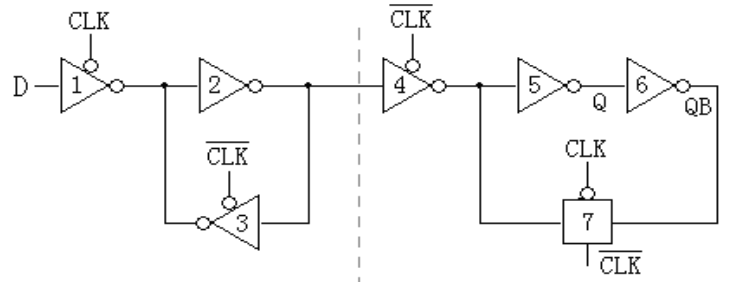

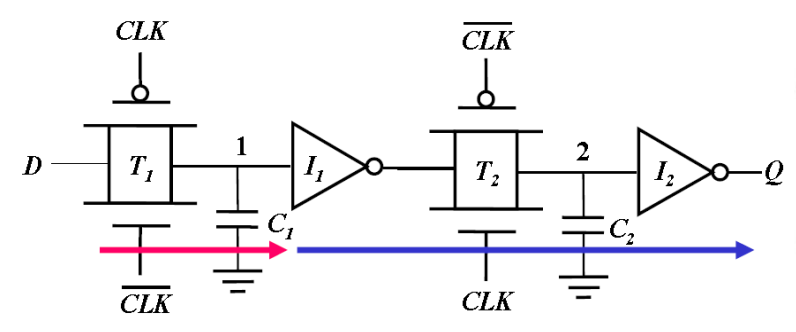

动态传输门边沿触发寄存器

- 建立时间setup = (T_1) ,Clk从低到高之前,数据需要保持(T_1)时间长度才能保证采样的值不变。

保持时间hold = 0

延迟时间:(T_{c-q} = I_1+T_2+I_2)

时钟重叠的影响:

对时钟不敏感的C2MOS(时钟控制CMOS)寄存器

对时钟交迭不敏感,无论是0-0还是1-1交迭,输出都是保持。

但是,在交迭期间还是对输入D有一定的要求。当0-0交迭时,主latch可以接受D从1到0的变化,X可以从0变为1。

- C2MOS的c-q时间很短(相当于一级反相器),因此在构成寄存器链时,要防止“贯通”。

- 如果时钟的上升下降时间太慢,会存在一个时间间隔,N和P都导通,输入和输出之间会产生一条通路,一般使时钟的上升下降时间约小于C2MOS latch传播延时的5倍。

在高频下为了满足上述时钟的要求,应该在寄存器单元内部对clk反相,而非使用全局反相时钟。

以上是关于VLSI基础-- 第六章 时序逻辑电路的主要内容,如果未能解决你的问题,请参考以下文章