IIC总线硬件工作原理(待完善)

Posted y4247464

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了IIC总线硬件工作原理(待完善)相关的知识,希望对你有一定的参考价值。

一、IIC基础概念

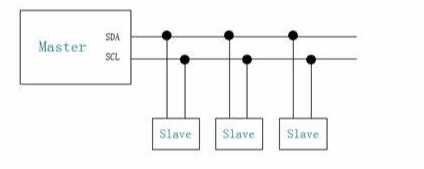

IIC(Inter-Integrated Circuit)总线是一种由PHILIPS公司开发的两线式串行总线,用于连接微控制器及其外围设备。IIC总线最初为音频和视频设备开发,如今主要在服务器管理中使用,其中包括单个组件状态的通信。例如管理员可对各个组件进行查询,以管理系统的配置或掌握组件的功能状态,如电源和系统风扇。可随时监控内存、硬盘、网络、系统温度等多个参数,增加了系统的安全性,方便了管理。

1、IIC特点

简单:接口在组件上,占用空间小

高效:能够以10Kbps的最大传输速率支持40个组件

多主控:任何能够进行发送和接收的设备都可以成为主总线

2、协议简介

总线信号 :

SDA :串行数据线

SCL :串行时钟

总线空闲状态 :

SDA :高电平

SCL :高电平

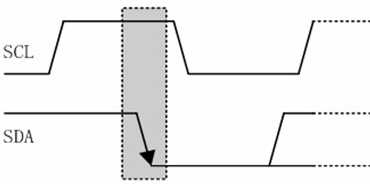

起始位:SCL为高电平期间 SDA出现下降沿

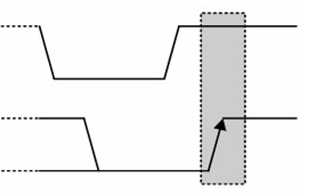

终止位:SCL为高电平期间 SDA出现上升沿

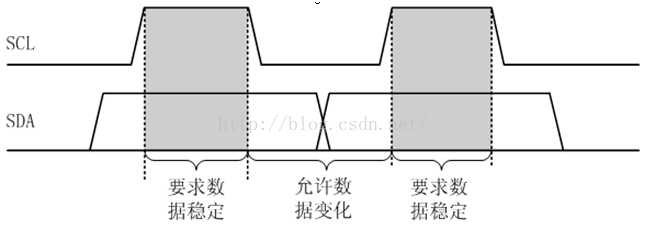

数据传输 :SDA的数据在SCL高电平期间被写入从机。所以SDA的数据变化要发生在SCL低电平期间。

IIC时钟频率:不高于400K

IIC器件地址:每一个IIC器件都有一个器件地址,有的器件地址在出厂时地址就设定好了

响应信号(ACK):处理器把数据发给外接IIC设备,如何知道IIC设备数据已经收到呢?就需要外接IIC设备回应一个信号给处理器。处理器发完8bit数据后就不再驱动总线了(SDA引脚变输入),而SDA和SDL硬件设计时都有上拉电阻,所以这时候SDA变成高电平。那么在第8个数据位,如果外接IIC设备能收到信号的话接着在第9个周期把SDA拉低,那么处理器检测到SDA拉低就能知道外接IIC设备数据已经收到。

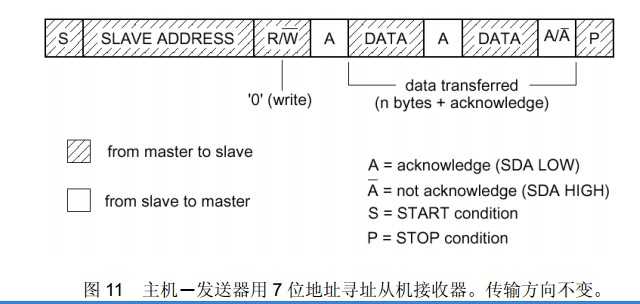

用7bit表示从地址,那么可以挂载的从设备数是2的7次方128个。处理器想写的话:先发送起始位,再发一个8bit数据:前7bit表示从地址,第8bit表示读或者写。0write是处理器往IIC从设备发,1read是IIC从设备往处理器发。第9个时钟周期回复响应信号。

(以上摘自:https://blog.csdn.net/zailushangha/article/details/8233448)

以上是关于IIC总线硬件工作原理(待完善)的主要内容,如果未能解决你的问题,请参考以下文章