从数字IC后端设计实现看先进工艺7nm实现的各种挑战

Posted lelin

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了从数字IC后端设计实现看先进工艺7nm实现的各种挑战相关的知识,希望对你有一定的参考价值。

目前虽然号称拥有或将要研发7nm工艺的有多家工艺厂商,但是具有实际流片能力的可能只有TSMC和三星。随着GlobalFoundries最近宣布放弃7nm的进一步研发,以及尽管Intel的10nm和这几家的7nm差不多一个水准,但是要跳票到2019年,因此短期内应该就是双雄争霸的局面。

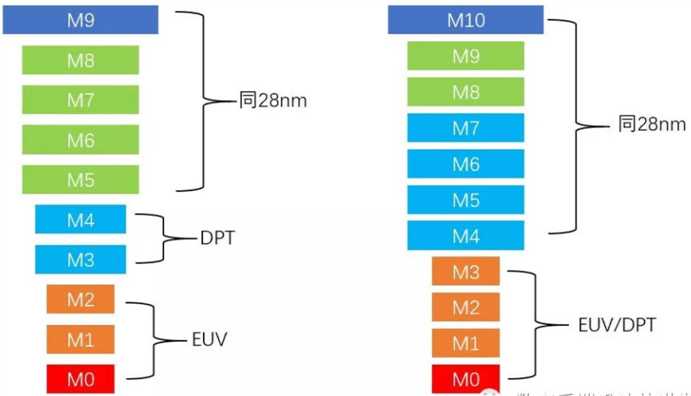

玩家越来越少,技术实现也没有太多选择,目前的方法无非两种:Multiple Pattern和EUV。前者沿用16nm/14nm等工艺的多重曝光技术,后者采用极紫外光刻机一次曝光。在工艺上的实现上,可能会有如下方案:

实际中可能不同的厂商会采取不同的策略,但是技术大致如此。需要引起大家注意的是,无论是何种方案,都增加了一层叫做M0的金属,这层金属一般来说是专门用来生成标准单元的power/ground rail,普通的信号线是不能走这一层的。

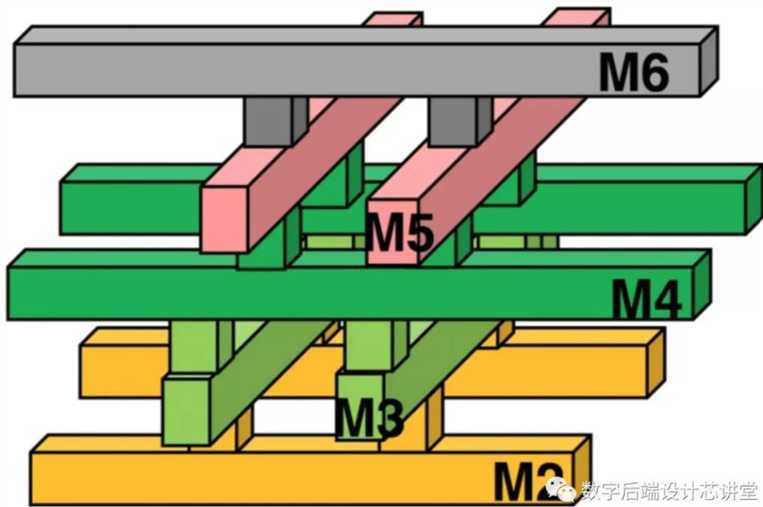

1. Signal EM以及Via ladder/Via pillar

由于7nm的底层金属宽度进一步缩小,因此出现signal EM的概率也逐渐增加,尤其是clock line上,大驱动的cell有很大可能会有signal EM的问题。针对这个现象,业界提出了Via ladder/Via pillar的概念和实现方法。他们其实本质是同一种东西,只是不同厂商的不同叫法,其基本原理如下图所示:

简单地说,就是把底层金属的pin通过“梯子”的方式逐级向上打通,以多个平行的金属shape分散电流,从而达到缓解和消除signalEM的目的。在实际设计中需要定义各类via pillar的参数,同时对需要via pillar的标准单元的output pin设置via pillar的属性,EDA工具可以根据设置的参数自动加上via pillar。

虽然上述方法能够解决EM的问题,但是同时会带来一个负面影响:占用额外的绕线资源。因此,对于绕线资源不是很丰富的设计,使用via pillar需要谨慎,可能需要控制加via pillar的cell的数量。

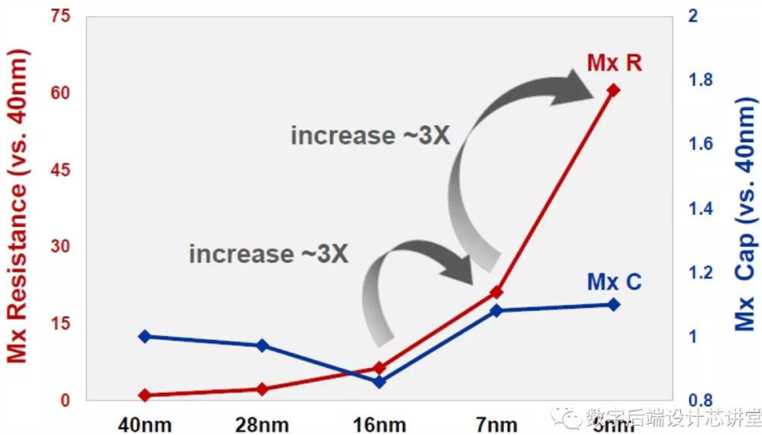

2. RC变化

随着线宽的进步缩小,金属层上尤其是底层金属的R逐渐成为delay贡献中的主导因素。下图展示了TSMC家的工艺进化过程中,RC的变化趋势

可以看出,在进入7nm后,Resistance的变化十分剧烈,增量达3倍之多。这种阻值增加给后端带来的显著变化就是,如果绕线用到了底层金属,那么net delay以及cell delay将会明显增大,给时序收敛带来额外的麻烦。在我们做的设计中,对于timing critical的path,必须通过限制金属层来减少这种负面影响,否则某些setup violation以传统的Vt swap或者size up等ECO手段是很难收敛的。

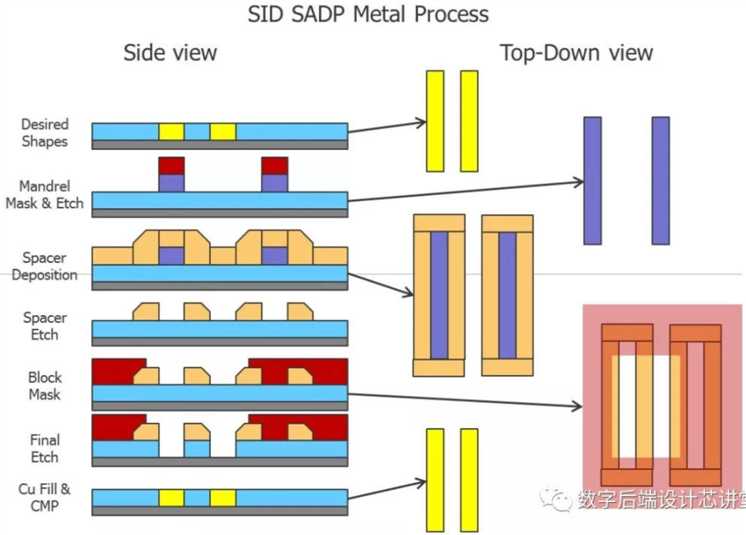

3.SADP(Self-Aligned Double Pattern)

这是工艺实现中,对于小间距金属的刻蚀方法之一。对此有兴趣的数字IC后端工程师可以自行查一查它的技术细节,在此我们简述一下它的特点。其基本思路如下图所示:

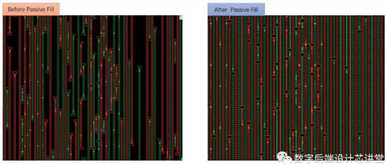

而这种实现方法对数字后端的要求就是:对于需要使用SADP方法刻蚀的金属层来说,在物理上必须采用所谓的“Passive Fill”的方式使得所有的金属shape呈现如下统一的pattern:

形成上述pattern的目的在于,让所有SADP的金属层以相同的width,相同的spacing均匀地布满整个design。那么这样一来如何区分哪些是design需要的shape,哪些是passive fill的shape呢?答案是通过图中那些小小的横向方框将这两种shape“切分”开来。这样在实际生产后这些小方框的地方就会天然断开,从而不会影响芯片的实际功能。

对于后端来说,passive fill进一步增加相关net的capacitance值,会给timing带来一定的负面影响。与此同时,passive fill还会引入新的DRC,虽然大部分工具都能解决,但是仍然会有少量violation需要工程师去修掉,从而进一步增加我们的工作量。

以上是关于从数字IC后端设计实现看先进工艺7nm实现的各种挑战的主要内容,如果未能解决你的问题,请参考以下文章