DDR接口时序实例

Posted lelin

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了DDR接口时序实例相关的知识,希望对你有一定的参考价值。

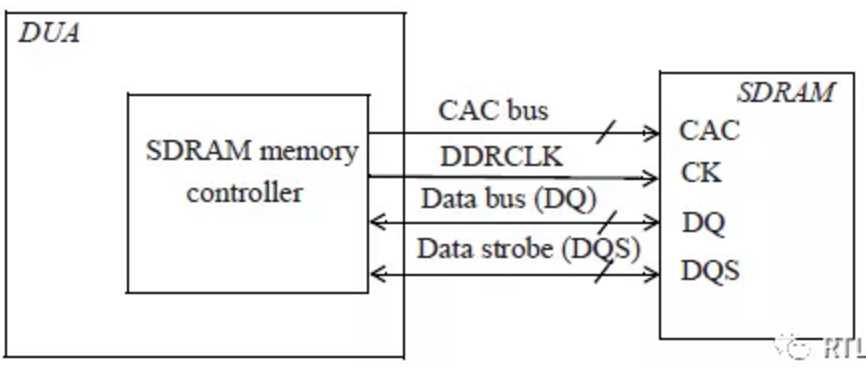

DDR SDRAM接口的示意图:

CAC总线表示Command,Address,Control Pin,时序相对简单,单向单周期,通过以下命令约束:

create_generated_clock -name DDRCLK-source [get_pins UPLL0/CLKOUT]-divide_by 1[get_ports DDRCLK]set_output_delay -max 0.75 -clock DDRCLK [get_ports CAC]set_output_delay -min -0.75 -clock DDRCLK [get_ports CAC]

DQ和DQS是同步对齐的,这是DDR的特点。DQS作为DQ的采样时钟,保证高速采样频率。

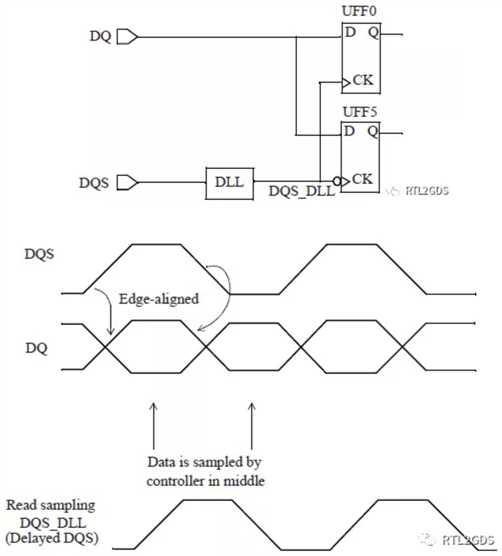

在进行读操作时,对应的电路结构和波形如下图:

可以这样定义:

#工作频率200MHzcreate_clock -period 5 -name DQS [get_ports DQS]#上升沿采样时的delayset_input_delay 0.4 -max -clock DQS [get_ports DQ]set_input_delay -0.4 -min -clock DQS [get_ports DQ]#下降沿采样时的delayset_input_delay 0.35 -max -clock DQS -clock_fall [get_ports DQ]set_input_delay -0.35 -min -clock DQS -clock_fall [get_ports DQ]#launch和capture在同一个沿set_multicycle_path 0 -setup -to UFF0/Dset_multicycle_path 0 -setup -to UFF5/D

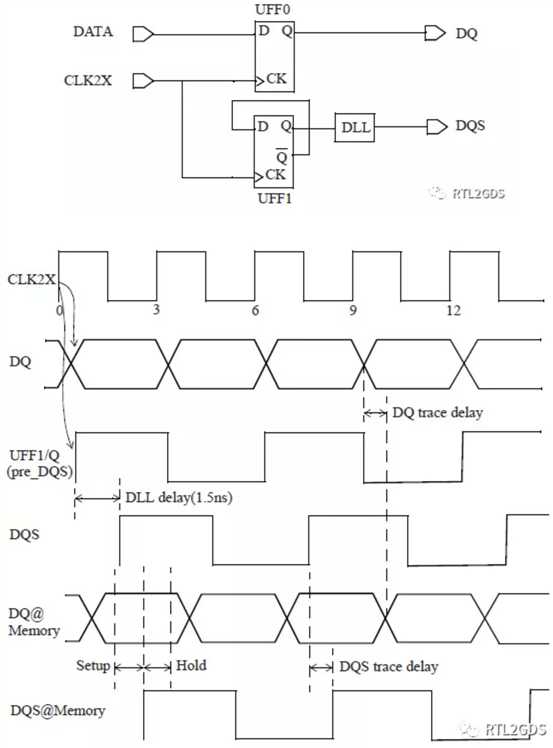

在进行写操作时,对应的电路结构和波形如下图:

可以这样定义:

create_clock -period 3 [get_ports CLK2X]create_generated_clock -name pre_DQS-source CLK2X-divide_by 2[get_pins UFF1/Q]create_generated_clock -name DQS-source UFF1/Q-edge {1 2 3}-edge_shift {1.5 1.5 1.5}[get_ports DQS]set_output_delay -clock DQS -max 0.25 -rise [get_ports DQ]set_output_delay -clock DQS -max 0.4 -fall [get_ports DQ]set_output_delay -clock DQS -min -0.15 -rise [get_ports DQ]set_output_delay -clock DQS -min -0.12 -fall [get_ports DQ]

总之,DDR接口的时序SDC还算复杂,值得多研究一会。

以上是关于DDR接口时序实例的主要内容,如果未能解决你的问题,请参考以下文章