ahb时序解析

Posted zhiminyu

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了ahb时序解析相关的知识,希望对你有一定的参考价值。

ahb 总线架构

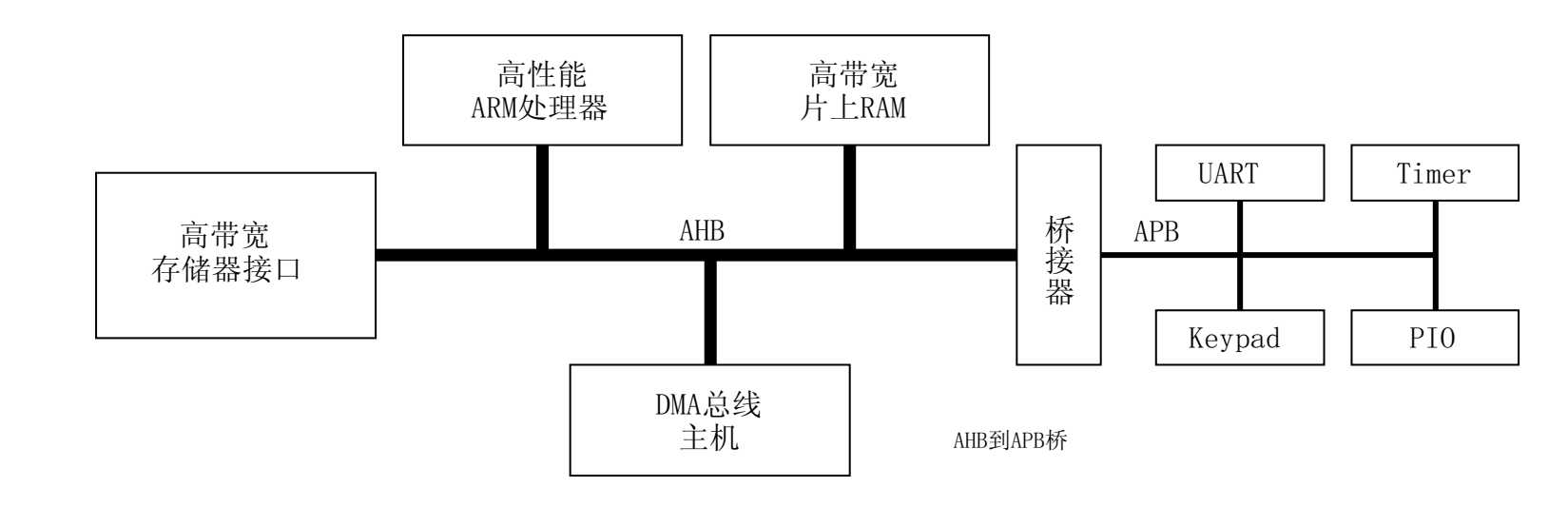

AHB(Advanced High Performance Bus)总线规范是AMBA(Advanced Microcontroller Bus Architecture) V2.0总线规范的一部分,AMBA总线规范是ARM公司提出的总线规范,被大多数SoC设计采用,它规定了AHB (Advanced High-performance Bus)、ASB (Advanced System Bus)、APB (Advanced Peripheral Bus)。AHB用于高性能、高时钟频率的系统结构,典型的应用如ARM核与系统内部的高速RAM、NAND FLASH、DMA、Bridge的连接。APB用于连接外部设备,对性能要求不高,而考虑低功耗问题。ASB是AHB的一种替代方案。现在已经有AHB V5.0。

AHB总线的强大之处在于它可以将微控制器(CPU)、高带宽的片上RAM、高带宽的外部存储器接口、DMA总线主机、各种拥有AHB接口的控制器等等连接起来构成一个独立的完整的SOC系统,不仅如此,还可以通过AHB-APB桥来连接APB总线系统。AHB可以成为一个完整独立的SOC芯片的骨架。

AHB特点:

分块处理

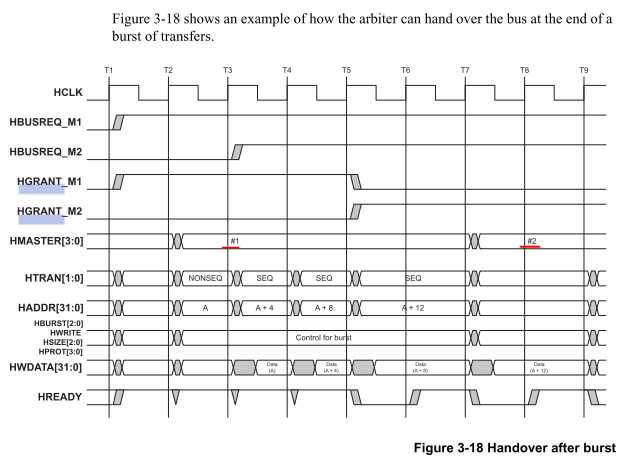

单周期总线主机移交

单时钟沿操作

无需三态门的实现方式

更宽的数据总线架构(64位或者128位)

流水线操作

可支持多个总线主设备(最多16个)

ahb 总线组成

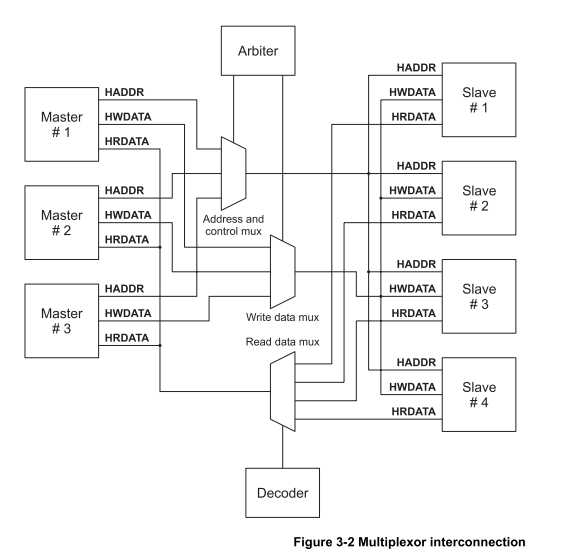

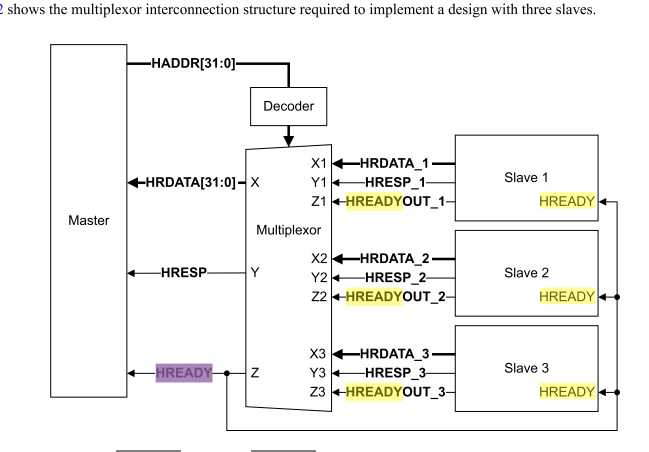

AHB总线由AHB总线主机(Master)、AHB总线从机(Slave)和Infrastructure构成。Infrastructure由仲裁器、数据多路选择器、地址控制多路选择器、译码器构成。

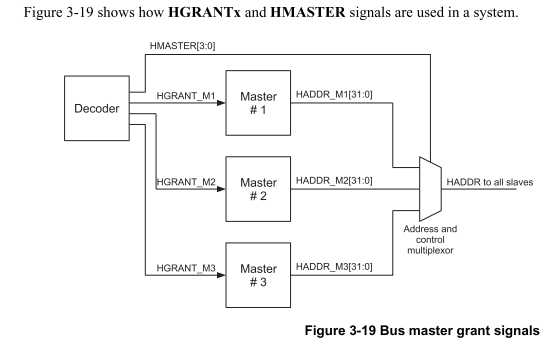

AMBA AHB 总线协议设计使用一个中央多路选择器互联方案。该方案中,所有总线主机设备输出地址和控制信号来指示它们想执行的传输,同时仲裁器决定哪一个主机能够将它

的地址和控制信号连通到所有的从机。当然也需要一个译码器来控制读数据和响应多路信号选择器,多路信号选择器选中来自传输中所包含从机的适当信号。

AHB 主机: 总线主机能够通过提供地址和控制信息发起读写操作。任何时候只允许一个总线主机处于有效状态并能使用总线。

AHB 从机: 总线从机在给定的地址空间范围内响应读写操作。总线从机将成功、失败或者等待数据传输的信号返回给有效的主机。

AHB 仲裁器: 总线仲裁器确保每次只有一个总线主机被允许发起数据传输。即使仲裁协议已经固定,任何一种仲裁算法,比如最高优先级或者公平访问都能够根据应用要求而得到执行。AHB 必须只包含一个仲裁器,尽管在单总线主机系统中这显得并不重要。

AHB 译码器: AHB 译码器用来对每次传输进行地址译码并且在传输中包含一个从机选择信号。

所有 AHB 执行都必须仅要求有一个中央译码器。

master interface

slave interface

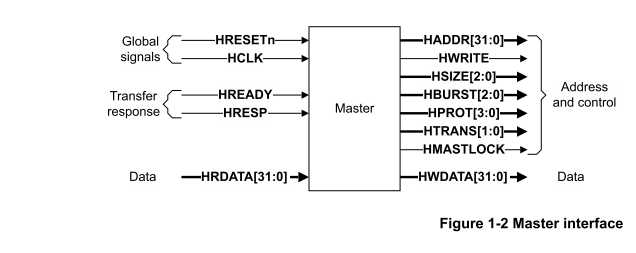

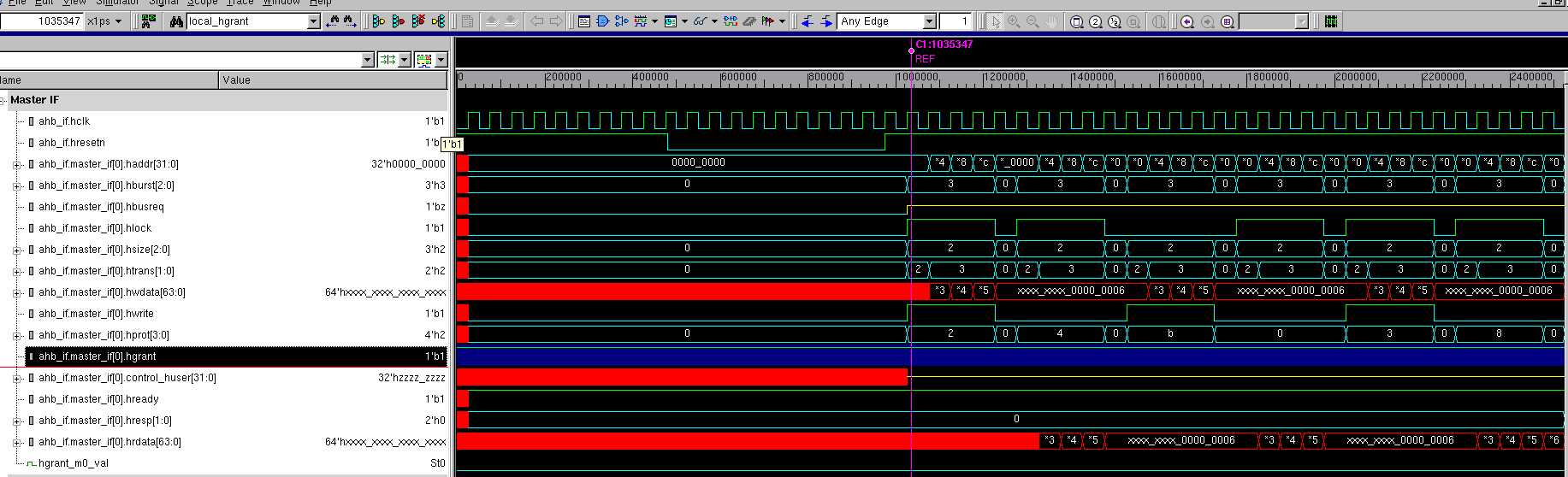

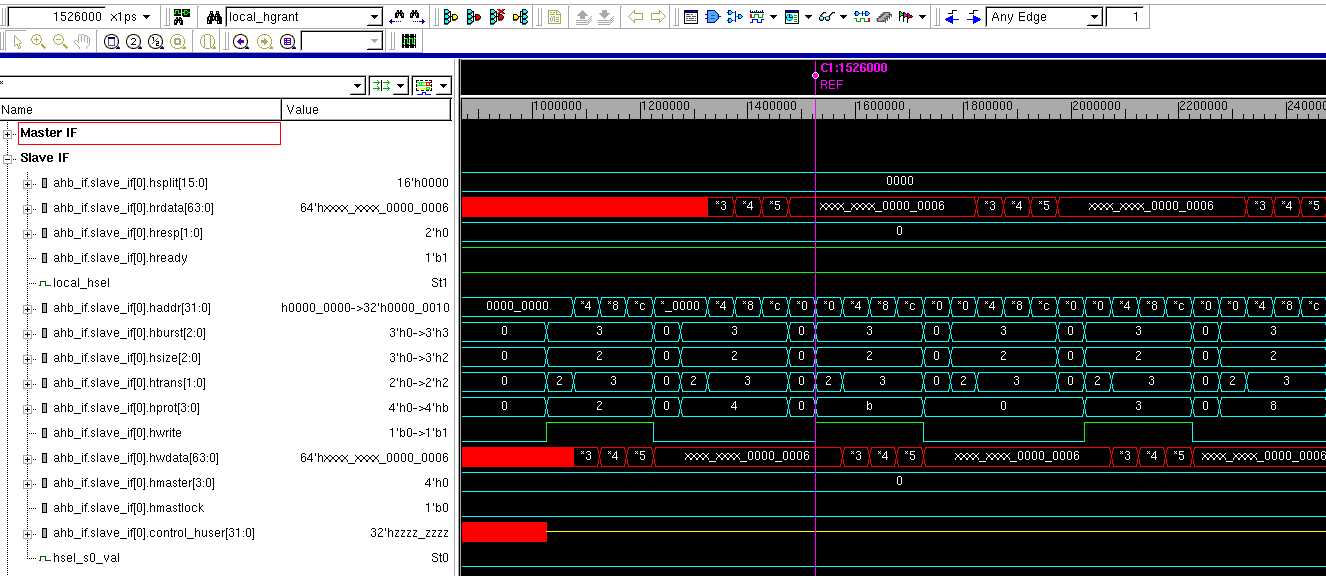

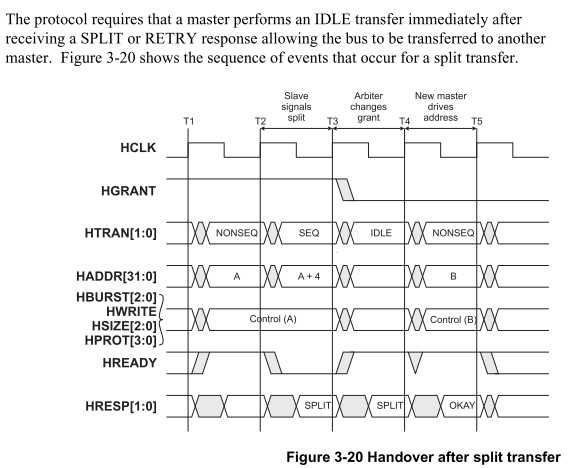

master侧时序和信号分析:

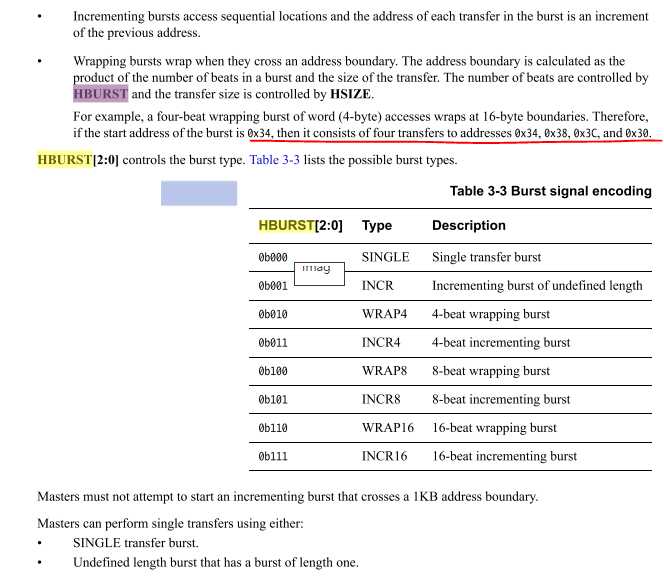

- hburst[2:0] :用于控制突发类型(模式)

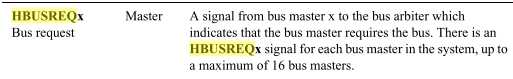

- hbusreq

master向bus仲裁器申请bus总线使用权;最多可以有16个master。

-

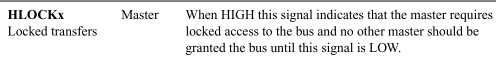

hlock

当该信号为高时,表示master请求锁定对总线的访问,在HLOCK为LOW之前,其他master不允许获得总线。

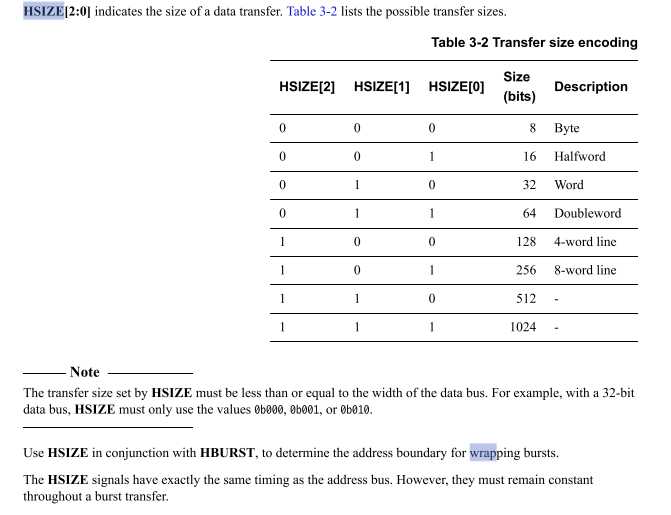

- HSIZE[2:0]

-

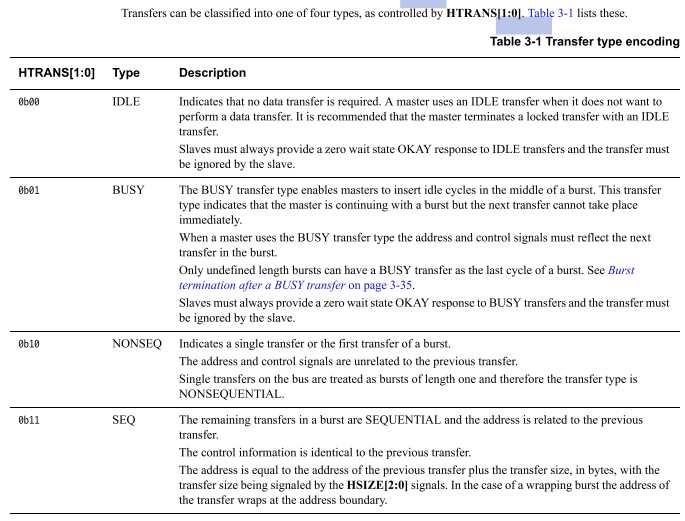

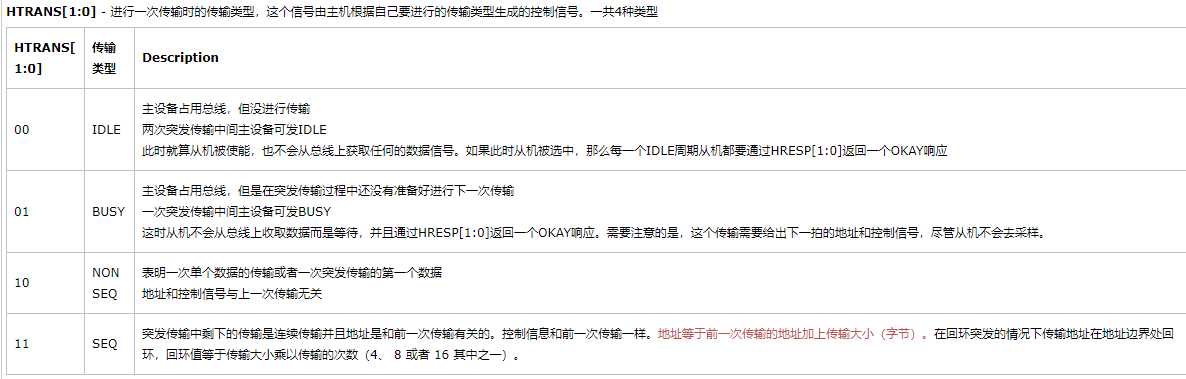

HTRANS[1:0]

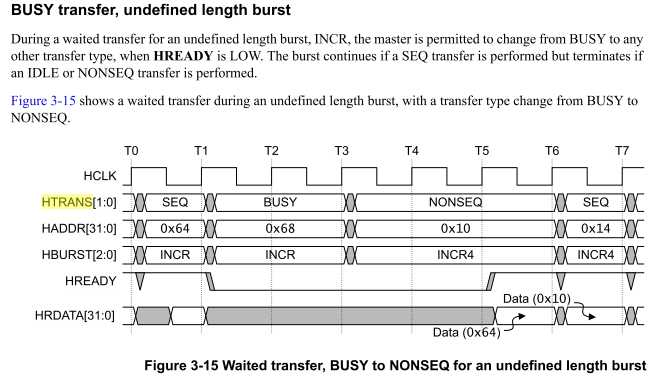

在wait Undefine Length busrt(INCR)的传输期间,当HREADY为低时,允许主机从BUSY改变为任何其它传输类型。如果执行SEQ传输,则burst继续,如果执行IDLE或NONSEQ传输,则burst终止。在T3~T5,HREADY为LOW时,HTRANS需保持。

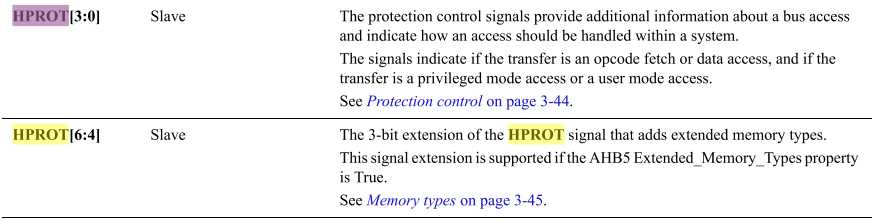

- HPROT

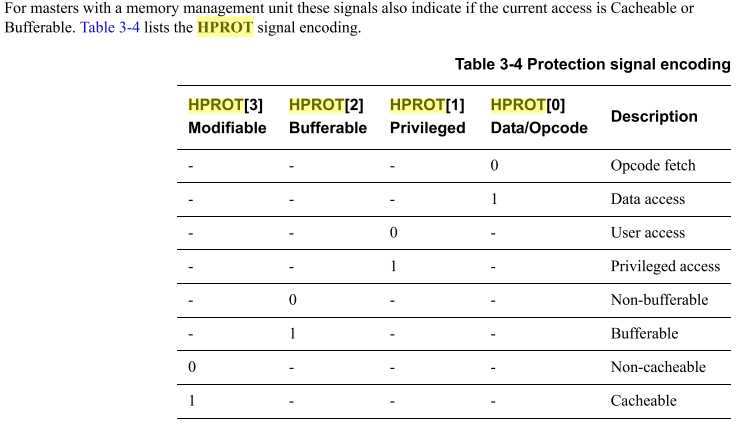

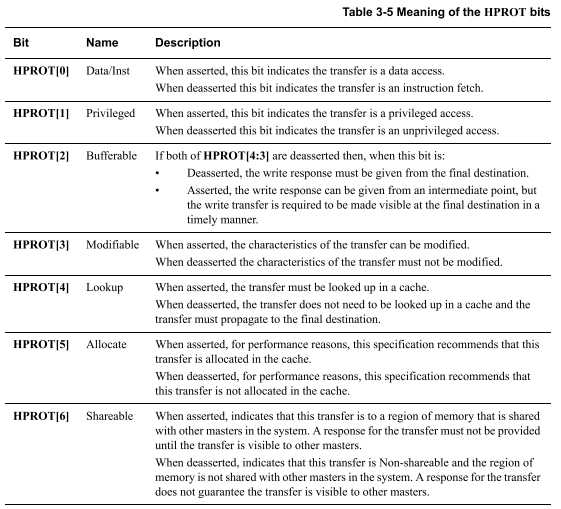

HPROT[6:4]是AHB5新增的,用来表示extended memory types,如果Extended_Memory_Types是True,HPROT[6:4]有效。 Issue A of this specification defined a 4-bit HPROT signal, which is described in this section.

Issue B of this specification adds extended memory types and this is described in more detail in Memory types on page 3-45.

-------------Note---------------

The name of HPROT[3] is changed between Issue A and Issue B of this specification, but the definition remains the same. In Issue A HPROT[3] was designated Cacheable, in Issue B it is designated Modifiable. ------------------------------------------------------------------------------------------------------------------------------- The protection control signals, HPROT[3:0], provide additional information about a bus access and are primarily intended for use by any module that implements some level of protection.

slave一般不使用HPROT信号。(Bufferable和Cacheable的区别详见相应博客随笔)

AHB5 defines the Extended_Memory_Types property. This property defines whether an interface supports the extended memory types described in this section. If this property is not defined, then the interface does not support the extended memory types.

This issue of the specification adds additional HPROT signaling and provides a more detailed list of requirements for each of the memory types. 该规范的这一期增加了额外的HPROT信令,并提供了每种存储器类型的更详细的要求列表。

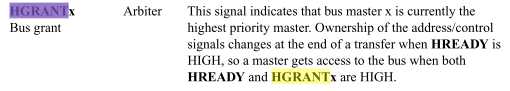

- HGRANT:

-

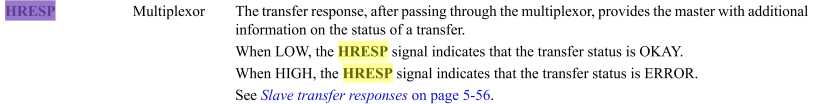

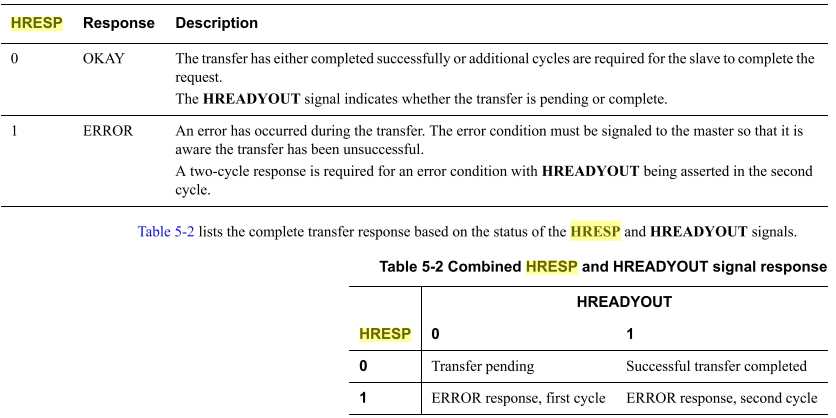

HRESP[1:0]

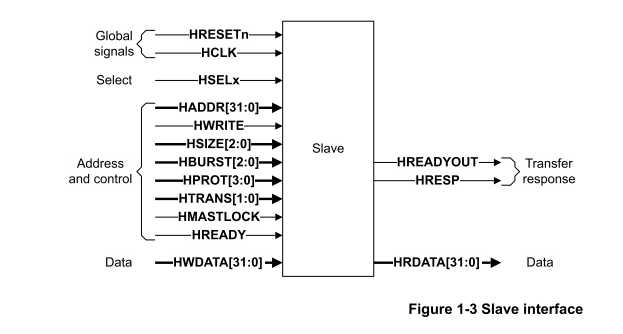

slave侧时序和信号分析:

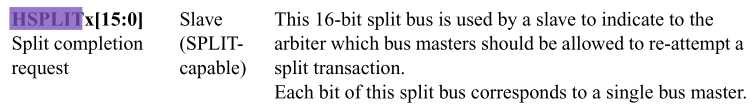

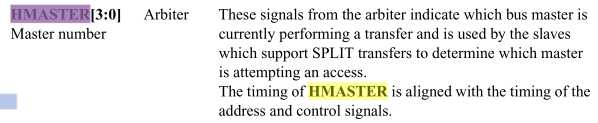

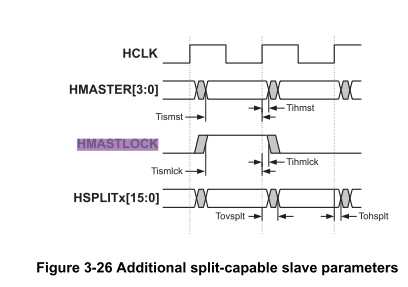

- HSPLIT[15:0]:当slave认为需要多次初理时,用于分割传输,该信号在slave和arbiter之间使用。

- hmaster[3:0]:用来表示哪个master正在占用总线

- hmastlock:表示当前master正在执行锁定的传输序列,该信号与hmaster具有相同的时序。

参考资料:

以上是关于ahb时序解析的主要内容,如果未能解决你的问题,请参考以下文章