FPGA流水灯(含Vivado使用流程)

Posted dingdangsunny

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了FPGA流水灯(含Vivado使用流程)相关的知识,希望对你有一定的参考价值。

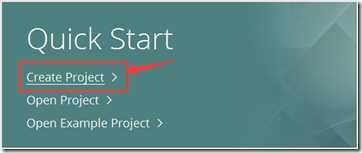

1. 建立工程

新建工程。

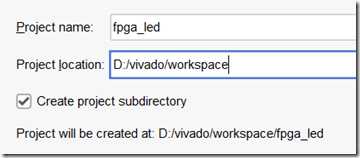

工程名和工程路径。

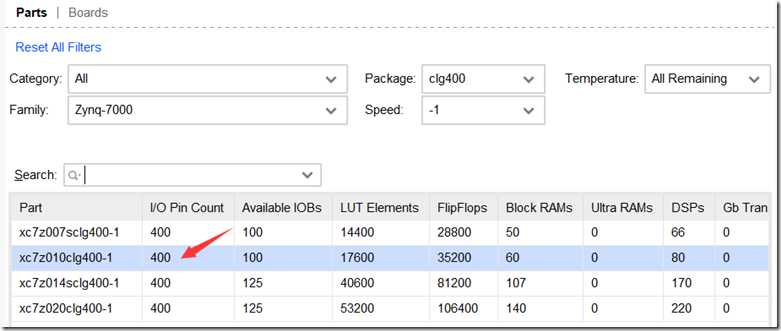

根据芯片型号选择。

其他一路Next直至Finish。

2. 源文件

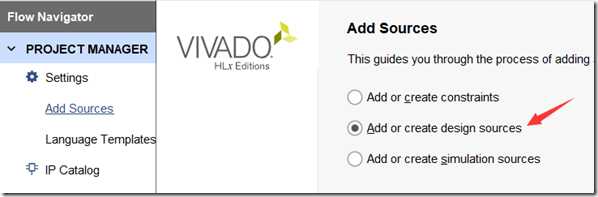

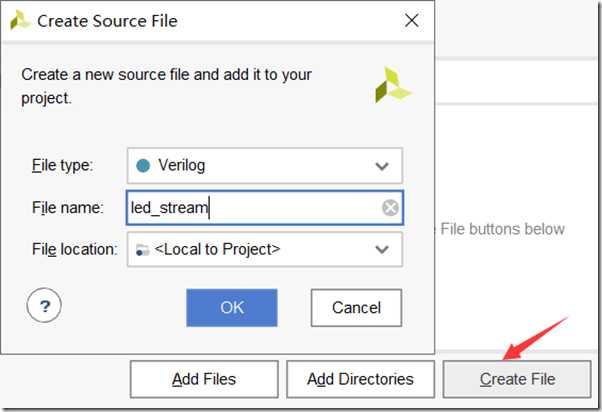

新建源文件:

Add Sources→Add or create design sources

Verilog代码:(这里先以流水灯为例)

module led_stream( output reg [3:0] led, // LED4 to LED1, 1 on, 0 off input clk, // FPGA PL clock, 50 MHz input rst_n // FPGA reset pin ); reg [31:0] cnt; reg [1:0] led_on_number; //clock input 50000000 parameter CLOCK_FREQ =50000000; parameter COUNTER_MAX_CNT=CLOCK_FREQ/2-1;//change time 0.5s always @(posedge clk, negedge rst_n) begin if(!rst_n) begin cnt <= 31‘d0; led_on_number <= 2‘d0; end else begin cnt <= cnt + 1‘b1; if(cnt == COUNTER_MAX_CNT) begin//count time 0.5s cnt <= 31‘d0; led_on_number <= led_on_number + 1‘b1; end end end always @(led_on_number) begin case(led_on_number) 0: led <= 4‘b0001; 1: led <= 4‘b0010; 2: led <= 4‘b0100; 3: led <= 4‘b1000; endcase end endmodule

时钟频率CLOCK_FREQ为50000000Hz。通过cnt累加计数,达到0.5s后改变一次输出状态。

3. 仿真文件

Add Sources→Add or create simulation sources

`define clk_cycle 10 module led_sim(); reg clk, rst_n; wire [3:0] led; always #`clk_cycle clk = ~clk; initial begin clk = 0; rst_n = 1; #10 rst_n = 0; #10 rst_n = 1; end led_stream led_stream(.rst_n(rst_n), .clk(clk), .led(led)); endmodule

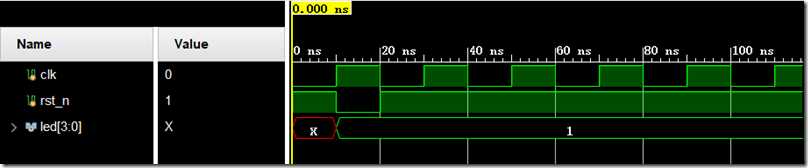

时钟周期20ns,故设置clk每隔10ns翻转一次。效果如下图所示。

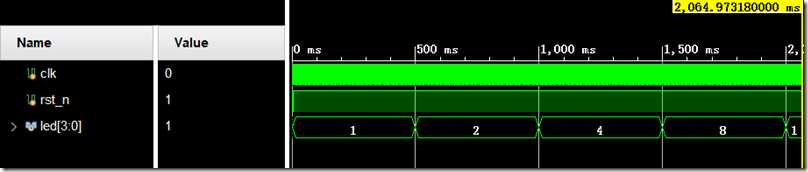

仿真至2s出头,得到结果如下图所示,可知程序正确。

led按照0001→0010→0100→1000的顺序变化。

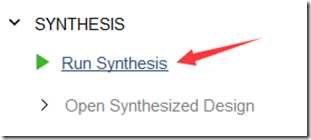

4. 综合

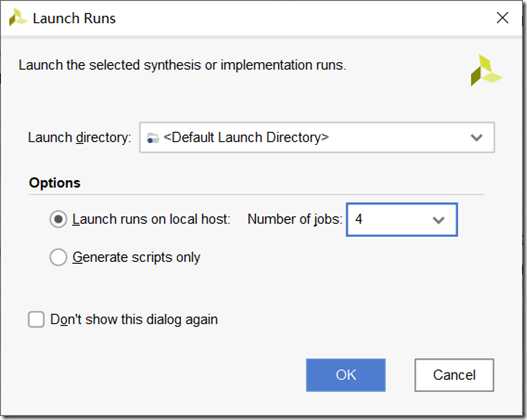

点击Run Synthesis

Number of jobs代表综合消耗的进线程。

点击OK开始综合,同时窗口右上角显示综合正在运行的提示。

综合完成后显示

5. 管脚绑定

Open Elaborated Design

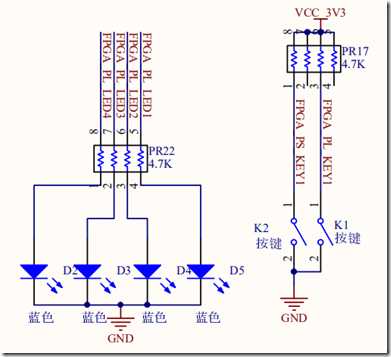

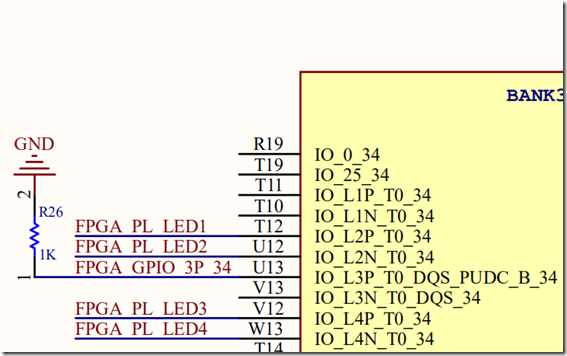

观察原理图。

LED引脚and复位按键引脚:

时钟引脚:

根据原理图绑定管脚:

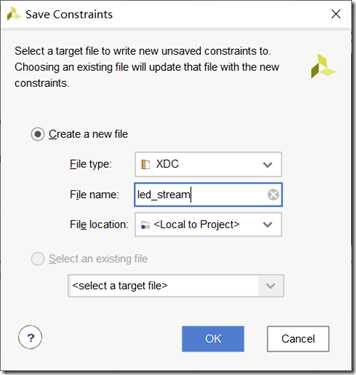

保存管脚约束文件(Ctrl+S):

6. 实现

Run Implementation

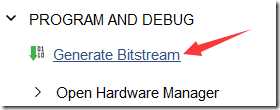

Generate Bitstream

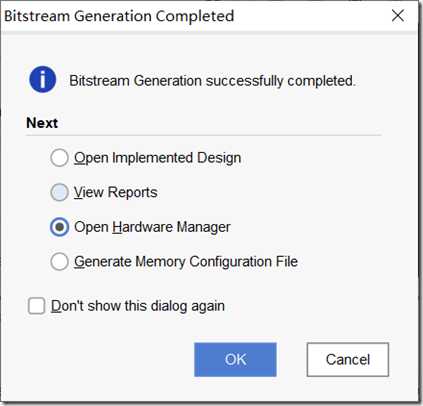

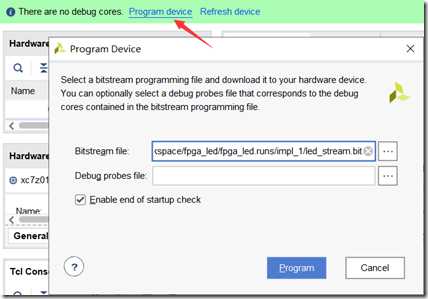

打开硬件管理器 Open Hardware Mnager:

连接ZYNQ开发板,选择Auto Connect

点击Program进行烧写操作

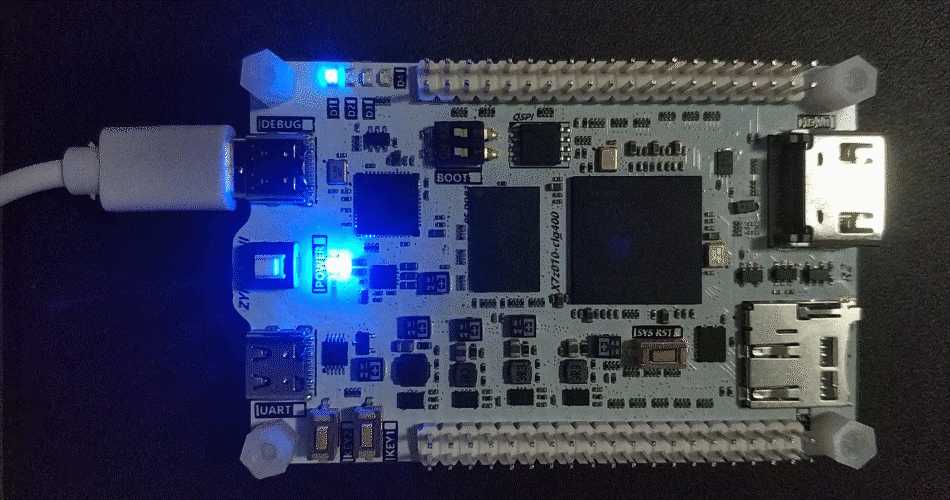

效果:

以上是关于FPGA流水灯(含Vivado使用流程)的主要内容,如果未能解决你的问题,请参考以下文章