fpga图像处理学习日记

Posted fpgamzy

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了fpga图像处理学习日记相关的知识,希望对你有一定的参考价值。

在学习有关方面之前,我还是先行的用了一天时间重新学习了一遍uart协议,我认为对uart的熟悉程度会对接下来的学习过程有一定的帮助,于是开始了对图像处理的学习,首先在找资料方面实在是难受,每次在查找资料的过程都是很痛苦的,每每不能找到我想到的东西,花了很长的功夫去四处找我要学习的东西,终于东拼西凑对VGA有了一点初步的了解

但是说实话,现在对一些名词还是没有很强的概念,比如前沿后沿,显示脉冲和同步脉冲等等,还是在参照下完成了代码

module vga_1(

input clk,

input rst_n,

output hsync,

output vsync,

output vga_r,

output vga_g,

output vga_b

);

reg [10:0] x_cnt;

reg [9:0] y_cnt;

wire valid; // 有效显示区标志

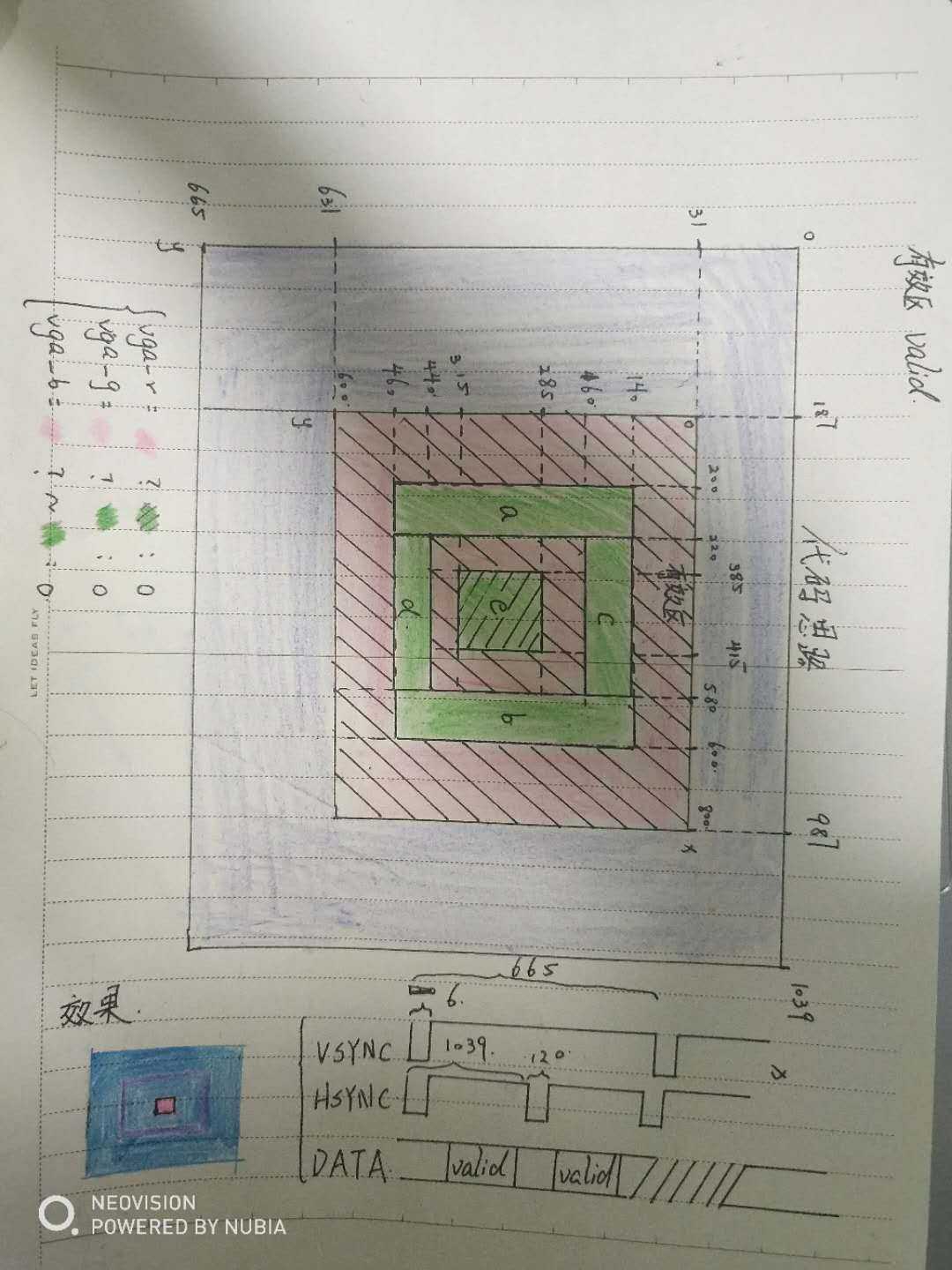

assign valid = (x_cnt >= 11‘d187) && (x_cnt < 11‘d987) && (y_cnt >= 10‘d31) && (y_cnt < 10‘d631);

wire [9:0] xpos,ypos;// 有效显示区坐标

assign xpos = x_cnt - 11‘d187;

assign ypos = y_cnt - 10‘d31;

[email protected](posedge clk or negedge rst_n)

begin

if(!rst_n)

x_cnt <= 11‘d0;

else if(x_cnt == 11‘d1039)

x_cnt <= 11‘d0;

else

x_cnt <= x_cnt + 1‘b1;

end

[email protected](posedge clk or negedge rst_n)

begin

if(!rst_n)

y_cnt <= 10‘d0;

else if(y_cnt == 10‘d665)

y_cnt <= 10‘d0;

else if(x_cnt == 11‘d1039)

y_cnt <= y_cnt + 1‘b1;

else

y_cnt <= y_cnt;

end

reg hsync_r,vsync_r;

[email protected](posedge clk or negedge rst_n)

begin

if(!rst_n)

hsync_r <= 1‘b1;

else if(x_cnt == 11‘d0)

hsync_r <= 1‘b0;

else if(x_cnt == 11‘d120)

hsync_r <= 1‘b1;

else

hsync_r <= hsync_r;

end

[email protected](posedge clk or negedge rst_n)

begin

if(!rst_n)

vsync_r <= 1‘b1;

else if(y_cnt == 10‘d0)

vsync_r <= 1‘b0;

else if(y_cnt == 10‘d6)

vsync_r <= 1‘b1;

else

vsync_r <= vsync_r;

end

assign hsync = hsync_r;

assign vsync = vsync_r;

wire a_dis,b_dis,c_dis,d_dis;

assign a_dis = ( (xpos >= 200) && (xpos <= 220) ) && ( (ypos >= 140) && (ypos <= 460) );

assign b_dis = ( (xpos >= 580) && (xpos <= 600) ) && ( (ypos >= 140) && (ypos <= 460) );

assign c_dis = ( (xpos >= 220) && (xpos <= 580) ) && ( (ypos >= 140) && (ypos <= 160) );

assign d_dis = ( (xpos >= 220) && (xpos <= 580) ) && ( (ypos >= 440) && (ypos <= 460) );

wire e_rdy;

assign e_rdy = ( (xpos >= 385) && (xpos <= 415) ) && ( (ypos >= 285) && (ypos <= 315) );

assign vga_r = valid ? e_rdy : 1‘b0;

assign vga_g = valid ? (a_dis | b_dis | c_dis | d_dis) : 1‘b0 ;

assign vga_b = valid ? ~(a_dis | b_dis | c_dis | d_dis) : 1‘b0 ;

endmodule

接下来的任务就是彻底的搞清楚整个VGA显示的工作原理以及流程了。

以上是关于fpga图像处理学习日记的主要内容,如果未能解决你的问题,请参考以下文章