FPGA初体验之用户IP核封装

Posted emmett-486

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了FPGA初体验之用户IP核封装相关的知识,希望对你有一定的参考价值。

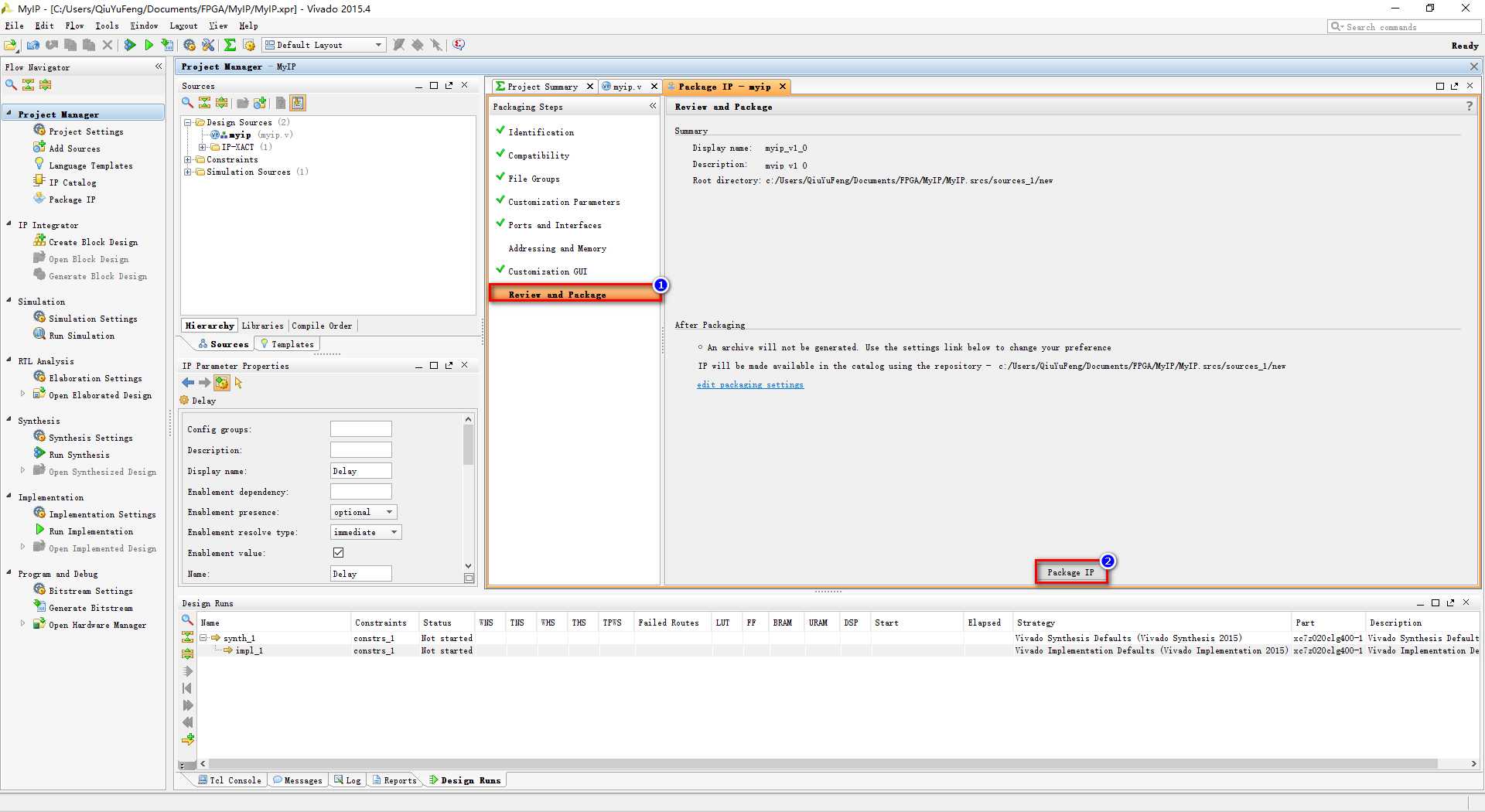

实验平台:Vivado 2015

开发板:Xilinx ZYNQ-7020

内容:创建和封装用户IP核流程

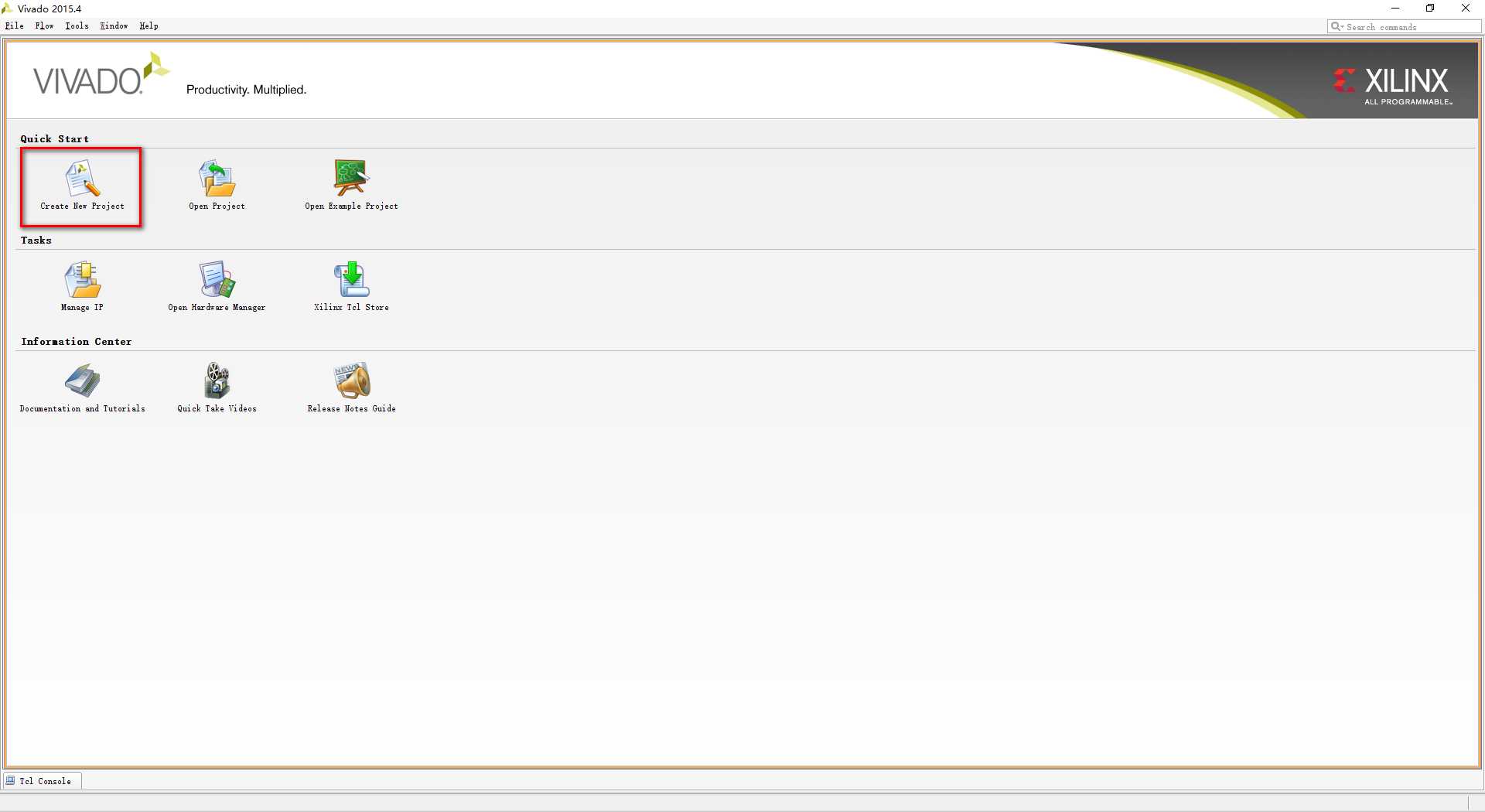

第一步:打开Vivado 2015,新建工程。

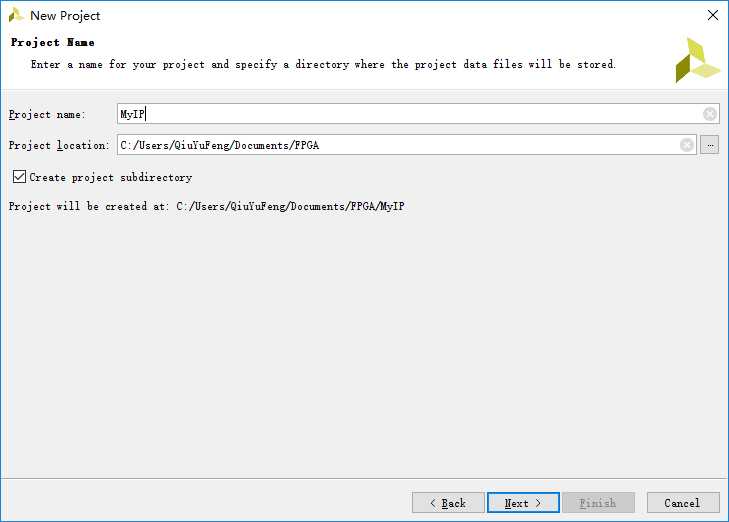

第二步:更改工程名和存放路径,点击下一步。

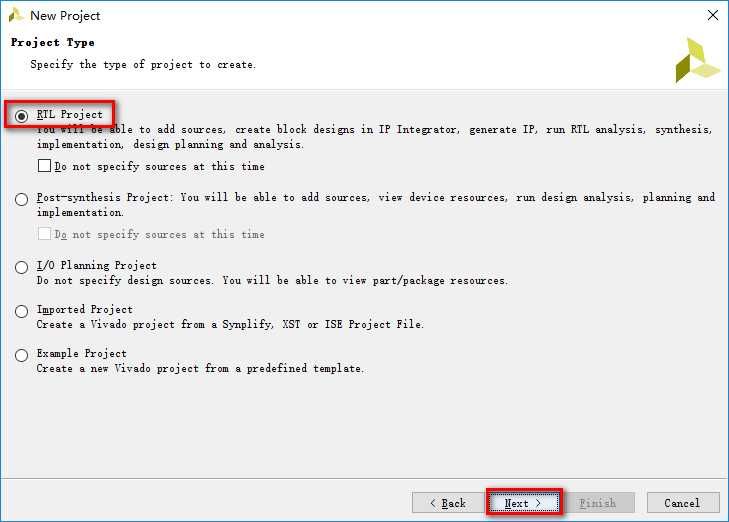

第三步:选择RTL工程,点击下一步。

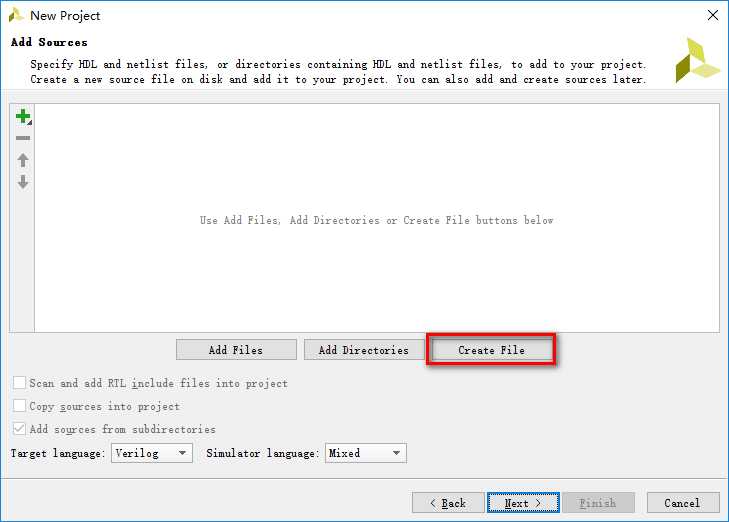

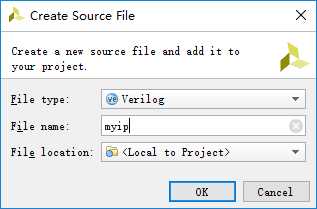

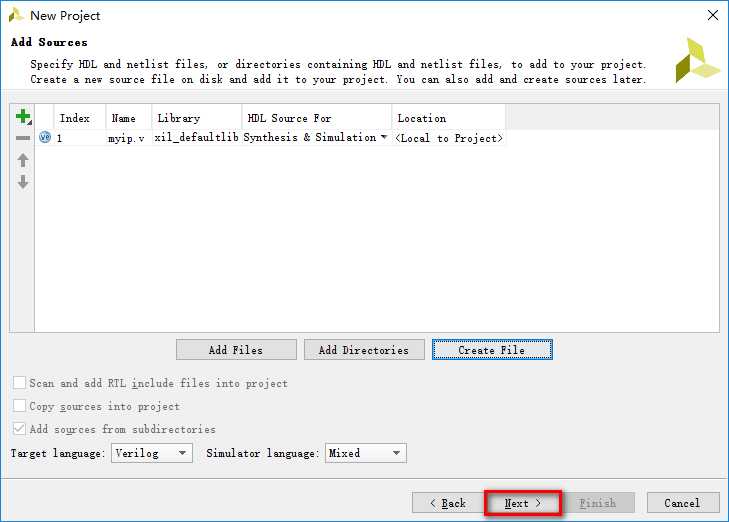

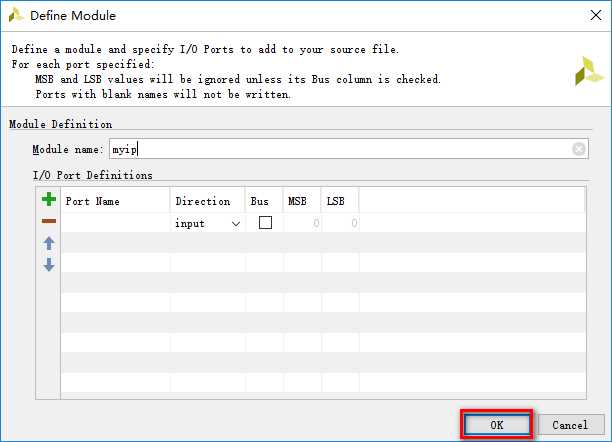

第四步:点击创建文件,输入IP核名称(自定义),点击OK。

点击下一步。

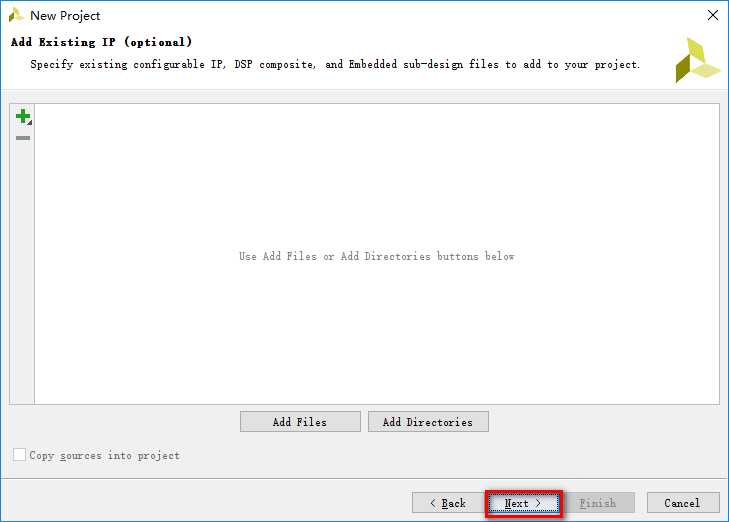

点击下一步。

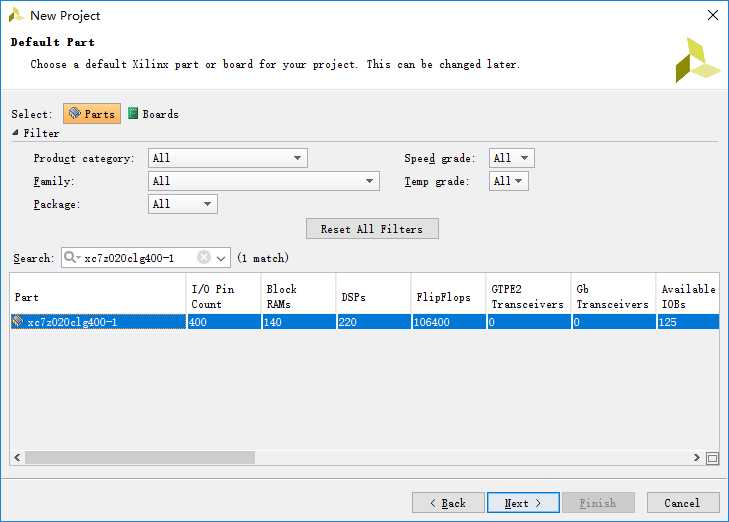

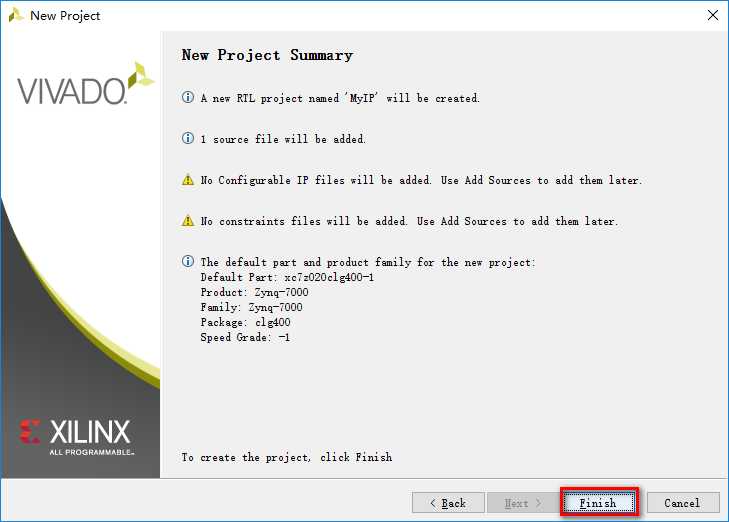

第五步:选择对应的芯片。我的开发板用的芯片是xc7z020clg-1,点击下一步。

点击完成。

直接点击OK。

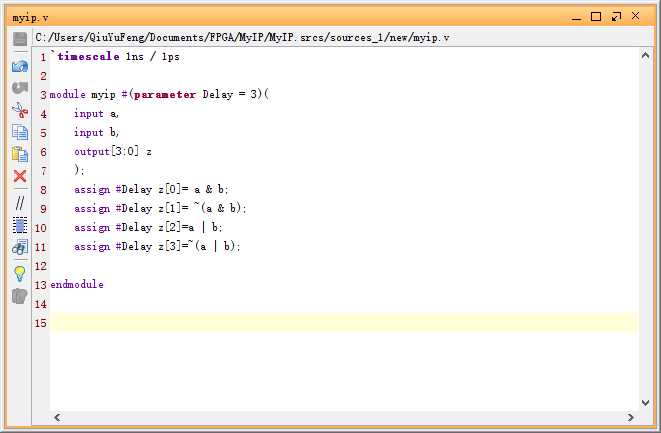

第六步:编辑myip.v

代码:myip.v

1 `timescale 1ns / 1ps 2 3 module myip #(parameter Delay = 3)( 4 input a, 5 input b, 6 output[3:0] z 7 ); 8 assign #Delay z[0]= a & b; 9 assign #Delay z[1]= ~(a & b); 10 assign #Delay z[2]=a | b; 11 assign #Delay z[3]=~(a | b); 12 13 endmodule

保存代码。

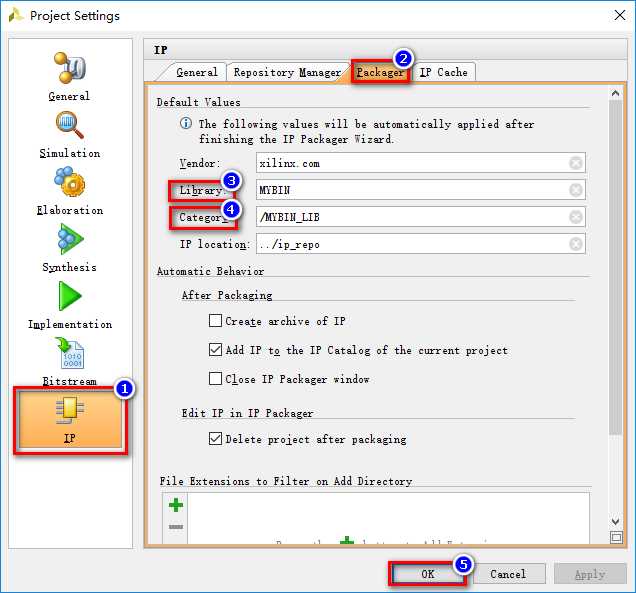

设置IP库名和目录

第一步:打开左侧导航栏中的工程设置,选择IP图标,找到Packager,设置IP库名和目录。

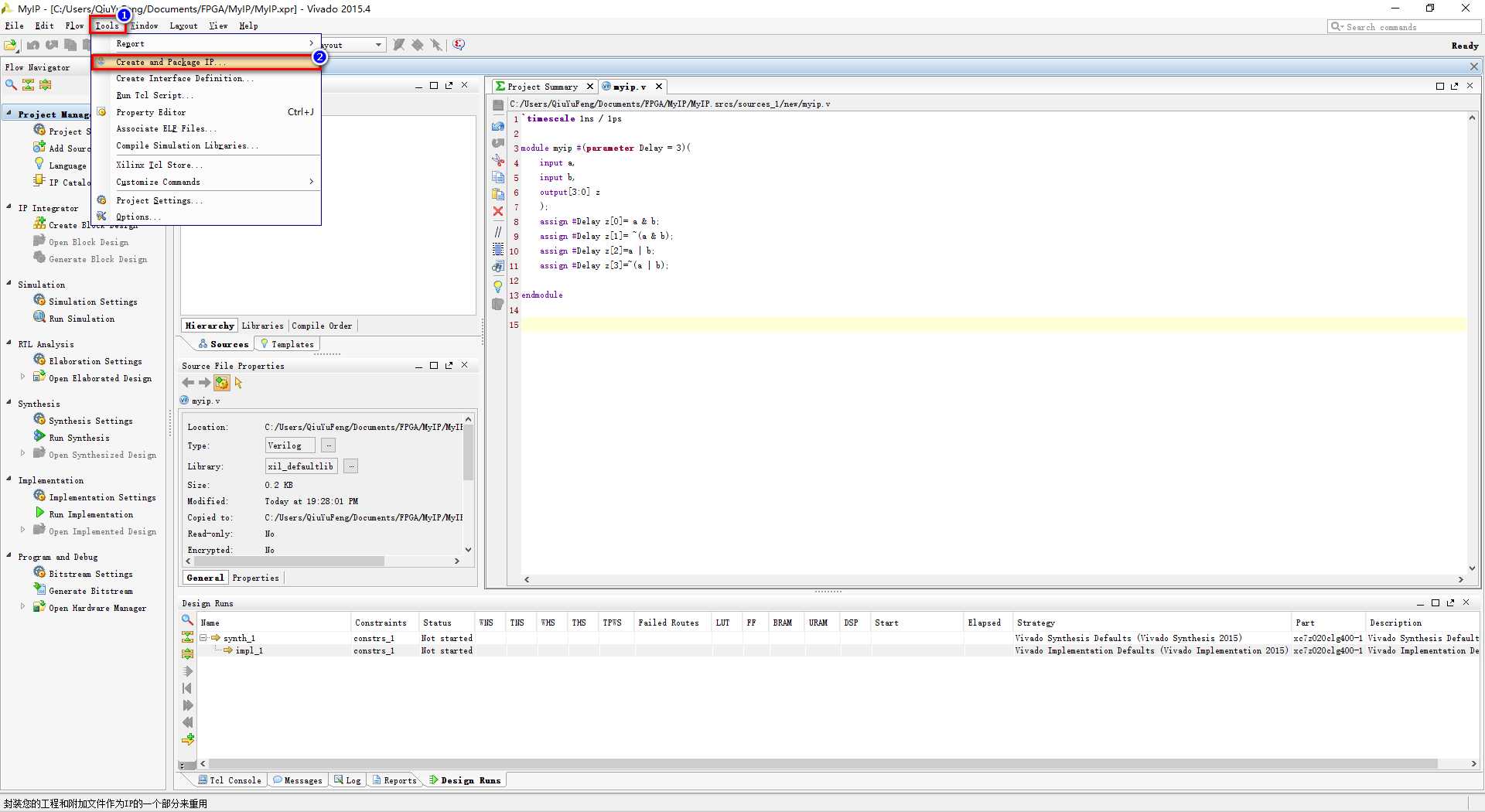

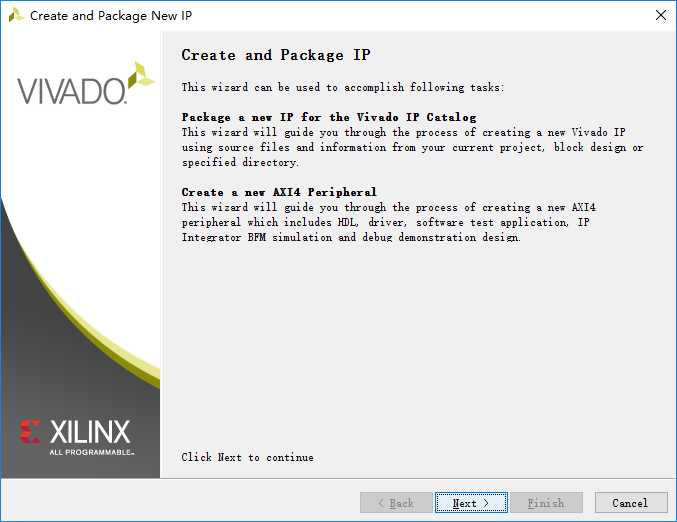

第二步:点击Tools,选择Create and Package IP...

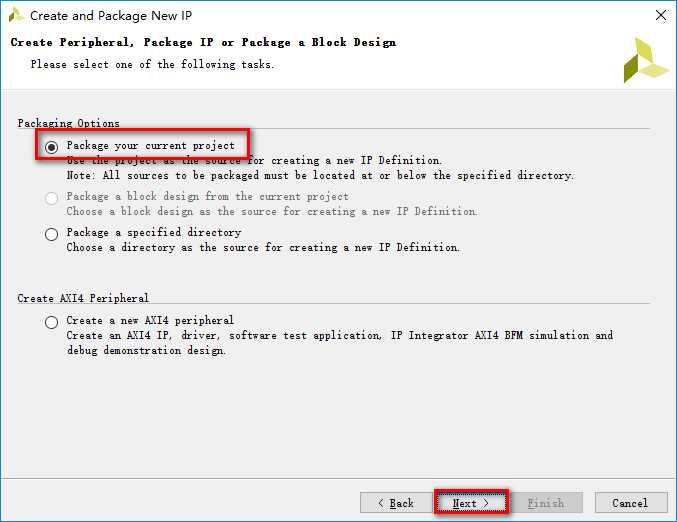

选择Package your current project,点击下一步。

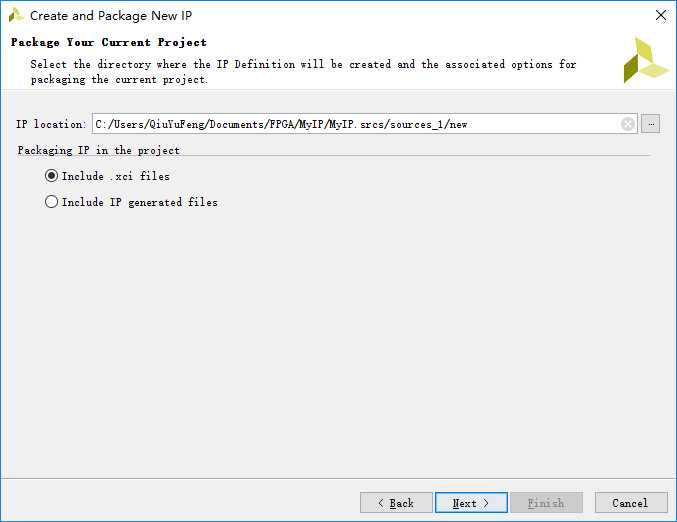

点击下一步

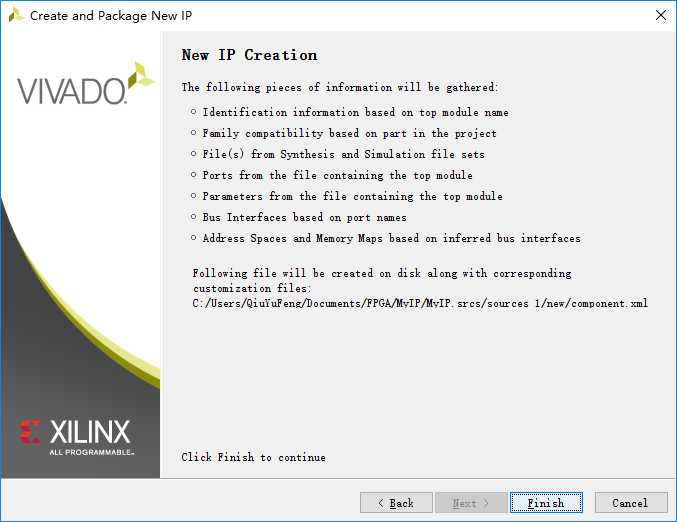

点击完成。

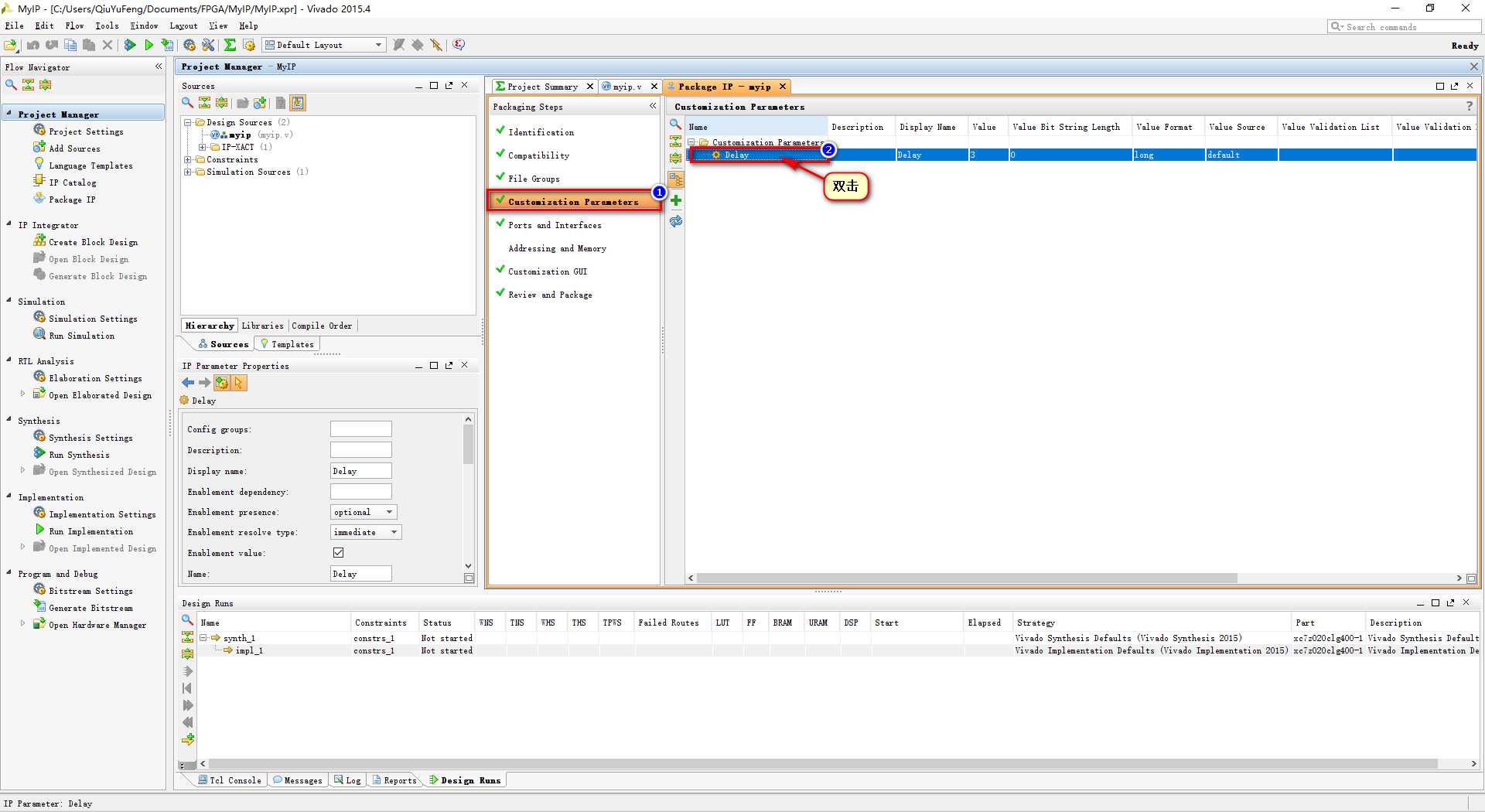

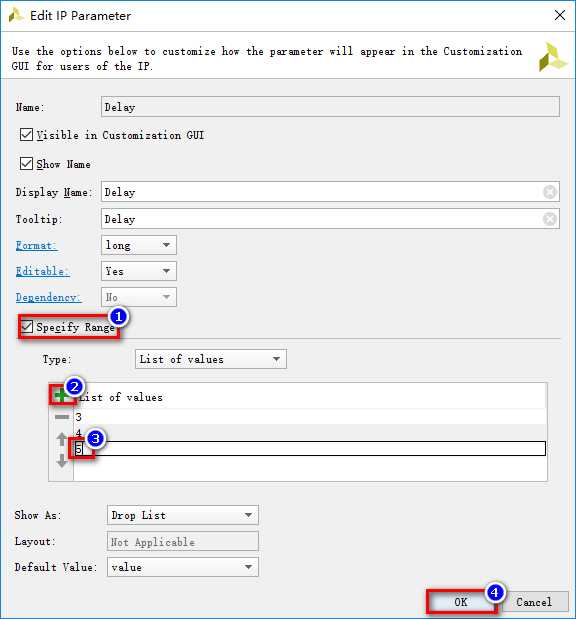

第三步:设置参数

双击需要设置的参数:

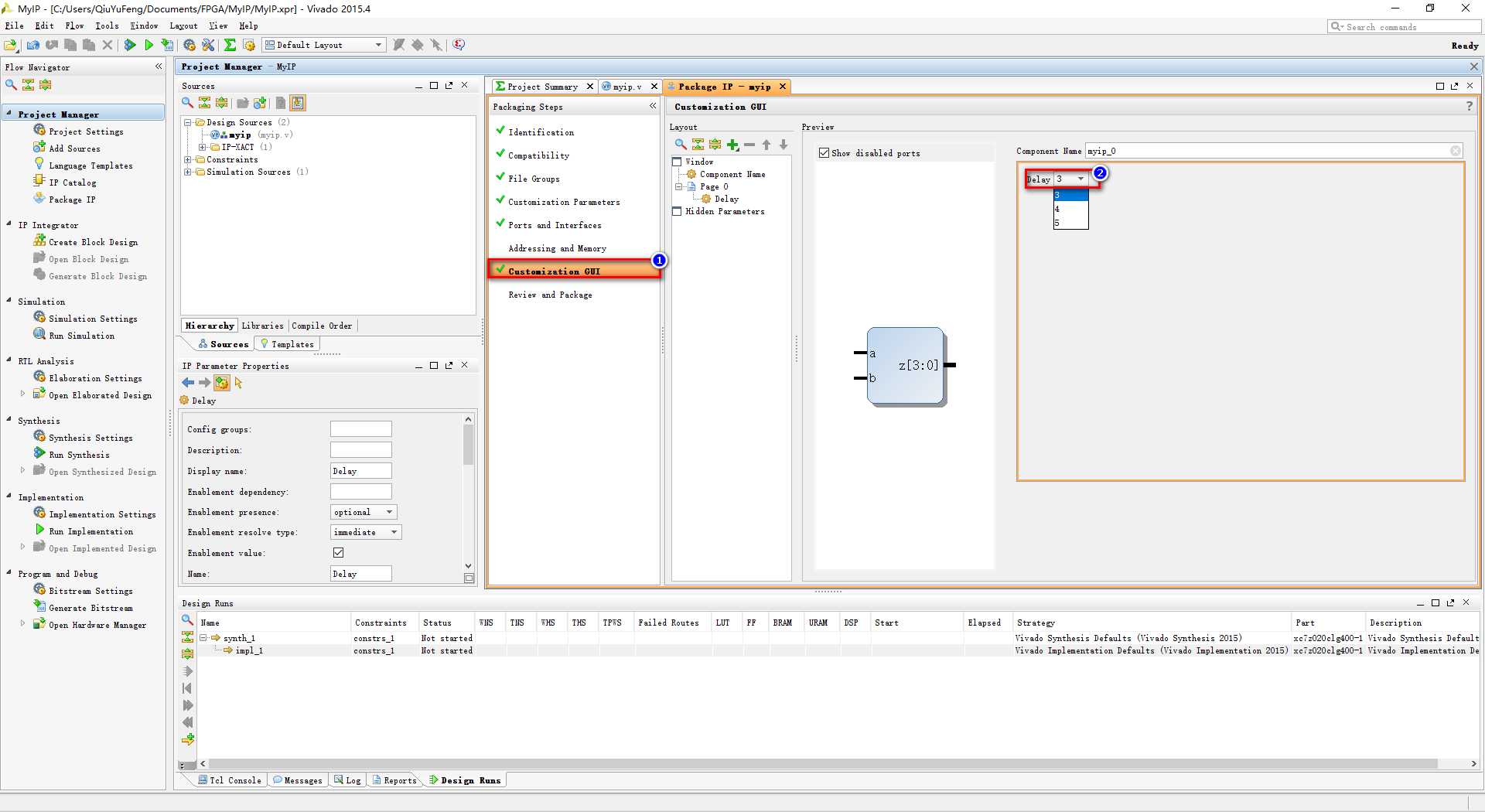

查看GUI界面,查看Delay参数。

第四步:当确认所有参数设置完成后,进行IP核封装。

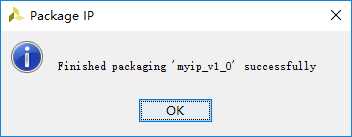

点击OK。

到此为止IP核封装完成。

以上是关于FPGA初体验之用户IP核封装的主要内容,如果未能解决你的问题,请参考以下文章

05-IP核应用之计数器——小梅哥FPGA设计思想与验证方法视频教程配套文档