测试MCU I/O和CPLD的通信(旧博客迁移)

Posted wuq-hz-zj

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了测试MCU I/O和CPLD的通信(旧博客迁移)相关的知识,希望对你有一定的参考价值。

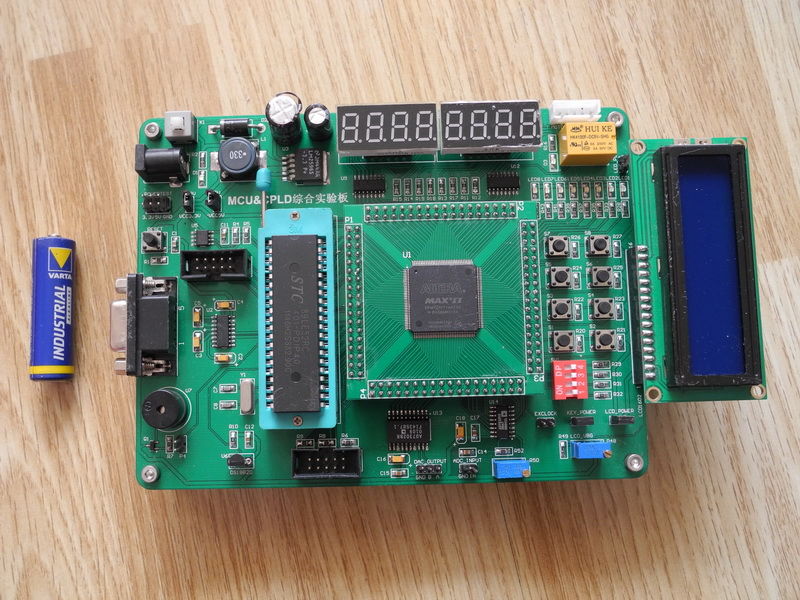

一、硬件连接

STC89LE52RC的P0[7:0]、P2[7:0]、P3[7:2]、P1[2:0]和ALE共26个信号与EPM1270相连;

另外利用CPLD外接的四位拨码开关和八个LED灯进行控制及指示;

二、测试流程

根据四位拨码开关的状态,选择P0~P3的端口值输出到LED上,用ALE作时钟同步;

三、C51 Code

#include "STC89C5xRC.h"

void main(void)

{

P0 = 0xff;

P1 = 0xff;

P2 = 0xff;

P3 = 0xff;

while (1)

{

P0 = 0x0f;

P2 = 0xf0;

P3 = 0xaa;

P1 = 0x05;

}

}

四、Verilog Code

module mcu

(

input[7:0]b_MCU_P0,

input[7:0]b_MCU_P2,

input[7:2]b_MCU_P3,

input[2:0]b_MCU_P1,

input[4:1]i_SW,

inputi_MCU_ALE,

output[8:1]o_LED

);

reg[8:1]r_LED;

always @(posedge i_MCU_ALE)

begin

case (i_SW)

4‘b0001:r_LED <= b_MCU_P0;

4‘b0010:r_LED <= b_MCU_P2;

4‘b0100:r_LED <= {b_MCU_P3, 3‘b000};

4‘b1000:r_LED <= {5‘b0_0000, b_MCU_P1};

default:r_LED <= 8‘b0000_0000;

endcase

end

assign o_LED = ~r_LED;

endmodule

五、实验现象

除了P0端口无法值无法显示,其余正常,初步判断应是没加上拉电阻引起,后续加上再测试。

六、续

P0口加4.7K上拉电阻,显示一切正常!

*有同学知道这块开发板资料的(原理图尤佳) 请联系我:)

六、续

P0口加4.7K上拉电阻,显示一切正常!

*有同学知道这块开发板资料的(原理图尤佳) 请联系我:)

以上是关于测试MCU I/O和CPLD的通信(旧博客迁移)的主要内容,如果未能解决你的问题,请参考以下文章