makefile

Posted jack-hzm

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了makefile相关的知识,希望对你有一定的参考价值。

小结

make -C make_test2/ 执行某个目录下的Makefile

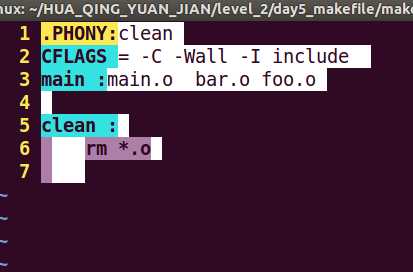

-I dir指定被包含的Makefile所在目录 ,引用某些文件的目录,例如说是 CFLAGS=-c -Wall -I include ,表示引用的引用了这个文件里面的include里面的文件

make -f Makefile_release -f 如果没有Makefile ,可以用其他名字来使用,代表这2个。

make -i ,可以忽视make中遇到的错误。如果一个项目编译的时间特变长,可以先这样子编译,如果中间有问题,也可以继续编译,然后将 有问题的 重新合成即可。

make -n ,只是看一看执行的那些命令,但是不去执行他。

make -p 显示make变量数据库和隐含规则

make -s 在执行命令的时候不显示命令

vsp.config.mk ---开启另外一个窗口了

复制代码 ,2,4 y 进行复制

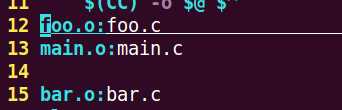

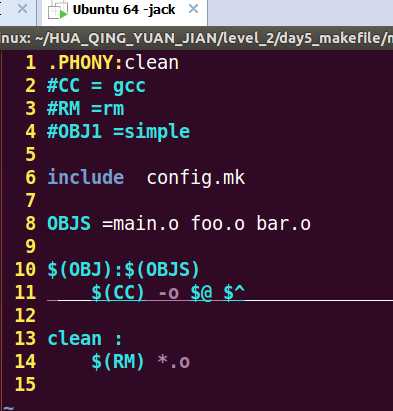

include config.mk 在另外一个文件里面加上这个。--开发板的一些可配置信息可以放到这里面做,不用再去修改了。

Makefile的隐含规则

只需要写目标文件和先决条件即可。但是如果需要的话,就添加 注意要写 CFLAGS=-c -Wall -I include

默认为

“$(CC) –c $(CPPFLAGS) $(CFLAGS)” 可以直接写的

甚至可以更简单的依赖都不用下的

继续隐含文件2看只需要 连接的文件等于他即可。

隐含规则2:链接Object文件的隐含规则 “<n>” 目标依赖于“<n>.o”,通过运行C的编译器来运行链接程序生成(一般是“ld”),其生成命令是:“$(CC) $(LDFLAGS) <n>.o $(LOADLIBES) $(LDLIBS)”。这个规则对于只有一个源文件的工程有效,同时也对多个Object文件(由不同的源文件生成)的也有效。例如如下规则: x : x.o y.o z.o 并且“x.c”、“y.c”和“z.c”都存在时,隐含规则将执行如下命令: cc -c x.c -o x.o cc -c y.c -o y.o cc -c z.c -o z.o cc x.o y.o z.o -o x 如果没有一个源文件(如上例中的x.c)和你的目标名字(如上例中的x)相关联,那么,你最好写出自己的生成规则,不然,隐含规则会报错的。

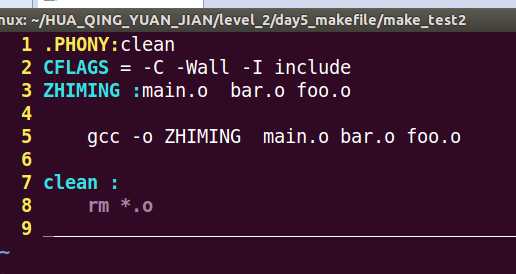

最简单的写法,不过这个目标文件,只可以是这3个其中的1个。不然就需要重新写了。

当然也可以改成如下

以上是关于makefile的主要内容,如果未能解决你的问题,请参考以下文章

使用带有 NMake 样式 Makefile 的 clang-cl 无法回显