LVDS原理及设计指南--以及衍生的B-LVDS-M-LVDS--CML-LVPECL电平等

Posted tianqiang

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了LVDS原理及设计指南--以及衍生的B-LVDS-M-LVDS--CML-LVPECL电平等相关的知识,希望对你有一定的参考价值。

LVDS是一种低摆幅的差分信号技术,它使得信号能在差分PCB 线对或平衡电缆上以

几百Mbps的速率传输,其低压幅和低电流驱动输出实现了低噪声和低功耗。

IEEE 在两个标准中对LVDS 信号进行了定义。ANSI/TIA/E IA -644 中,推荐最大速率为

655Mbps ,理论极限速率为1.923Mbps

一、LVDS组成

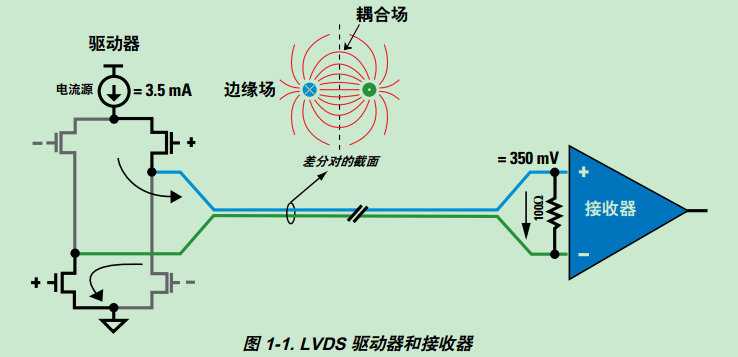

LVDS 信号传输一般由三部分组成:差分信号发送器,差分信号互联器,差分信号接收器。

差分信号发送器:将非平衡传输的TTL 信号转换成平衡传输的LVDS 信号。

差分信号接收器:将平衡传输的LVDS 信号转换成非平衡传输的TTL 信号。

差分信号互联器:包括联接线(电缆或者PCB 走线),终端匹配电阻。按照IEEE 规定 ,电阻为100 欧。我们通常选择为100 ,120 欧。

二、 LVDS信号电平特性 (电流驱动--电压接收--共模电压由0-2.4v直流偏置,典型为1.2v--差模电压:350mv由驱动电流提供-)

LVDS 物理接口使用1.2V 偏置电压作为基准(共模直流电压),提供大约350mV 摆幅(差模电压)。

LVDS 驱动器由一个驱动差分线对的电流源组成(通常电流为3.5mA),

LVD S 接收器具有很高的输入阻抗,因此驱动器输出的电流大部分都流过10 0 Ω 的匹配电阻,并在接收器的输入端产生大约350mV 的电压。

电流源为恒流特性,终端电阻在100 ――120 欧姆之间,则电压摆动幅度为:3.5mA * 100 = 350mV ;3.5mA * 120 = 420m V 。

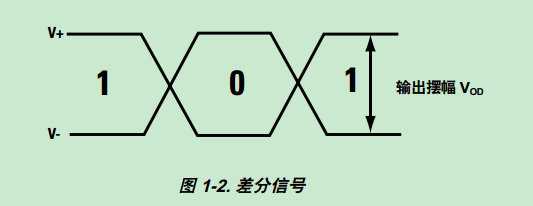

由逻辑“0 ”电平变化到逻辑“1 ”电平是需要时间的。

由于LVDS 信号物理电平变化在0 。85――1 。55V 之间,其由逻辑“0”电平到逻辑“1 ”

电平变化的时间比TTL 电平要快得多,所以LVDS 更适合用来传输高速变化信号。其低压

特点,功耗也低

三、抗干扰性:

0--1电平表示:当输出V+=350MA电流,V-=0ma电流--那么输出的为高电平(在接收端的匹配电阻转换为电压值350mv),反之为低电平

摆幅VOD=共模差值350MV

在实际线路传输中,

V+总电流=A(交流350MA)+D(直流1.2V/100=12MA)-----当然了,最主要的还是差模电压的交流信号

V-总电流=A(交流 0MA)+D(直流1.2V/100=12MA)-----当然了,最主要的还是差模电压的交流信号

差值--(在100欧姆上的电压)=[(350+12)-(0+12)]*100=0.35*100=0.35v=350mv

线路存在干扰,并且同时出现在差分线对上,

V+总电流=A(交流350MA)+D(直流1.2V/100=12MA) +G(干扰8ma)-----当然了,最主要的还是差模电压的交流信号

V-总电流=A(交流 0MA)+D(直流1.2V/100=12MA)+G(干扰8ma)-----当然了,最主要的还是差模电压的交流信号

差值--(在100欧姆上的电压)=[(350+12+8)-(0+12+8)]*100=0.35*100=0.35v=350mv(由于干扰是加在差分线上的所以相等抵消了)

噪声被抑止掉。

上述可以形象理解差分方式抑止噪声的能力。在实际芯片中,是在噪声容限内,采

用“比较”及“量化”来处理的。

LVDS 接收器可以承受至少±1V 的驱动器与接收器之间的地的电压变化。由于LVDS

驱动器典型的偏置电压为+1.2V,地的电压变化、驱动器偏置电压以及轻度耦合到的噪声之

和,在接收器的输入端相对于接收器的地是共模电压。这个共模范围是:+0.2V~+2.2 V 。

建议接收器的输入电压范围为:0V~+2.4V

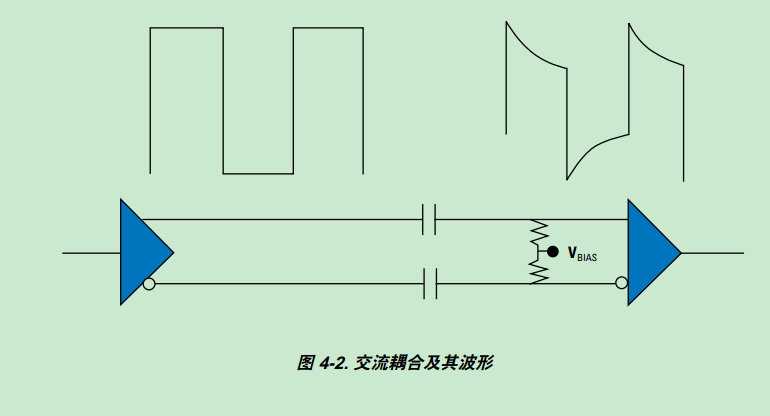

四、耦合方式---AC(交流)--DC(直流)

直流耦合方式:---耦合电容---匹配电阻--

由于在接收器的输入端相对于接收器的地是共模电压。这个共模范围是:+0.2V~+2.2 V

即:直流偏置电压要求不高:+0.2V~+2.2 V都可以---

所以--可以直接使用源端的直流偏置电压--即无论是高速低速--板间、板内-最好都使用直流耦合方式

但是当---干扰很大的板间---直流偏置不在范围内的则采用交流耦合

交流耦合方式:---耦合电容---匹配电阻--偏置电压

(要加直流偏置电压--V_BIAS,若芯片内部不提供直流偏置的话要在外面接成这个样子,而不能只是简单的匹配电阻了)

优点:

1、接收器的输入波形将以偏置电压V_BIAS为中心--这使得接收器件能在器件的最佳点工作---从而能减少抖动和改善性能

2、由于CML和LVPECL并非工业标准。因此对器件的阈值并不硬性规定。假设驱动器和接收器有可能来自不同的厂商,则交流耦合能xi

消除不同厂商的产品之间存在的任何阈值差异造成的影响

3、交流耦合能消除驱动器和接收器之间的任何直流偏置--因此,对于各种技术之间的转换非常有效

4、可以防止连个板卡或两个系统之间出现电位差

应用:总之----交流耦合一般出现在采样信号速率高和CML与LVPECL器件的应用情形中

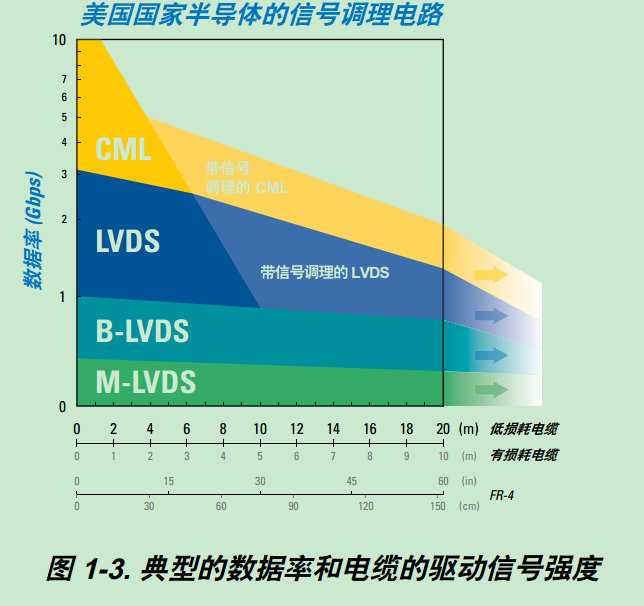

五、衍生差分信号---CML---LVPECL---M-LVDS----B_LVDS

| 工业标准 | 最高速率 | 输出摆幅 | 功耗 | ||

| LVDS | TIA/EIA-644 | 3.125Gbps | 350MV | 低 | |

| LVPECL | 无 | 10 +Gbps | 800MV | 中高 | |

| CML | 无 | 10 +Gbps | 800MV | 中 | |

| M-LVDS | TIA/EIA-899 | 250Mbps | 550MV | 低 | |

| B-LVDS | 无 | 800Mbps | 550MV | 低 |

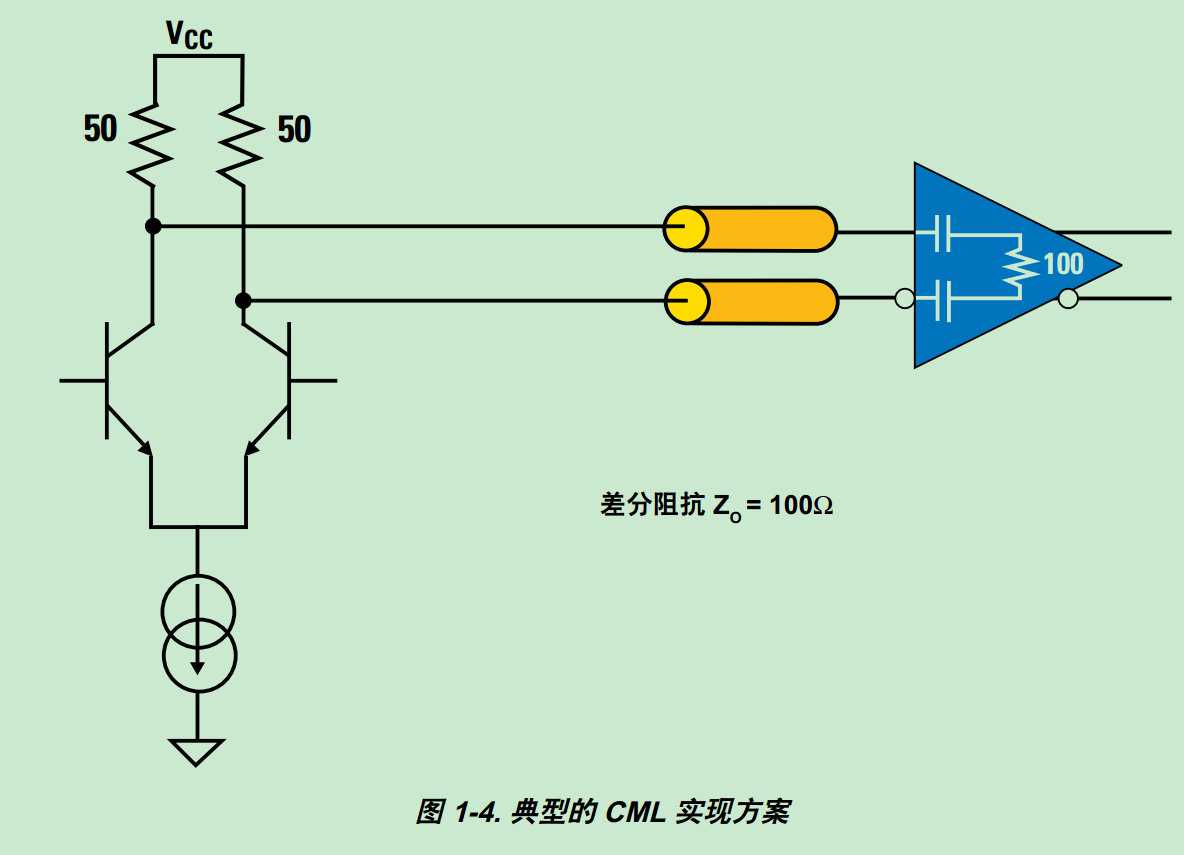

电流模式逻辑----Current-Mode Logic-------CML

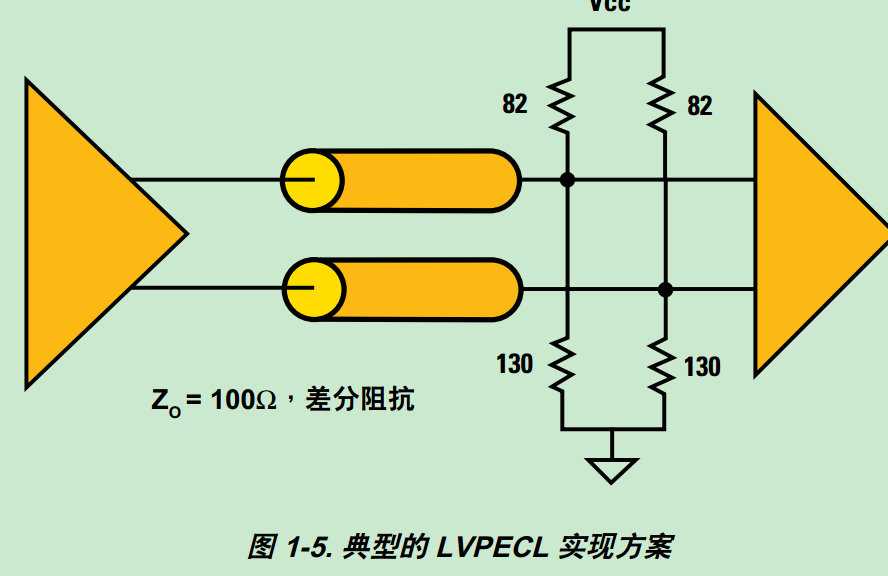

低压正发射机耦合逻辑----Low-Voltage Positive-Emitter-Coupled--LVPECL

以上两个电平标准没有正式规范化---个厂商之间的心能差异很大

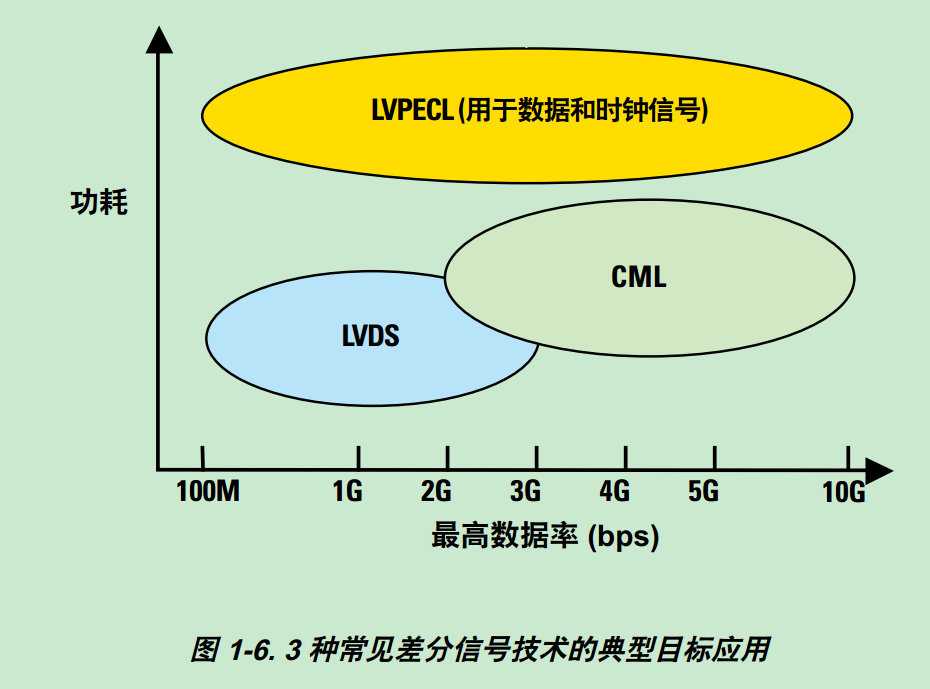

各种电平速度比较

直流偏置电压比较

功耗比较

六、LVDS-CML-LVPECL三种电平的转换

CML

LVPECL

以上是关于LVDS原理及设计指南--以及衍生的B-LVDS-M-LVDS--CML-LVPECL电平等的主要内容,如果未能解决你的问题,请参考以下文章