Chisel3-Intellij IDEA中使用sbt构建Chisel项目

Posted wjcdx

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Chisel3-Intellij IDEA中使用sbt构建Chisel项目相关的知识,希望对你有一定的参考价值。

https://mp.weixin.qq.com/s/gssjiiPW6zUzKwCFZdNduw

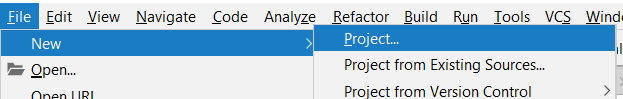

1. 使用Intellij IDEA创建Scala项目

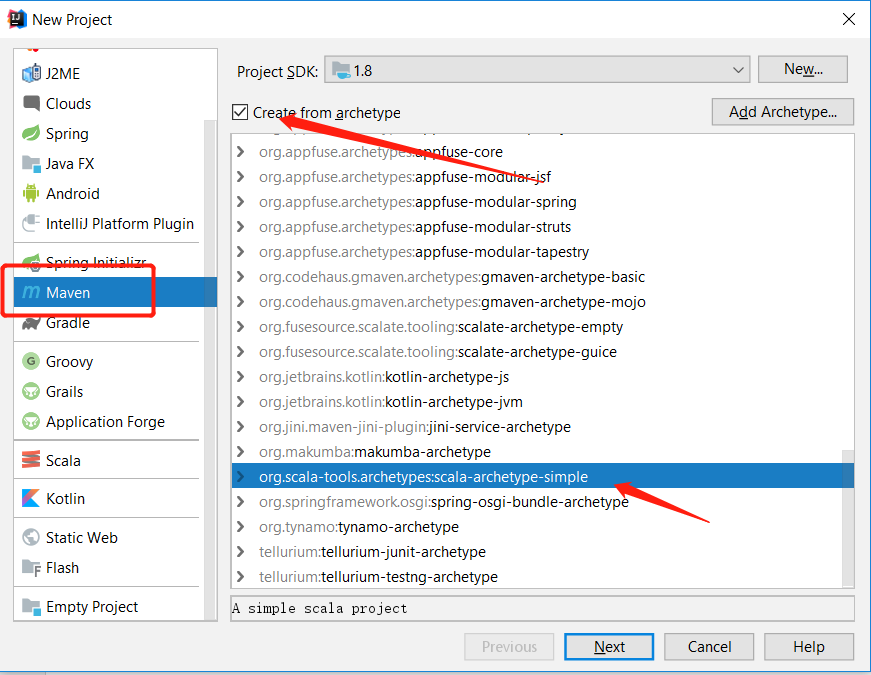

Chisel项目,就是构建Scala项目。Intellij IDEA支持使用Maven等多种方式构建Scala项目:

? ?

?

? ?

?

这里选择Maven和IDEA,都可以很方便的构建项目。尤其是使用IDEA构建项目,不需要额外的下载,直接编写Scala代码,即可完成编译运行。

很遗憾的是,Chisel3的库对sbt有依赖(比如依赖sbt生成的BuildInfo信息),无法使用其他构建方式。

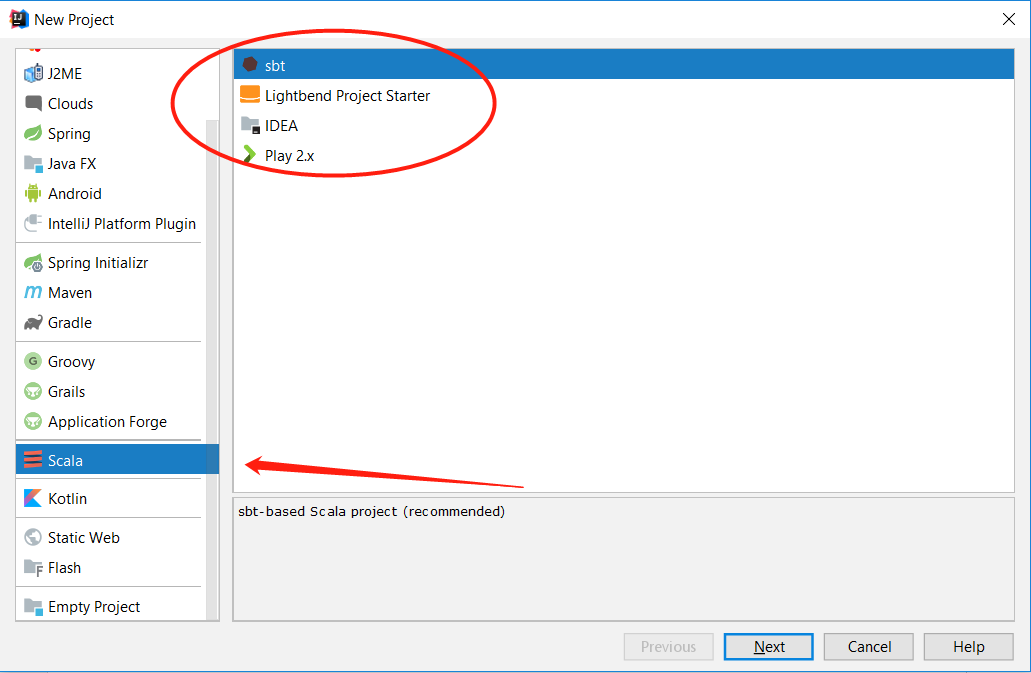

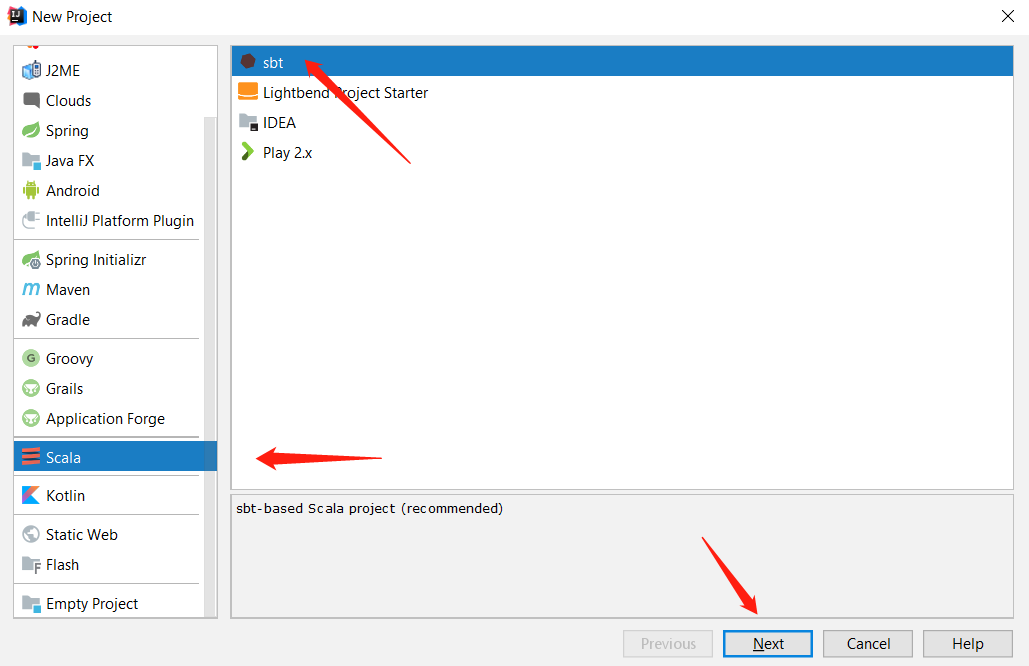

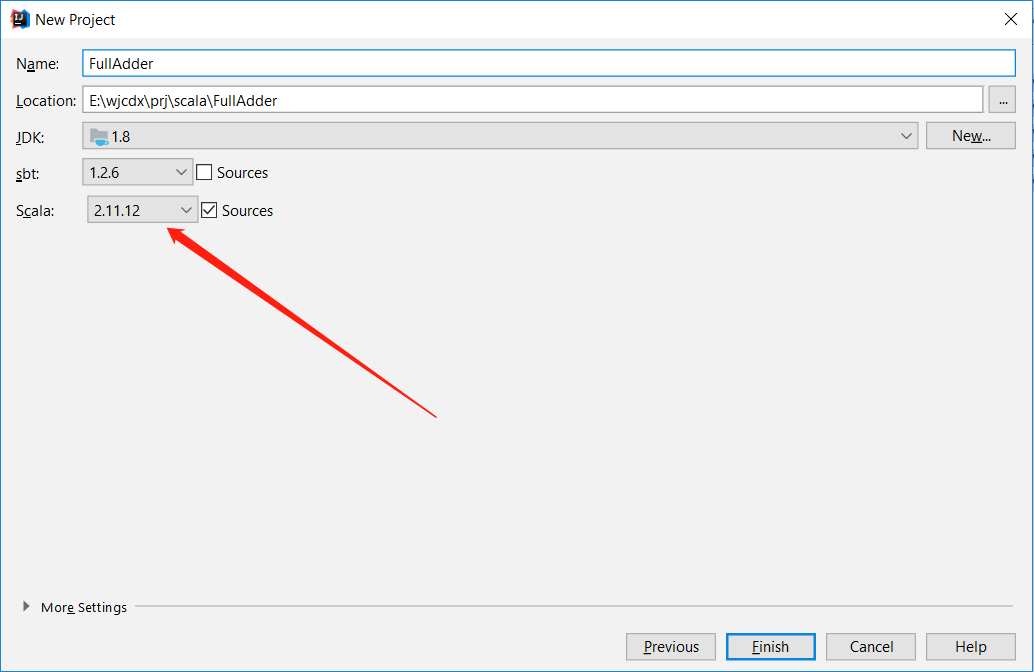

创建一个使用sbt构建的Scala项目的步骤如下:

? ?

?

? ?

?

? ?

?

需要注意的是Chisel3的库在Scala 2.12+版本上会出问题,所以这里我们选择2.11的最后一个版本2.11.12.

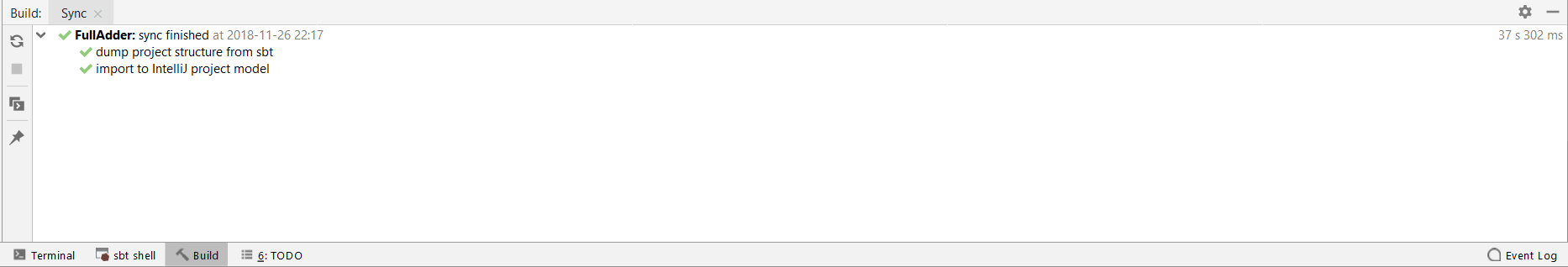

点击Finish之后,项目创建即完成,等待Intellij IDEA同步完成即可。(可能下载需要的库,需要耐心等待)

? ?

?

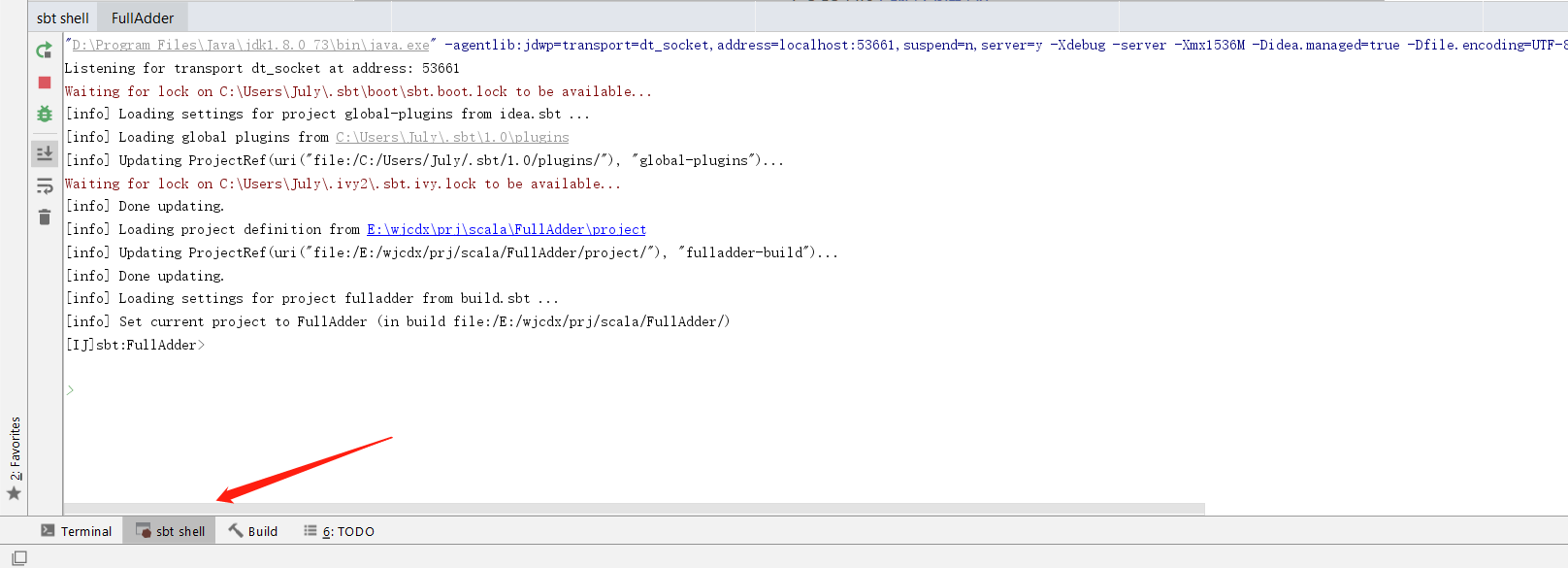

2. sbt shell窗口

点击下方的sbt shell按钮,即可打开sbt窗口。通过这个窗口可以下sbt命令。

初次打开窗口,如同执行sbt命令,加载系统以及当前项目的设置,下载需要的库之后,进入等待状态。等待用户执行构建命令。

? ?

?

? ?

?

可以通过左侧的命令按钮重启和关闭sbt shell。

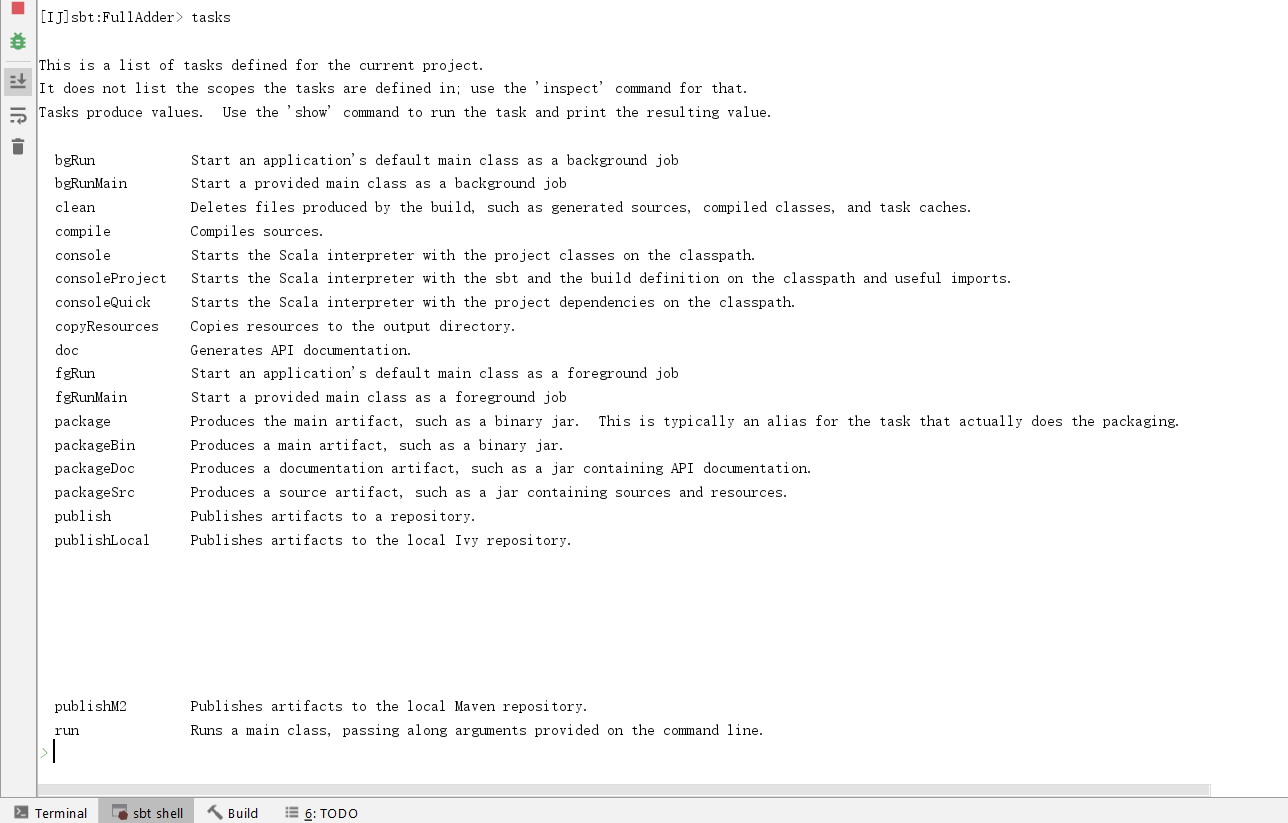

执行tasks,显示可以执行的命令:

? ?

?

这里简单介绍,其他可以自行搜索。

3. 添加chisel3库依赖

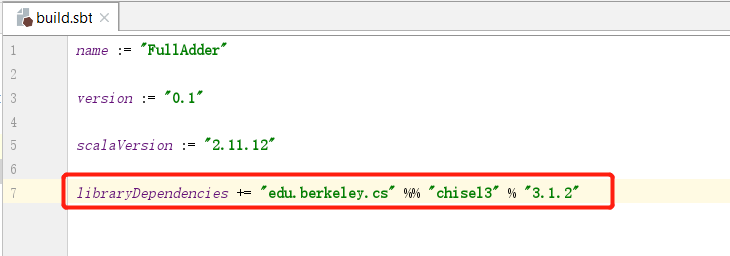

打开build.sbt,添加如下行:

libraryDependencies += "edu.berkeley.cs" %% "chisel3" % "3.1.2"

如下:

? ?

?

之后,Intellij IDEA右下角会提示,是否引入修改:

? ?

?

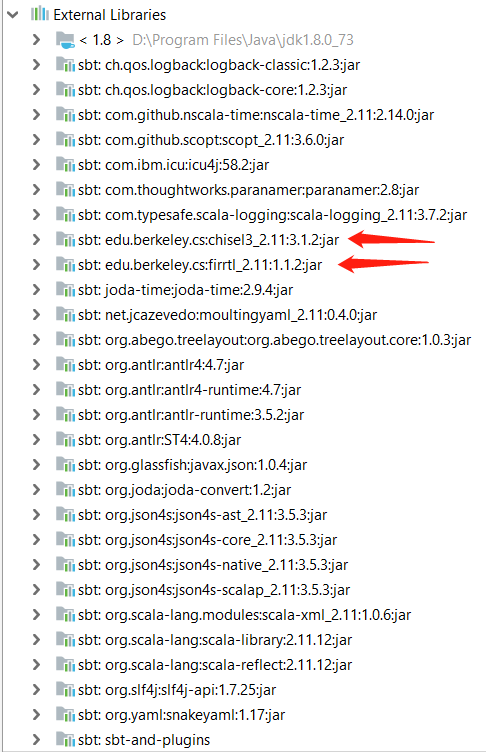

引入修改的意思是检查修改,应用修改后的配置。这次修改就是要下载需要的库,即chisel3-3.1.2.jar

可以选择Import Changes单次引入修改,也可以选择Enable Auto-Import以后每次修改build.sbt都自动引入修改。选择之后会自动下载所依赖的库。

? ?

?

PS. 猜想:也可以不理会这两个选项,直接在sbt shell中,执行update命令,或者重启sbt shell,都可以引入修改并下载所需要的库。但亲试不可行,不明就里,这里不再深究。

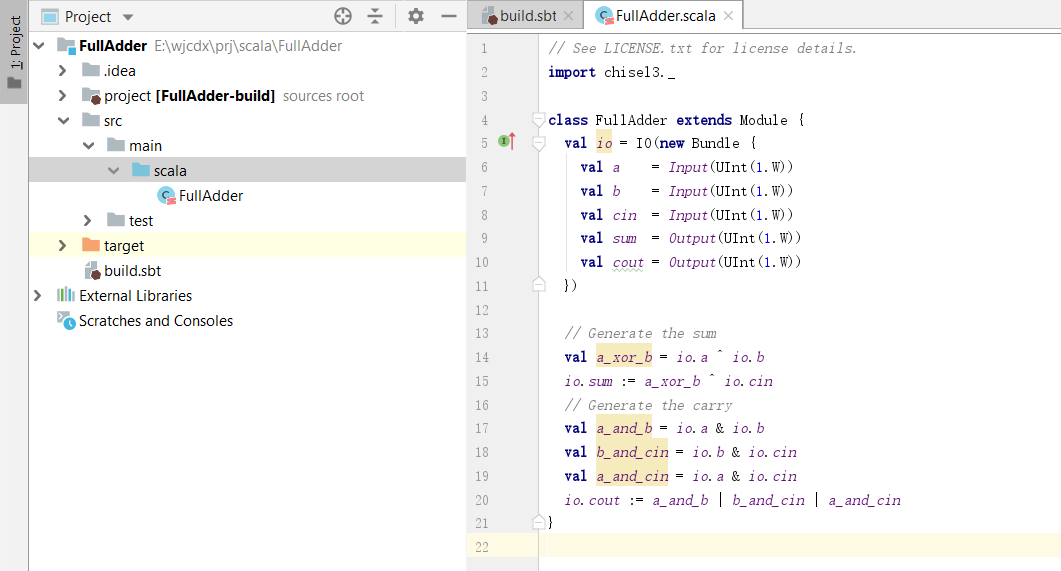

4. 添加FullAdder.scala

从chisel-tutorial中拷贝FullAdder.scala到src/main/scala目录下,

? ?

?

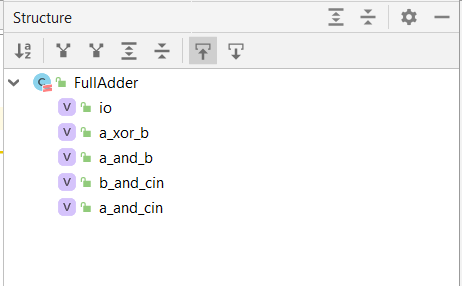

打开Structure窗口可以看到类结构:Class FullAdder,有5个Variable成员。

? ?

?

5. 测试Intellij IDEA直接构建

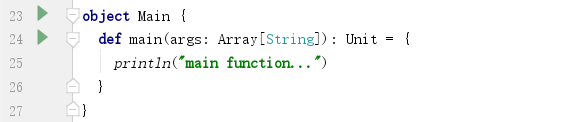

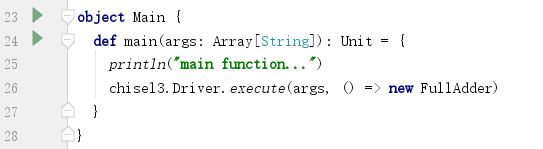

可以直接在FullAdder中添加一个Main object定义main函数,

? ?

?

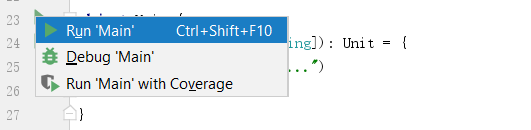

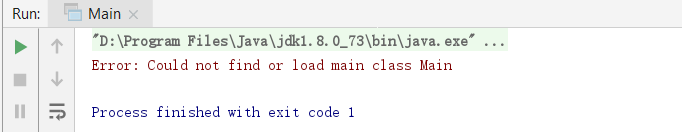

点击三角符号执行:

? ?

?

预期是能成功。但是我这边执行出错,

? ?

?

暂时不予理会。

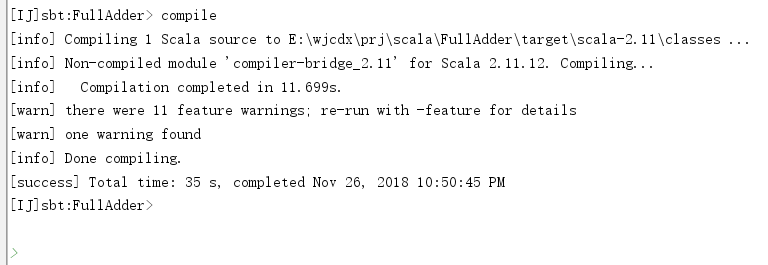

6. 使用sbt shell构建

compile:

? ?

?

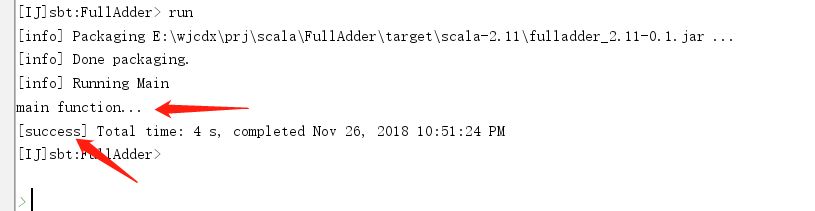

run:

? ?

?

成功了。

看来Intellij IDEA对sbt的整合,还有一些小问题。好在提供了sbt shell供使用。

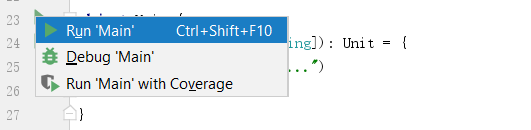

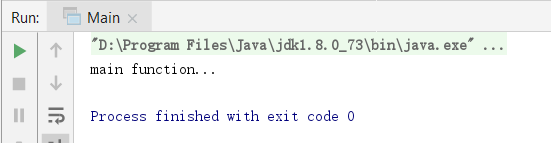

此时再次使用三角执行符号直接执行,又能成功:

? ?

?

? ?

?

可能是因为sbt shell做了一个packaging的动作。

7. 使用Chisel3 Driver

Chisel3 Driver类提供了很多功能供使用,如转换成firrtl, verilog等。

? ?

?

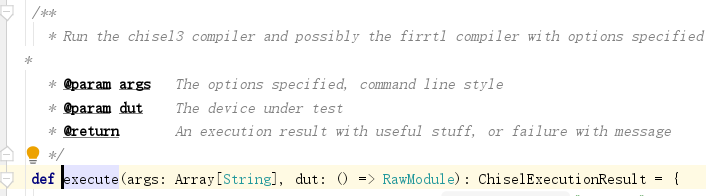

看下execute函数的签名:

? ?

?

其中args是String数组,执行时的参数。dut的类型为函数:() => RawModule,即没有参数,返回RawModule的函数。

这里我们直接把参数执行main函数时提供的参数,传递给execute函数。这样可以直接改变执行时的参数。

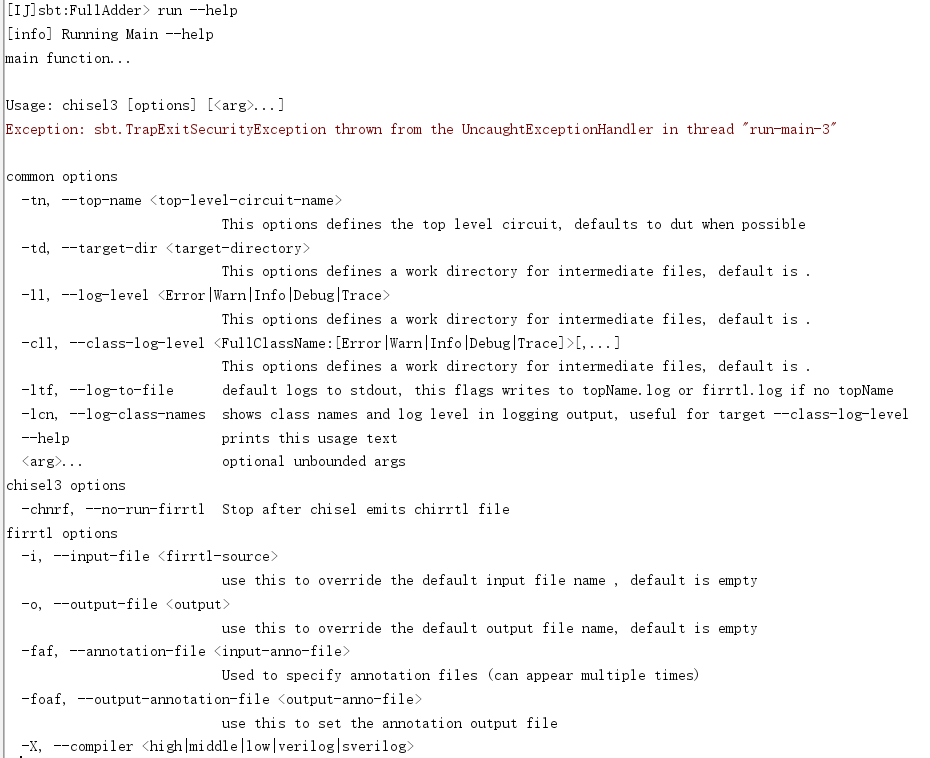

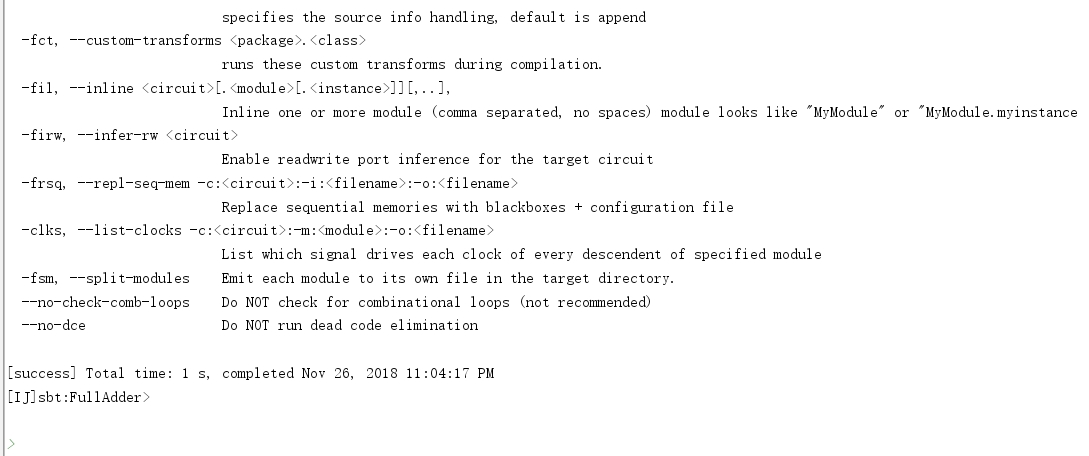

通过sbt shell执行run --help

? ?

?

? ?

?

其中-X即--compiler参数默认为verilog,即生成Verilog代码。如果选择sverilog,则生成SystemVerilog代码。

各项参数可以自行阅读。

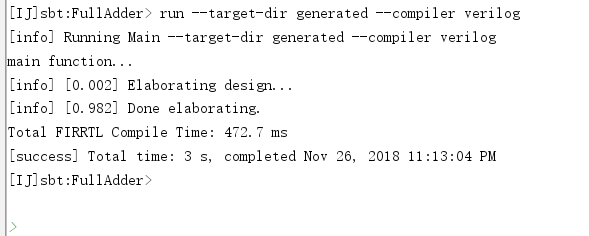

执行 --target-dir generated --compiler verilog:

? ?

?

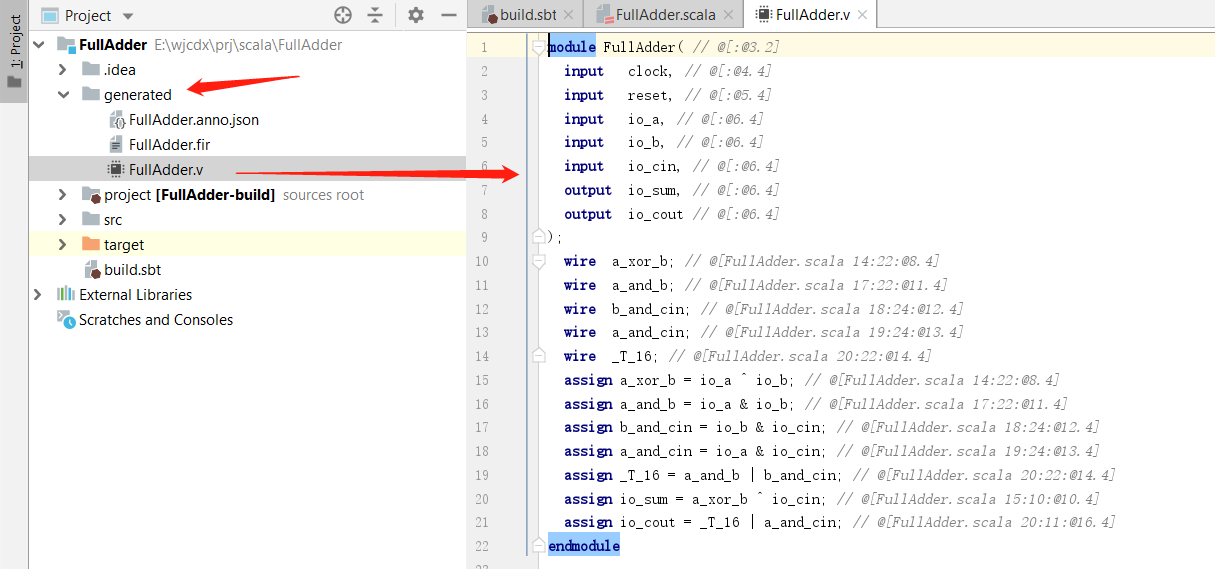

可以看到,已经生成了Verilog代码:

? ?

?

8. 附录:代码如下

(略)

以上是关于Chisel3-Intellij IDEA中使用sbt构建Chisel项目的主要内容,如果未能解决你的问题,请参考以下文章