PCB设计流程

Posted hcr1995

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了PCB设计流程相关的知识,希望对你有一定的参考价值。

基本流程:前期准备->PCB结构设计->PCB布局->布线->布线优化和丝印->网络和DRC检查和结构检查->制版。

1.前期准备

软件工具+相应的库(一定要积累,形成自己的原理图库和封装库)

元件库要求:

1.管脚属性和PCB相对应

2.简单清晰易懂

比如画芯片时在原理图上最好能看到芯片大小形状和1脚等,便于在焊接调试对照。

封装库:

尺寸要求,焊盘要比datasheet的大一点,注意常用1206 0805 0603 0402以免弄混。过孔也要大一点。

(原则上先做封装库再做原理图库)

常用封装:

SMD:surface mount devices 表面贴装

BGA:ball grid array 球形触点阵列

SIP:single in-line package 单排直插封装

DIP:dual in-line package 双排直插封装

QFP:quad flat package 四侧引脚偏平封装

四侧引脚扁平封装。引脚中心距有1.0mm、0.8mm、0.65mm、0.5mm、0.4mm、0.3mm 等多种规格。

日本将引脚中心距小于 0.65mm 的QFP称为 QFP(FP)。但现在日本电子机械工业会对QFP的

外形规格进行了重新评价。在引脚中心距上不加区别,而是根据封装本体厚度分为

QFP(2.0mm~3.6mm 厚)、LQFP(1.4mm 厚)和 TQFP(1.0mm 厚)三种。

另外,有的 LSI 厂家把引脚中心距为 0.5mm 的 QFP 专门称为收缩型 QFP 或 SQFP、VQFP。

但有的厂家把引脚中心距为 0.65mm 及 0.4mm 的 QFP 也称为 SQFP,至使名称稍有一些混

乱。

FQFP:fine pitch quad flat package 小引脚中心距 QFP,e<0.65mm

LQFP:low profile quad flat package 薄型QFP ,本体厚度=1.4mm

TQFP:本体厚度=1mm

CQFP:Ceramic Quad Flat Pack 陶瓷QFP

QFN:无引出脚封装,又称为LCC、PCLC、P-LCC等;e=1.27mm ,0.65mm ,0.5mm ,

SOP:Small Out-Line Package 小外形封装,e=1.27mm,8~44脚

SSOP:shrink small-outline package 窄间距小外形塑封,e<1.27mm,常用的e=0.65mm

TSOP:Thin Small Outline Package 微型薄片式封装,本体厚度<1.27mm

TSSOP:Thin Shrink Small Outline Package

SOJ:塑料J形线封装

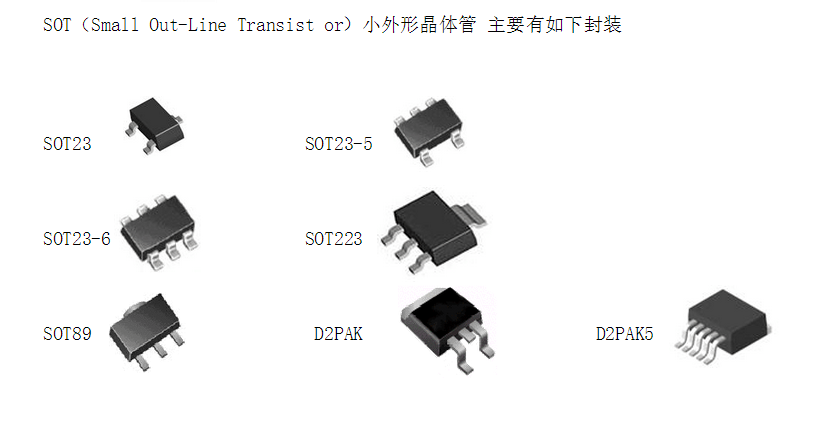

SOT:small out-line transistor 小外形晶体管,e=0.95mm

2.PCB结构设计

根据已经确定的电路板尺寸和各项机械定位,在PCB 设计环境下绘制PCB板面,并按定位要求放置所需的接插件、按键/开关、螺丝孔、装配孔等等。并充分考虑和确定布线区域和非布线区域(如螺丝孔周围多大范围属于非布线区域)。

3.PCB布局

①. 按电气性能合理分区,一般分为:数字电路区(即怕干扰、又产生干扰)、模拟电路区(怕干扰)、功率驱动区(干扰源);

②. 完成同一功能的电路,应尽量靠近放置,并调整各元器件以保证连线最为简洁;同时,调整各功能块间的相对位置使功能块间的连线最简洁;

③. 对于质量大的元器件应考虑安装位置和安装强度;发热元件应与温度敏感元件分开放置,必要时还应考虑热对流措施;

④. I/O驱动器件尽量靠近印刷板的边、靠近引出接插件;

⑤. 时钟产生器(如:晶振或钟振)要尽量靠近用到该时钟的器件;

⑥. 在每个集成电路的电源输入脚和地之间,需加一个去耦电容(一般采用高频性能好的独石电容);电路板空间较密时,也可在几个集成电路周围加一个钽电容。

钽电容的优点:容量变化受外界环境影响小,体积小,使用温度范围宽,耐高温以及寿命长,绝缘电阻高,漏电流小和容量误差小等都是钽电容所存在的优点,而且能在极其严峻在条件下工作。

独石电容:也被称之为是瓷介电容,这类电容具有容量大,体积小的优势,而且具有较强的耐高温性能。相对而言是电容类型中优点诸多的电容之一。

⑦. 继电器线圈处要加放电二极管(1N4148即可);

⑧. 布局要求要均衡,疏密有序,不能头重脚轻或一头沉

一定要考路元器件的大小封装高度相对位置,修改器件的摆放,使之整齐美观。

4.布线

布线是整个PCB设计中最重要的工序。这将直接影响着PCB板的性能好坏。

①.一般情况下,首先应对电源线和地线进行布线,以保证电路板的电气性能。在条件允许的范围内,尽量加宽电源、地线宽度,最好是地线比电源线宽,它们的关系是:地线>电源线>信号线,通常信号线宽为:0.2~0.3mm,最细宽度可达0.05~0.07mm,电源线一般为1.2~2.5mm。对数字电路的 PCB可用宽的地导线组成一个回路, 即构成一个地网来使用(模拟电路的地则不能这样使用)

②. 预先对要求比较严格的线(如高频线)进行布线,输入端与输出端的边线应避免相邻平行,以免产生反射干扰。必要时应加地线隔离,两相邻层的布线要互相垂直,平行容易产生寄生耦合。

③. 振荡器外壳接地,时钟线要尽量短,且不能引得到处都是。时钟振荡电路下面、特殊高速逻辑电路部分要加大地的面积,而不应该走其它信号线,以使周围电场趋近于零;

④. 尽可能采用45o的折线布线,不可使用90o折线,以减小高频信号的辐射;(要求高的线还要用双弧线)

⑤. 任何信号线都不要形成环路,如不可避免,环路应尽量小;信号线的过孔要尽量少;

⑥. 关键的线尽量短而粗,并在两边加上保护地。

⑦. 通过扁平电缆传送敏感信号和噪声场带信号时,要用“地线-信号-地线”的方式引出。

⑧. 关键信号应预留测试点,以方便生产和维修检测用

⑨.原理图布线完成后,应对布线进行优化;同时,经初步网络检查和DRC检查无误后,对未布线区域进行地线填充,用大面积铜层作地线用,在印制板上把没被用上的地方都与地相连接作为地线用。或是做成多层板,电源,地线各占用一层。

①. 线

一般情况下,信号线宽为0.3mm(12mil),电源线宽为0.77mm(30mil)或1.27mm(50mil);线与线之间和线与焊盘之间的距离大于等于0.33mm(13mil),实际应用中,条件允许时应考虑加大距离;

布线密度较高时,可考虑(但不建议)采用IC脚间走两根线,线的宽度为0.254mm(10mil),线间距不小于0.254mm(10mil)。特殊情况下,当器件管脚较密,宽度较窄时,可按适当减小线宽和线间距。

②. 焊盘(PAD)

焊盘(PAD)与过渡孔(VIA)的基本要求是:盘的直径比孔的直径要大于0.6mm;例如,通用插脚式电阻、电容和集成电路等,采用盘/孔尺寸 1.6mm/0.8mm(63mil/32mil),插座、插针和二极管1N4007等,采用1.8mm/1.0mm(71mil/39mil)。实际应用中,应根据实际元件的尺寸来定,有条件时,可适当加大焊盘尺寸;

PCB板上设计的元件安装孔径应比元件管脚的实际尺寸大0.2~0.4mm左右。

③. 过孔(VIA)

一般为1.27mm/0.7mm(50mil/28mil);

当布线密度较高时,过孔尺寸可适当减小,但不宜过小,可考虑采用1.0mm/0.6mm(40mil/24mil)。

④. 焊盘、线、过孔的间距要求

PAD and VIA : ≥ 0.3mm(12mil)

PAD and PAD : ≥ 0.3mm(12mil)

PAD and TRACK : ≥ 0.3mm(12mil)

TRACK and TRACK : ≥ 0.3mm(12mil)

密度较高时:

PAD and VIA : ≥ 0.254mm(10mil)

PAD and PAD : ≥ 0.254mm(10mil)

PAD and TRACK : ≥ 0.254mm(10mil)

TRACK and TRACK : ≥ 0.254mm(10mil)

5.布线优化和丝印

一般设计的经验是:优化布线的时间是初次布线的时间的两倍。感觉没什么地方需要修改之后,就可以铺铜了(Place->polygon Plane)。

6.网络的DRC检查和结构检查

首先,在确定电路原理图设计无误的前提下,将所生成的PCB网络文件与原理图网络文件进行物理连接关系的网络检查(NETCHECK),并根据输出文件结果及时对设计进行修正,以保证布线连接关系的正确性;

网络检查正确通过后,对PCB设计进行DRC检查,并根据输出文件结果及时对设计进行修正,以保证PCB布线的电气性能。最后需进一步对PCB的机械安装结构进行检查和确认。

7.制版

以上是关于PCB设计流程的主要内容,如果未能解决你的问题,请参考以下文章