jchdl - GSL实例 - Add

Posted wjcdx

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了jchdl - GSL实例 - Add相关的知识,希望对你有一定的参考价值。

使用FullAdder级联实现加法器

参考链接:

1.创建Add.java, 并生成构造方法和logic()方法

略

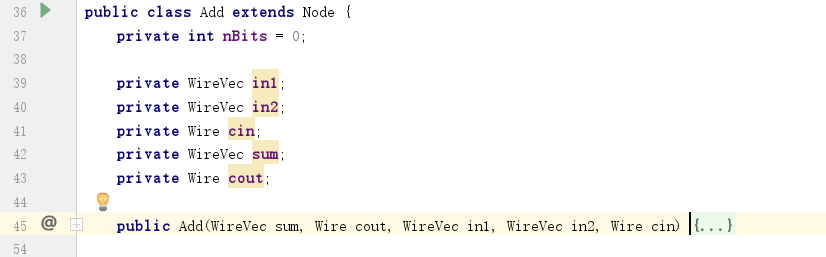

2. 根据逻辑原理图,添加输入输出线

? ?

?

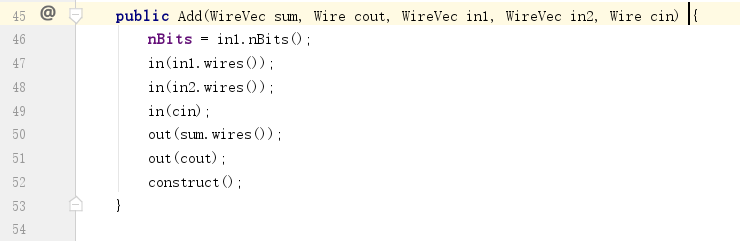

3. 在构造方法中搜集输入输出线并调用construct()方法

? ?

?

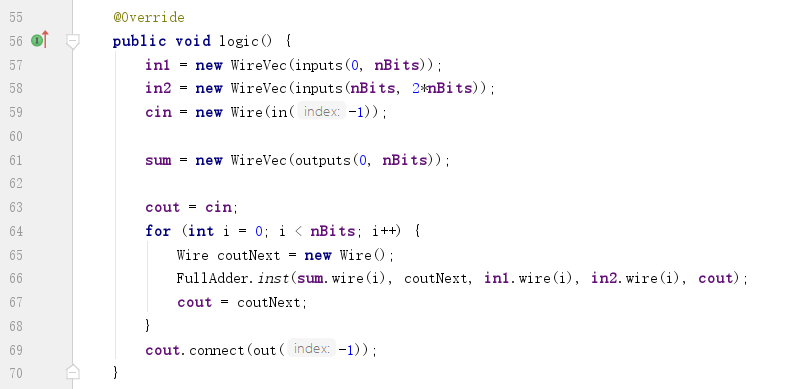

4. 在logic()方法中创建子节点并连线

? ?

?

这里首先从input ports牵出线,并创建连接到output ports的线。其中,最后一个input port使用in(-1)取出。最后一个output port使用out(-1)取出。

cout作为一个游标,逐次指向每一级的进位线进行连接。最开始为cin,第一级之后代表这一级FullAdder的进位线...直到最后,代表最后一个进位线连接到Add节点的最后一个output port.

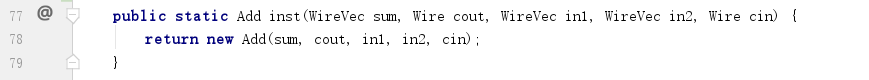

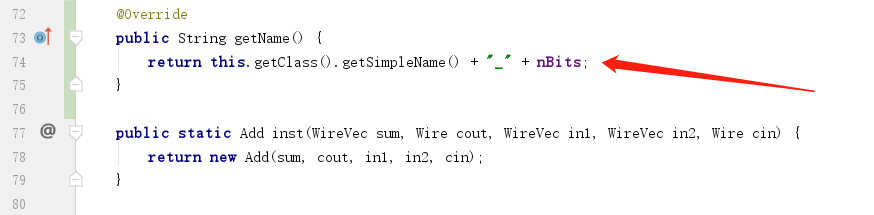

5. 创建inst静态方法方便后续使用

? ?

?

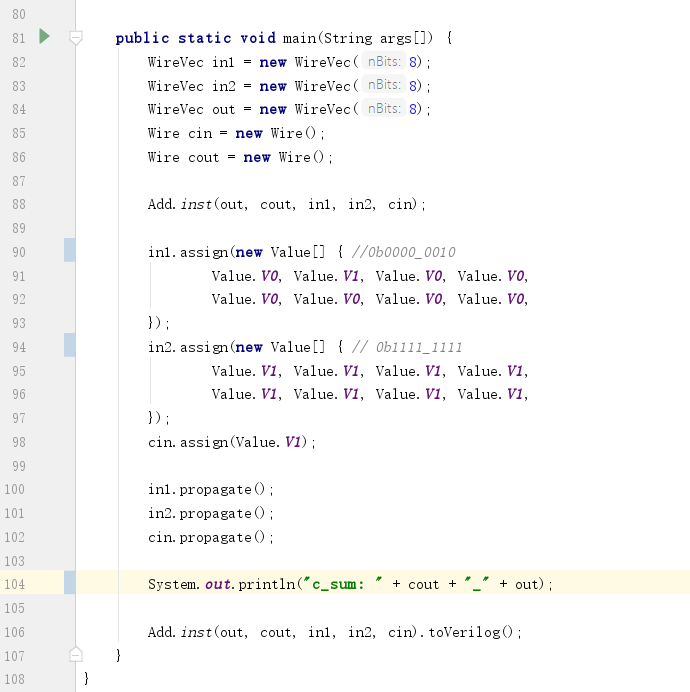

6. 创建main方法执行验证

? ?

?

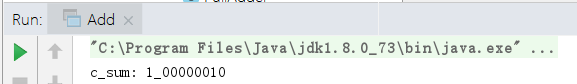

运行结果为:

? ?

?

? ?

?

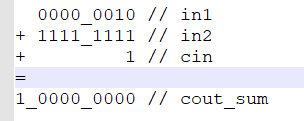

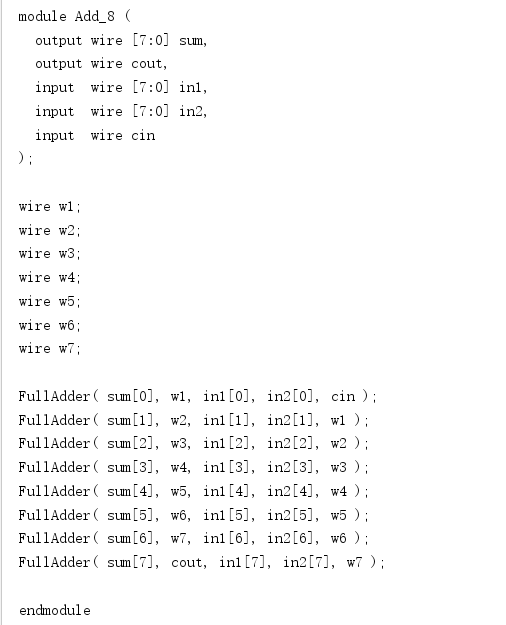

7. 生成Verilog

? ?

?

执行结果如下:

? ?

?

? ?

?

module Add_8后面多出来一个8?这样就可以把不同位宽的Add模块区分开来。

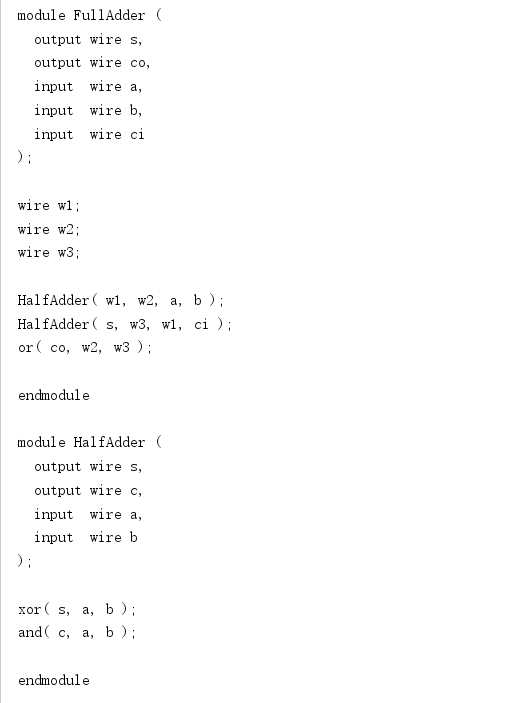

需要覆盖getName()方法:

? ?

?

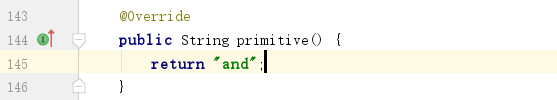

原子节点需要覆盖primitive()方法,以返回原语的名称。比如与门,需要返回and:

? ?

?

更多实例请参考如下链接:

package org.jchdl.model.gsl.operator.arithmetic;

import org.jchdl.model.gsl.core.datatype.helper.WireVec;

import org.jchdl.model.gsl.core.datatype.net.Wire;

import org.jchdl.model.gsl.core.meta.Node;

import org.jchdl.model.gsl.core.value.Value;

// treat operands as plain bits

public class Add extends Node {

private int nBits = 0;

private WireVec in1;

private WireVec in2;

private Wire cin;

private WireVec sum;

private Wire cout;

public Add(WireVec sum, Wire cout, WireVec in1, WireVec in2, Wire cin) {

nBits = in1.nBits();

in(in1.wires());

in(in2.wires());

in(cin);

out(sum.wires());

out(cout);

construct();

}

@Override

public void logic() {

in1 = new WireVec(inputs(0, nBits));

in2 = new WireVec(inputs(nBits, 2*nBits));

cin = new Wire(in(-1));

sum = new WireVec(outputs(0, nBits));

cout = cin;

for (int i = 0; i < nBits; i++) {

Wire coutNext = new Wire();

FullAdder.inst(sum.wire(i), coutNext, in1.wire(i), in2.wire(i), cout);

cout = coutNext;

}

cout.connect(out(-1));

}

@Override

public String getName() {

return this.getClass().getSimpleName() + "_" + nBits;

}

public static Add inst(WireVec sum, Wire cout, WireVec in1, WireVec in2, Wire cin) {

return new Add(sum, cout, in1, in2, cin);

}

public static void main(String args[]) {

WireVec in1 = new WireVec(8);

WireVec in2 = new WireVec(8);

WireVec out = new WireVec(8);

Wire cin = new Wire();

Wire cout = new Wire();

Add.inst(out, cout, in1, in2, cin);

in1.assign(new Value[] { //0b0000_0010

Value.V0, Value.V1, Value.V0, Value.V0,

Value.V0, Value.V0, Value.V0, Value.V0,

});

in2.assign(new Value[] { // 0b1111_1111

Value.V1, Value.V1, Value.V1, Value.V1,

Value.V1, Value.V1, Value.V1, Value.V1,

});

cin.assign(Value.V1);

in1.propagate();

in2.propagate();

cin.propagate();

System.out.println("c_sum: " + cout + "_" + out);

Add.inst(out, cout, in1, in2, cin).toVerilog();

}

}

以上是关于jchdl - GSL实例 - Add的主要内容,如果未能解决你的问题,请参考以下文章