Chisel3-创建工程并转换为Verilog代码

Posted wjcdx

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Chisel3-创建工程并转换为Verilog代码相关的知识,希望对你有一定的参考价值。

基于Intellj IDEA+Scala插件模式开发

因为Chisel内嵌于Scala,所以Chisel3的项目实际上是Scala的项目,构建使用sbt。

下面使用官方网站上面的例子Adder,创建第一个项目,并转换成Verilog语言的实现。

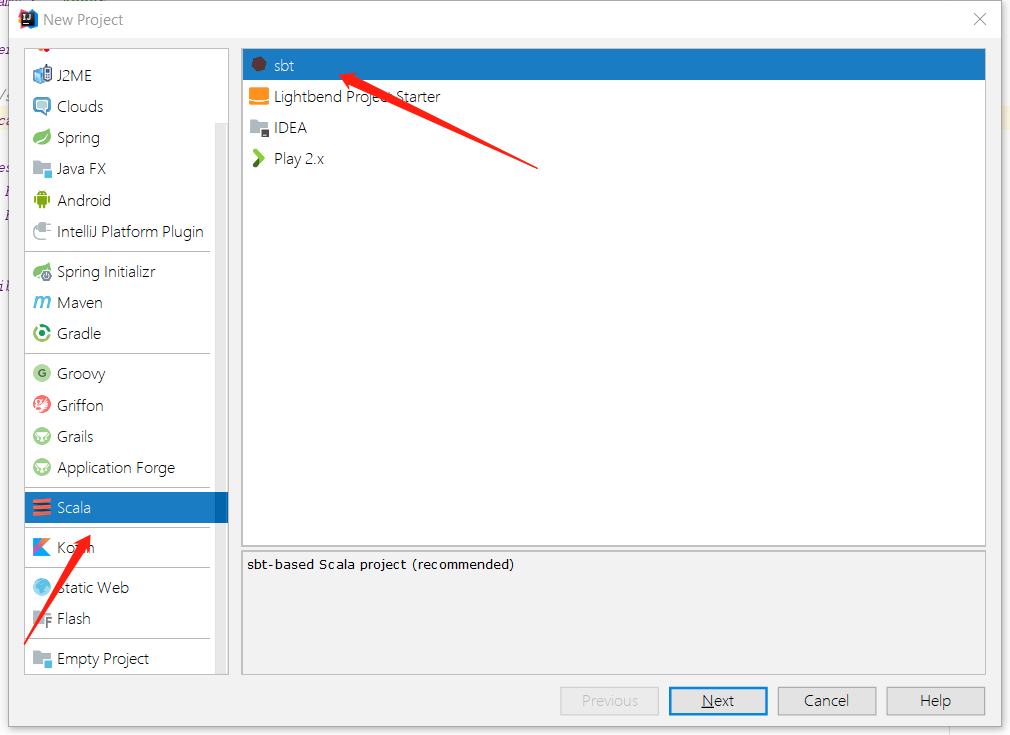

一. 创建一个基于Scala的项目

? ?

?

选择项目的存储位置,JDK, sbt和Scala的版本。版本之所以重要,是因为版本之间的差异很大,并且会引入Bug,所以不建议使用最新的Scala版本(2.12版本的会出现Bug,该Bug与Scala有关,与Chisel无关)。

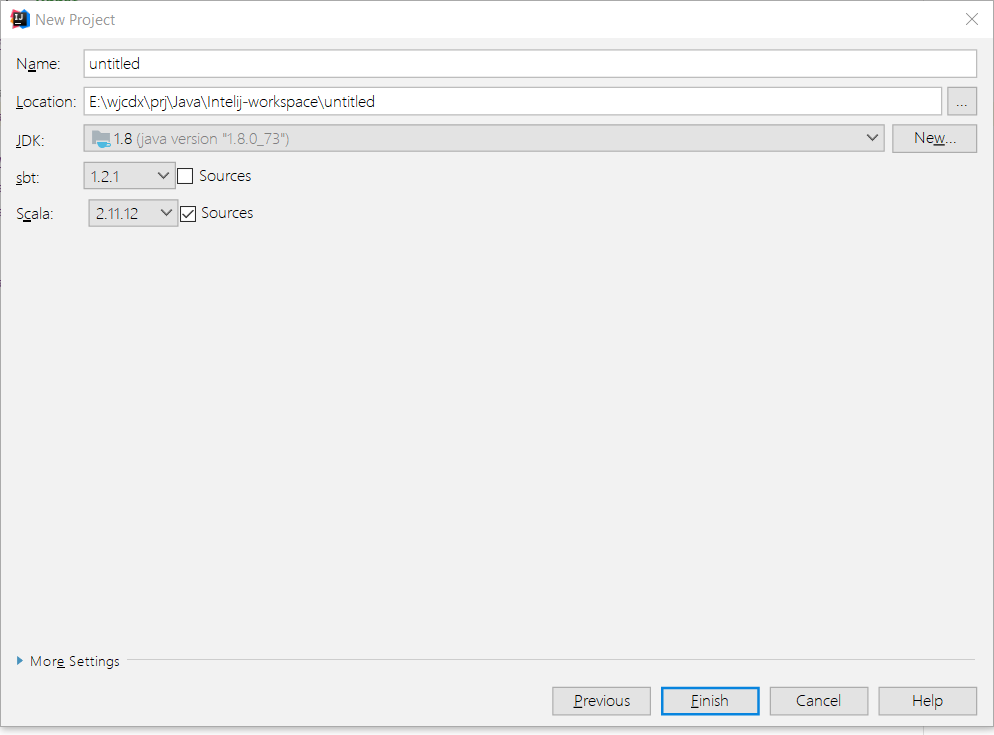

? ?

?

点击Finish之后,创建出一个Scala项目。

? ?

?

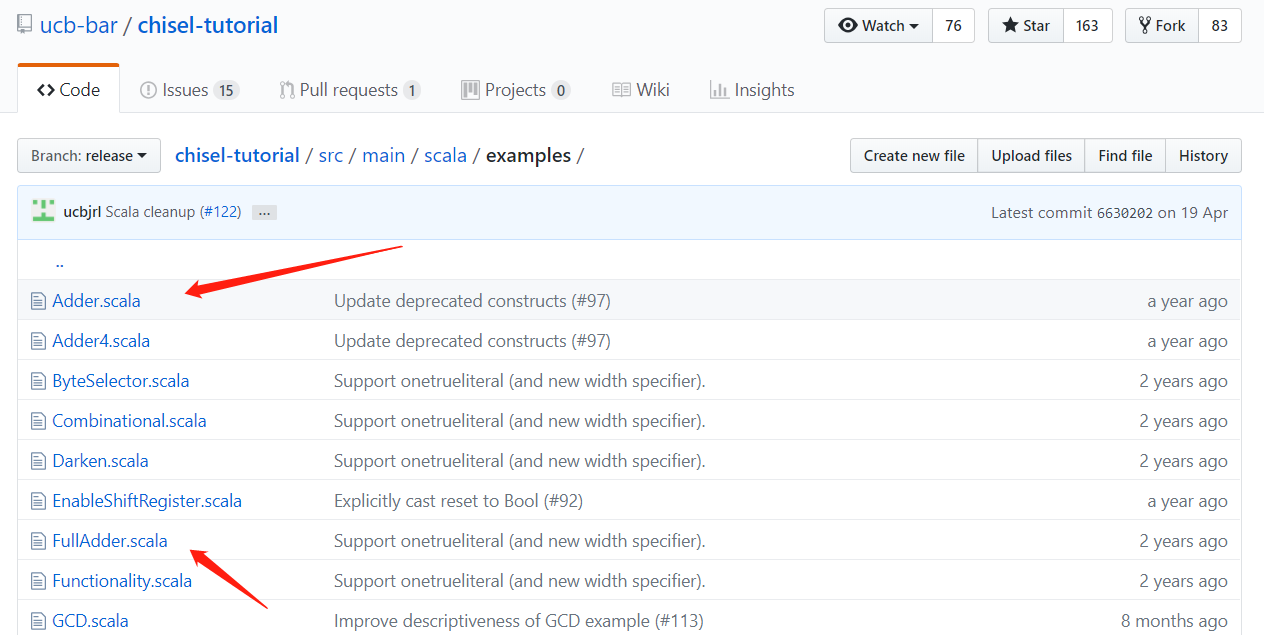

二. 添加chisel3的库

打开build.sbt文件,添加chisel3的库引用,添加之后如下:

name := "Adder"

version := "0.1"

scalaVersion := "2.11.12"

resolvers ++= Seq(

Resolver.sonatypeRepo("snapshots"),

Resolver.sonatypeRepo("releases")

)

libraryDependencies += "edu.berkeley.cs" %% "chisel3" % "3.1.2"

修改build.sbt之后,会自动同步下载chisel3相关的库。

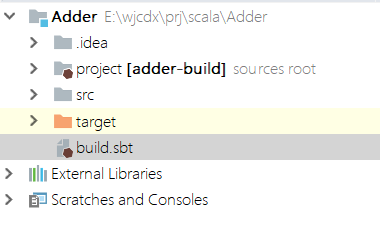

三. 添加代码文件

? ?

?

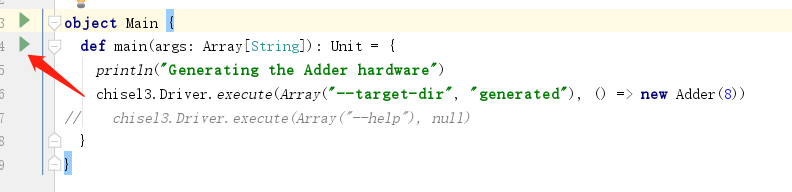

四. 在Adder.scala中添加main函数

object Main {

def main(args: Array[String]): Unit = {

println("Generating the Adder hardware")

chisel3.Driver.execute(Array("--target-dir", "generated"), () => new Adder(8))

// chisel3.Driver.execute(Array("--help"), null)

}

}

? ?

?

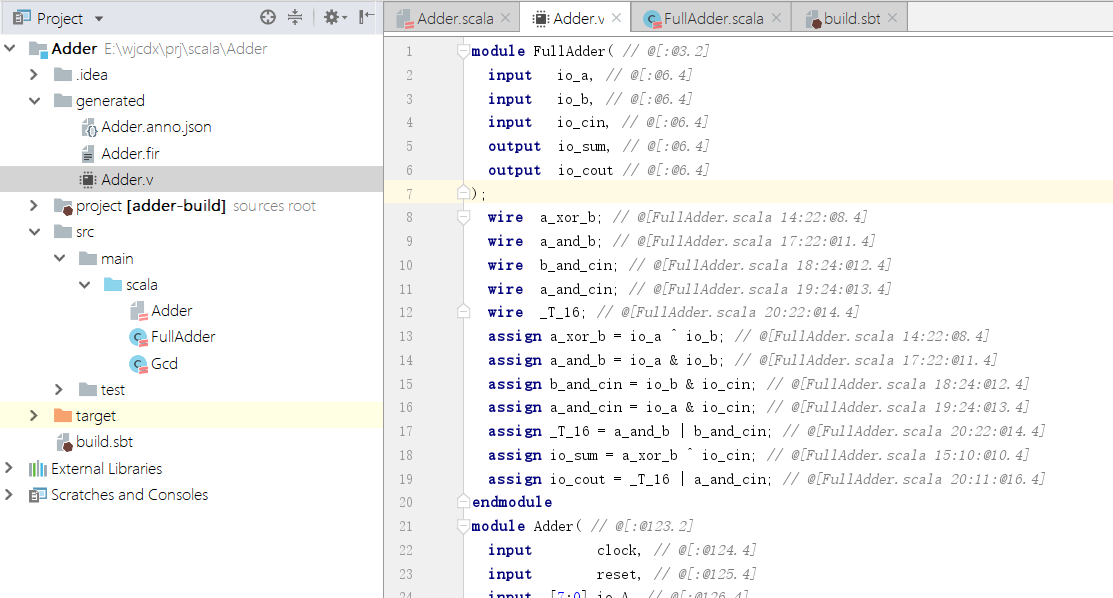

点击执行按钮,即可生成Verilog代码,存放在generated目录下。打开注释的--help,可以查看有哪些参数可以使用。

? ?

?

Linux命令行下类似,需要手动创建build.sbt文件,然后执行sbt命令构建。

PS. Scala语言过于复杂,编译比较慢。所需要的库基本都在国外,中国人需要耐心等待。

以上是关于Chisel3-创建工程并转换为Verilog代码的主要内容,如果未能解决你的问题,请参考以下文章