Spartan6芯片配置模式详解(转)

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Spartan6芯片配置模式详解(转)相关的知识,希望对你有一定的参考价值。

1. 配置概述

Spartan6系列FPGA通过把应用程序数据导入芯片内部存储器完成芯片的配置。Spart-6 FPGA可以自己从外部非易失性存储器导入编程数据,或者通过外界的微处理器、DSP等对其进行编程。对以上任何一种情况,都有串行配置和并行配置之分,串行配置可以减少芯片对引脚的要求,并行配置对8bit/16bit Flash或者微处理器来说更合适。

因为Xilinx的FPGA器件的配置数据存储在CMOS 配置锁存器内(CCL),因此Spartan6 FPGA器件上电后必须重新配置。Spartan6器件有多种配置模式,包括:

JTAG配置模式

. Master Serial/SPI配置模式(X1,X2,X4)

. Slave Serial配置模式

. Master SelectMAP/BPI配置模式(X8,X16)

. Slave SelectMAP配置模式(X8,X16)

Spartan6系列FPGA的配置模式由引脚M[0:1]的状态决定(详细介绍见Spartan6系列之器件引脚功能详述),在主配置模式中,CCLK默认来自与内部的振荡器,也可以来自外部的GCLK0/USERCCLK.,the BitGen -g ConfigRate选项可以设置内部时钟的振荡频率,默认频率为2MHZ;无论M[0:1]状态如何,JTAG配置始终可用。

对一个FPGA系统来说,可以有多种配置模式,但往往只有一种配置模式最适合自己的目标系统,应该要进行慎重的选择。当然,FPGA可以重新装载多个镜像文件,因此可以为1片FPGA提供多个配置文件,典型的应用为:当FPGA上电时,装载一个自检的镜像文件,完成自检后重新装载最终的应用程序镜像文件。这种方法可大大提高FPGA的使用效率。

因为FPGA的外部存储器可以存储多个镜像文件,因此可以通过FPGA正在使用(已装载的镜像)更新外部存储器内容,实现远程镜像更新升级。

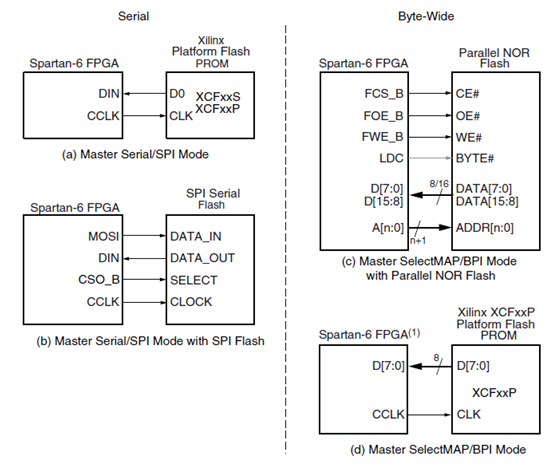

1.1. 主模式配置(master mode)

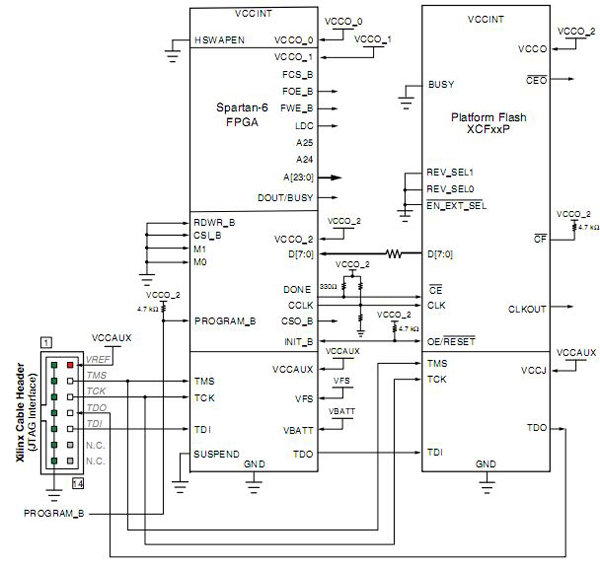

由FPGA自身将外部存储器的配置数据装载进内部的模式称为主模式配置;主配置模式的各种连接方式如下图1所示,左侧为串行配置连接方式,右侧为并行配置连接方式。

图 1 主配置模式连接方式汇总

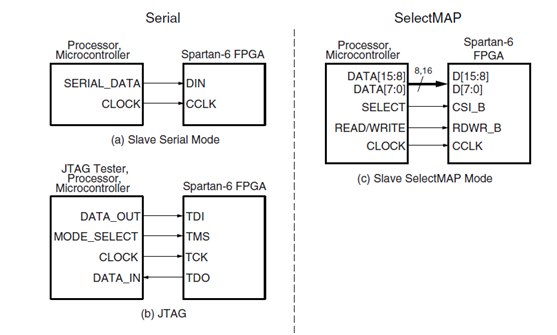

1.2. 从模式配置(slave mode)

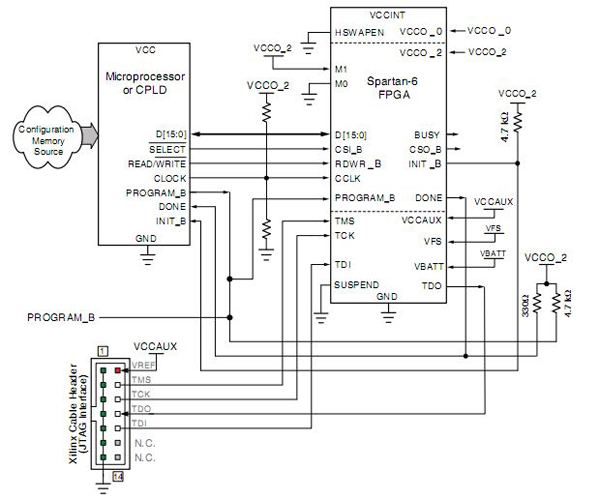

由外部器件(主要指处理器)对FPGA进行配置的模式成为从模式;从配置模式的各种连接方式如下图1所示,左侧为串行配置连接方式,右侧为并行配置连接方式。

图 2 从配置模式连接方式汇总

2. 具体配置模式详解

Spartan-6系列FPGA的配置模式由模式控制引脚决定,具体情况如表1所示。

表格 1 Spartan-6 FPGA配置模式

2.1. JTAG配置模式

在任何情况下,只要FPGA上电,就可以使用JTAG模式。

2.2. Serial配置模式

在serial配置模式中,FPGA在每个CCLK周期载入1bit配置数据。

图 3 Serial Configuration时序图

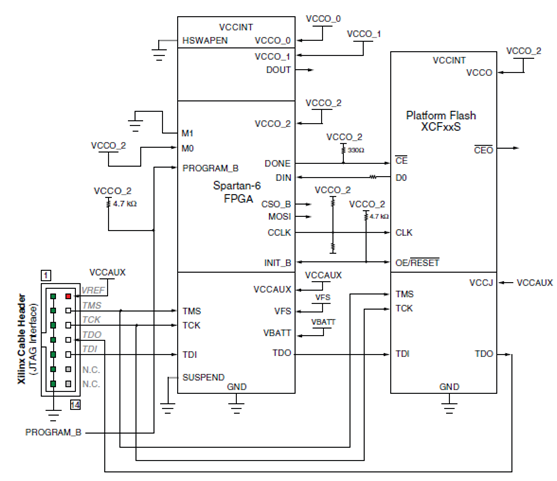

2.2.1. Master Serial配置模式

在配置完成之前,done信号为0,将在整个配置过程中片选platform Flash;program_B是在配置FPGA之前对FPGA进行异步复位;由时序图可以看出,若没有CRC错误,FPGA的INIT_B是作为输出始终将platform Flash的OE置高。

图 4 Master Serial Mode 配置电路图

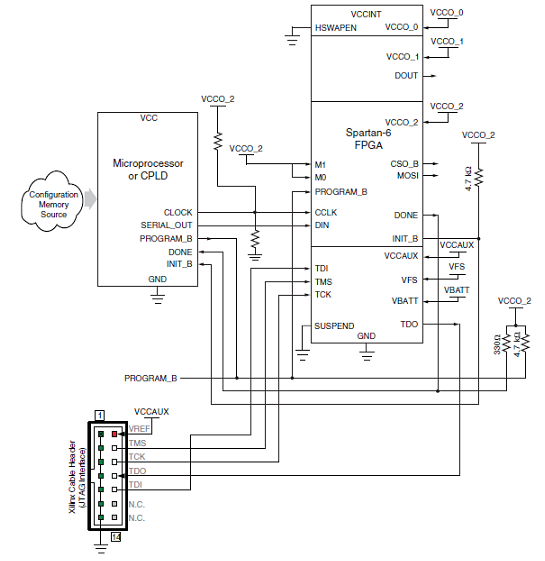

2.2.2. Slave Serial配置模式

对FPGA的异步复位(PROGRAM_B)既可以由外部器件如按钮产生,也可以由CPLD或microprocessor产生;数据及时钟信号均由CPLD等产生;

图 5 Slave Serial 配置模式

2.3. SelectMAP配置模式

SelectMAP配置接口提供了8/16bit双向数据接口,即可用于对FPGA的配置,也可用于对FPGA配置数据的回读。在SelectMAP模式中有多种配置思路,例举如下:

. 单FPGA的master SelectMAP配置

. 单FPGA的slave SelectMAP配置

. 多个FPGA呈菊花链连接形式以SelectMAP总线配置不同image

. 多个FPGA呈并列一组形式以SelectMAP总线配置同一个image

表格 2 SelectMap接口中需特别说明的接口信号

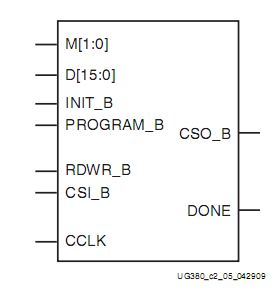

图 6 SelectMap配置接口

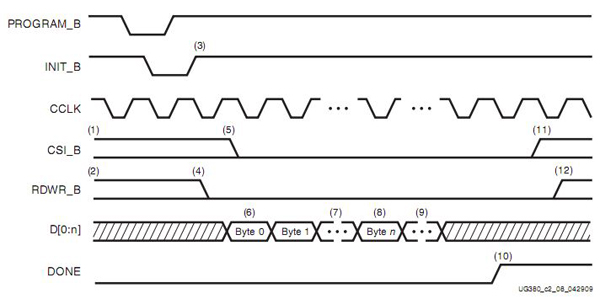

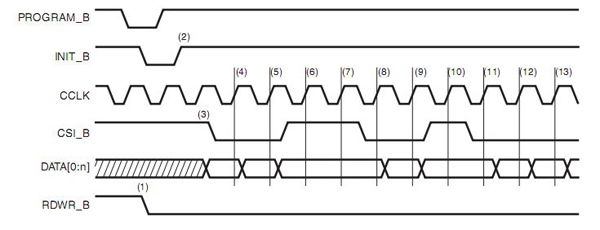

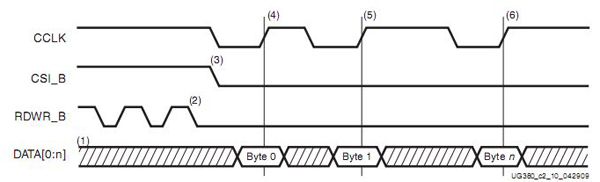

SelectMap配置模式有多种时序,因控制信号的不同而不同,主要有三种:连续的SelectMap配置模式数据载入时序、非连续数据总线可控的SelectMap配置模式数据载入时序、非连续时钟可控的SelectMap配置模式数据载入时序。数据总线宽带可以是8/16bit宽,数据宽度取决于配置启动阶段对数据总线采样的结果,在启动阶段,数据总线会输出特殊的标志数据。

图 7 连续的SelectMap配置模式数据载入时序

图 8 非连续数据总线可控的SelectMap配置模式数据载入时序

图 9 非连续时钟可控的SelectMap配置模式数据载入时序

2.3.1. 单FPGA的Master SelectMap配置模式

在主模式下,CSI_B和EDWR_B接地,使能了SelectMap的数据线并使数据线的方向为输入;因为是单FPGA,所以不需要用到CSO_B,浮置即可。

图 10 单FPGA的主SelectMap配置模式

2.3.2. 单FPGA的Slave SelectMap配置模式

当使用CPLD/Microprocessor来配置FPGA时,即可使用master SelectMap模式也可使用slave SelectMap模式,但优先使用Slave SelectMap配置模式。当CPLD/Microprocessor的SELECT等于0时,将使能FPGA的SelectMap配置模式数据总线;当CPLD/Microprocessor的READ/WRITE为0时,FPGA的SelectMap配置模式数据总线方向为输入,这时可以将配置数据输入到FPGA内部。

图 11 单FPGA的从SelectMap配置模式

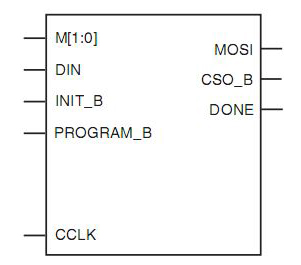

2.4. SPI配置模式

SPI配置模式只能工作于主模式,SPI接口允许FPGA把标准的工业SPI Flash作为配置数据存储介质。需要注意的是,在FPGA呈菊花链连接模式中,FPGA的SPI模式配置只能选择SPIX1方式,不能选择SPIX2或SPIX4模式。要使能FPGA的SPIX4的配置模式,需要在ise的BitGen选项里增加“-g: spi_buswidth:4”。

图 12 Spartan-6 FPGA SPI配置接口

图 13 Spartan-6 FPGA SPI配置接口电路图

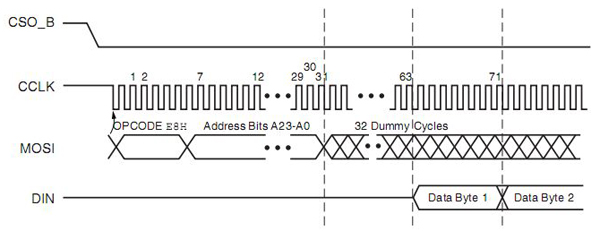

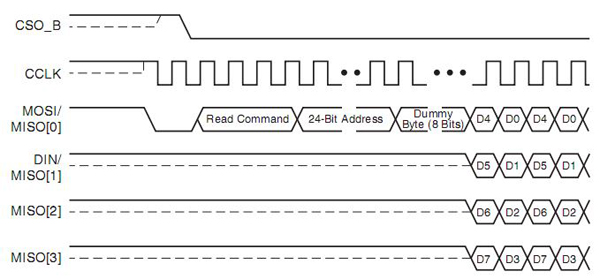

不同数据线传输模式根据SPI总线每次传输的命令区分,Single_Read的命令操作码:0x03或0xE8;Dual_Read的命令操作码:0x3B;Quad_Read的命令操作码:0x6B。

图 14 SPI总线Single_Read时序

图 15 SPI总线Dual_Read时序

图 16 SPI总线Quad_Read时序

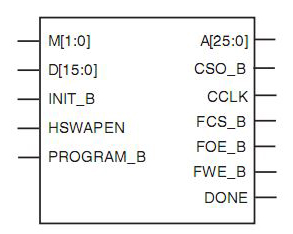

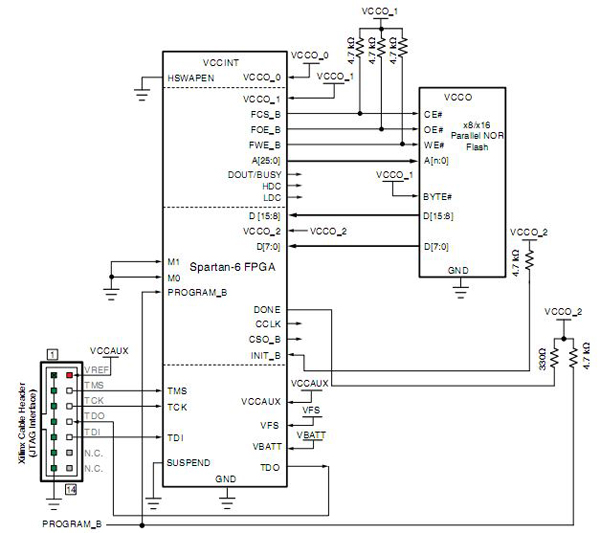

2.5. BPI配置接口

BPI:Byte-Wide Peripheral Interface,字节宽度外设接口。FPGA可以从一个工业标准的并行NOR Flash读取配置数据。Spartan-6 FPGA最高支持1Gb的NOR Flash,也就是说地址线最高可达26根,但是并不是每种Spartan-6 FPGA都支持BPI配置或者26位的地址线的,具体情况例举如下:

. MCB-M1(Bank1的存储器控制模块)可以用作BPI配置接口,但是,用户只能选择将MCB_M1用作存储器控制接口或者BPI之一,不能同时作为两种接口使用。

. 6SLX4 、6SLX25/T FPGA不支持BPI配置接口。

. TQG144 和 CPG196封装的FPGA不支持BPI配置接口。

. CSG225封装中BPI配置地址线A22、A23不可用。

图 17 BPI配置接口

表格 3 BPI配置中特殊引脚说明

图 18 BPI配置总线电路连接图

图 19 BPI配置总线时序图

以上是关于Spartan6芯片配置模式详解(转)的主要内容,如果未能解决你的问题,请参考以下文章