第三章 存储器的层次结构

Posted stormax

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了第三章 存储器的层次结构相关的知识,希望对你有一定的参考价值。

总览:

- 存储器的分类

- 存储器的层次化结构

- 半导体随机存取存储器

- SRAM存储器

- DRAM存储器

- 只读存储器

- Flash存储器

- 主存储器与CPU的连接

- 双口RAM和多模块存储器

- 高速缓冲存储器

- Cache的基本工作原理

- Cache和主存之间的映射方式

- Cache中主存块的替换算法

- Cache写操作策略

- 虚拟存储器

- 虚拟存储器的基本概念

- 页式虚拟存储器

- 段式虚拟存储器

- 段页式虚拟存储器

- TLB(快表)

- 外存储器

- 存储器的基本概念

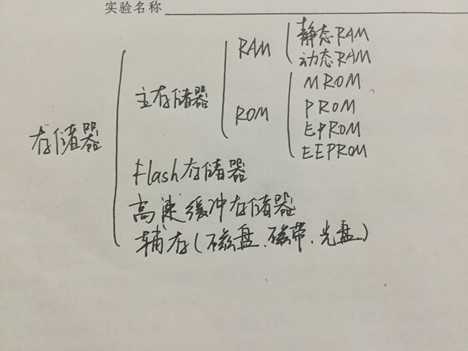

- 存储器的分类

- 按存储器介质分类:半导体、磁表面、磁心、光盘

- 按存取方式分类:RAM/ROM/顺序存取存储器/直接存取存储器

- 按在计算机中的作用分类:主存、辅存、缓冲存储器

- 存储器的性能指标

- 存储容量=存储字数*字长

- 单位成本:每位价格=总成本/总容量

- 存储速度:数据传输率=数据的宽度/存储周期

- 存储周期:从上一次访问存储器的操作开始(读/写),到下一次访问存储器的操作(读/写)为止,所花费的总时间。

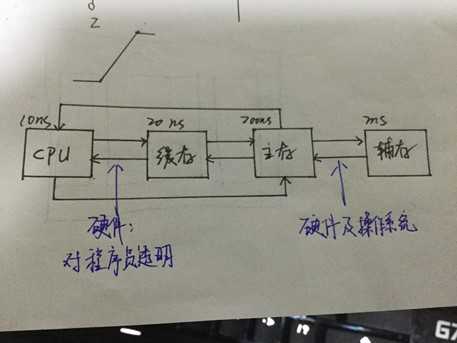

- 存储器的层次化结构

- 半导体随机存取存储器

- 基本概念

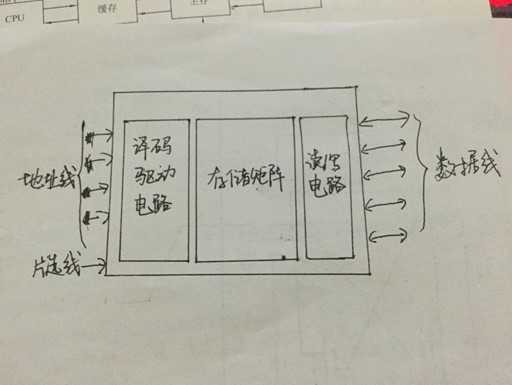

- 基本结构

- 译码驱动方式

- 线选法:假设矩阵有N行,则地址线有条,向上取整;读/写控制电路与矩阵每行的位数相同

- 重合法:有X地址译码器和Y地址译码器,通过坐标定位单元,有单独的读/写控制电路

- 读周期指芯片两次连续读操作的最小时间间隔;读时间表示进行一次存储器读操作的时间,显然读时间小于读周期;写周期与写时间类似。

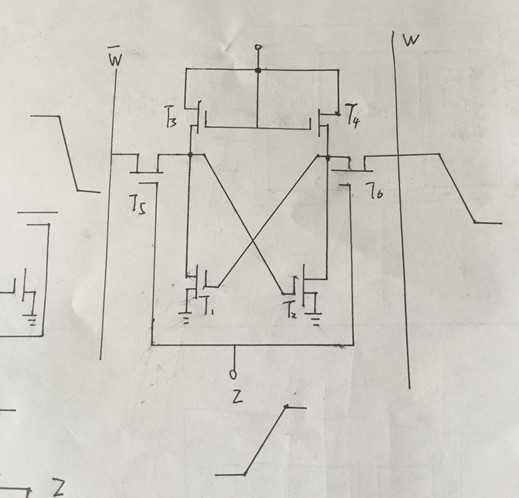

- SRAM存储器

- 规定:T1通、T2止,存"0";T1止、T2通,存"1"

- 电路图

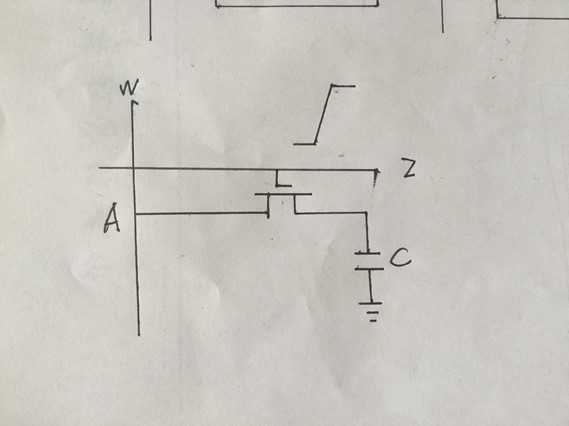

- DRAM存储器

- 工作原理:电容上有电荷存"1",电容上无电荷存"0",需要刷新

- 电路图

- DRAM存储器的刷新:读出后再原样写入,如果题目没有特别注明,刷新一行的时间就是一个存储周期;如果说明了刷新操作由读操作和写操作一起执行,那么刷新一行的时间就按照两倍的存储周期计算。

- 集中刷新:集中在一段时间内刷新(死时间)

- 分散刷新:分散的周期性的进行

- 异步刷新:有计划的刷新

- 刷新和再生的区别

对某个单元的刷新和再生操作过程是一样的,即读后恢复,但再生操作是随机的,只对所读单元进行,而刷新操作是按顺序定时一行一行进行的。

- 只读存储器

- Flash存储器

- 主存储器与CPU连接

- 位扩充:仅扩充数据线。

- 字扩充:仅扩充地址线,扩充的地址线作为片选信号。

- 字位扩充:先进行位扩充,对芯片进行分组,再进行自扩充。

- 双口RAM和多模块存储器

- 双口RAM

- 单体多字存储器:指令和数据在主存内必须连续存放才能发挥预期效果

- 多体并行存储器

高位交叉编址的多体存储器(顺序存储)

低位交叉编制的多体寄存器(交叉存储)

特点

每个模块内的体内地址是连续的,高位表示体号,低位表示体内地址

程序存放在相邻的体中,低位用来表示体号,高位用来定位体内地址

优点

非常有利于存储器的扩充,只需将存储单元的编号往后加即可

可以实现多模块流水线式并行存取,同时从主存中取出n条指令,大大提高存储器的带宽

缺点

由于各个模块一个接一个的串行工作,因此存储器的带宽收到限制

并行的体现

不同的请求源并行的访问不同的体

同一请求源并行的访问不同的体

- 高速缓冲存储器(Cache)

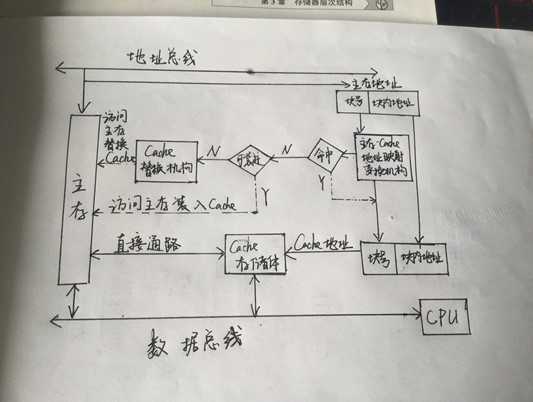

- 基本工作原理:局部性原理(时间、空间)

- 主存和Cache的编址:主存中的每块大小应与Cache中每块的大小相同

- 主存

主存的地址分为两部分:一部分用来寻找某个字块;另一部分用来寻找该字块中的字或字节。

- Cache

Cache的地址也分为两部分:高c位表示Cache的块号,低b位表示其块内的字或者字节数,Cache的块数远小于主存块数。

命中率的概念:CPU要访问的信息在Cache中的比例

平均访问时间的概念:假设命中率为h,tc为命中时访问Cache的时间,tm为未命中时的主存访问时间,则Cache主存系统的平均访问时间ta为:

Ta=h*tc+(1-h)*tm

Cache主存系统效率的概念:

用e表示效率,则e=tc/ta

Cache的命中率只和Cache的容量、Cache的字块长度有关

- Cache的基本结构

- Cache与主存之间的映射方式

直接映射

全相联映射

组相联映射

优点

1)实现简单。利用主存地址之间判断,即可确定所需字块是够在Cache中。

2)无需考虑替换策略

1) Cache的命中率可以提高

2)"有位置就可以做",Cache的利用率提高

对直接映射和全相联映射进行折中的一种方式,组相连映射中的一组看做直接相联中的一块。

缺点

- 不够灵活

- 冲突概率高

Tag的位数增加了,访问Cache时主存字块标记需要和Cache的全部"标记"进行比较,才能判断所访问的主存地址的内容是否已在Cache内。

应用场合

适合大容量Cache

适用于小容量的Cache

操作原理

首先,CPU指令指出一个内存地址,该地址包含tag、块号、字等字段。然后,根据内存地址的块号c找到Cache中对应的块号,找到Cache中对应的块号后将该块中的标记和内存地址中的t位tag标记送入比较器比较。若相符且有效位为"1",即表示命中,然后用内存地址的低b位在Cache中读取所需要的字即可。若不相符或有效位为"0",则需要从主存中读取所需要的块来替换Cache中旧的块,同时将信息送往CPU,修改Cache的标记,如果原来有效位为"0",还得将有效位置"1"

首先,CPU访存指令指出一个内存地址,该内存地址包含块号、字等字段。为了加快检索速度,Cache所有行的标记位和内存地址的块号一同送入比较器中比较,如果块号命中,则直接从Cache命中的块号中读取所需的字;如果块号不命中,则按内存地址读取这个字,同时吧内存块读入Cache行中。

首先,CPU访存指令指出一个内存地址,该地址包含tag、组号、字等字段。通过组号找到Cache中对应的组,然后将Cache该组中每一块的tag和内存地址的tag送入比较器进行比较。如果Cache中由某块的tag与之符合,则表示Cache命中,通过内存地址的低b位确定需要该块中的哪一个字,然后进行存取操作。如果Cache中每行tag都与之不相符,则不命中,需要去内存取需要的字,并将内存中该字所在的块送入Cache中

- Cache中主存块的替换算法

- FIFO

- LRU

- 随机法

- Cache写操作策略:CPU更改了Cache的内容,会导致Cache的内容和主存内容不一致。

- 写回法

- 全写法

- 写一次法

- 虚拟存储器

- 基本概念

页式虚拟存储器

段式虚拟存储器

段页式虚拟存储器

划分单位

页

段

把程序分段,再把每个段分固定大小的页

优点

由于页面的起点、终点地址是固定的,因此页表简单,调入方便,主存空间浪费小。

段的分界与程序的自然分界相对应;段的逻辑独立性使他易于编译、管理、修改和保护,也便于多道程序共享;某些类型的段(堆栈、队列)具有动态可变长度,允许自由调度以便有效利用主存空间。

兼备页式虚拟存储器和段式虚拟存储器的优点。

缺点

由于页面不是逻辑上的独立实体,因此处理、保护和共享都不如段式虚拟存储器方便。

段的长度各不相同,段的起点和终点不定,给主存空间分配带来麻烦,而且容易在段间留下去多空余的不易利用的零散存储空间,造成浪费。

在地址映射过程中需要多次查表。

- TLB(快表):快表是页表的子集,快表命中页表一定命中

- 外存储器

- 硬盘存储器

- 如何记录数据:归零制(RZ)、不归零制(NRZ)、"见1就翻"的不归零制"NRZ1"

- 技术指标:记录密度、存储容量、平均寻址时间、数据传输率、误码率

- 磁盘阵列

- RAID0

- RAID1

- 光盘存储器

- 只读型光盘CD-ROM

- 只写一次型光盘

- 可擦写光盘

感想:

上一章是看了难的不会做,这一章是看了和没看一样,根本不知道题目到底该咋做,TAT;昨天关word的时候居然忘了保存,今天写的80%都是昨天写的TAT;博客只总结了绝大部分的概念,对于计算题没有涉及。

以上是关于第三章 存储器的层次结构的主要内容,如果未能解决你的问题,请参考以下文章