Crosslink-NX器件应用案例: MIPI的多源合成(MUX)与分发(DeMUX)

Posted _Hello_Panda_

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了Crosslink-NX器件应用案例: MIPI的多源合成(MUX)与分发(DeMUX)相关的知识,希望对你有一定的参考价值。

作者:Hello,Panda

好久没有码文章了,今天讨论讨论MIPI多通道合成输出(MUX)和输入分发输出(DeMUX)的问题。这也是类似于Crosslink-NX此类器件的一个典型应用方向,通过增加传输速率的方式提升带宽,减少和主控的物理连线Lane数,这里熊猫君以Crosslink-NX基础视觉板和最常见的OV5640图像传感器为例,讲讲MIPI 4-MUX-1的实现思路,DeMUX将之反着实现就成。本质原理是利用MIPI的VC通道,因为VC通道占2bit,因此最多可支持4合1或者1分4使用。

1、技术参数

基于Crosslink-NX基础视觉板(芯片为LIFCL-40-7MG121I),采用OV5640图像传感器模组作为数据源,FPGA驱动并接收OV5640传感器数据并将其进行4-MUX-1合成后通过2.5Gbps硬核MIPI发出,需达到的主要技术参数如下:

(1) 合成模式:4-MUX-1,即支持4颗sensor数据源合成一路输出,亦支持3-MUX-1和2-MUX-1模式;

(2) 摄像头模组:OV5640,配置成为720P30,MIPI单lane YUV输出,亦可配置支持MIPI双Lane其它色空间格式输出;

(3)输出参数:MIPI 4-lane ,1.5Gbps/lane,4个VC通道,连续时钟模式;

(4) 本地显示:显示单摄像头图像,720P30,4个源交替显示。

从带宽考量,每路OV5640配置为720P30,YUV422格式输出的话,那么每颗Sensor所需带宽为336Mbps,四路就是1344Mbps。因此,输出的MUX MIPI链路使用1.5Gbps 4-lane的配置已经带宽足够富余了。

2、硬件电路

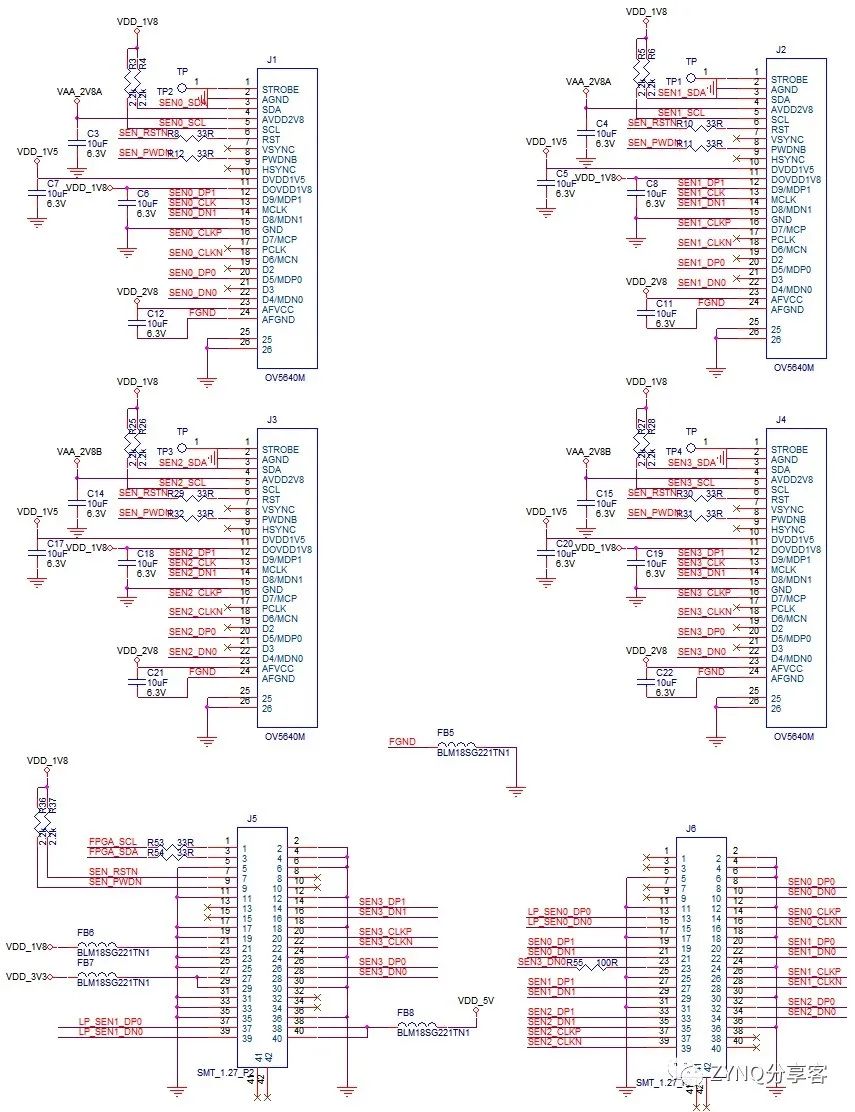

本章节简要描述硬件电路,电路原理图见下图1。

图1 硬件原理图

2.1 接口和信号描述

如图1所示,硬件电路通过与Crosslink-NX的J5、J6连接,合成好的MIPI数据通过30P FPC接口输出。

(1) FPGA通过IIC对CMOS进行配置,通过IIC通路切换芯片PI4MSD5V9545A实现1:4路的通路切换;

(2) 给CMOS的板载参考时钟是24MHz,对应MIPI输出的Lane速率为336Mbps;

(3) 连接到30Pin FPC接插件的J1~J3的sensor采用softMIPI采集,J4上的Sensor采用硬核MIPI接收;

(4)FPGA引出一路IIC信号,通过IIC 1:4 Switch进行切换到4路CMOS,芯片采用DIODES的PI4MSD5V9545A芯片,其访问IIC地址为0xE0,配置其内部的一个8bit寄存器实现通道的切换。

图2 实物照片

2.2 OV5640图像传感器

OV5640是OmniVision推出的一款彩色图像传感器,全画幅有效像素为2592*1944,内置ISP功能,图像输出接口支持DVP和MIPI(2-lane)两种,本例中选择配置为MIPI接口。OV5640支持RAW RGB、RGB565/555/444、CCIR565、YUV422/420和压缩图像等,支持的分辨率和帧率包括15fps@2592*1944、1080P30、960P45、720P60、480P90、240P120,本例选择720P30、YCbCr4:2:2输出。

Lattice Crosslink-NX LIFCL-40实现OV5640 MIPI输出,四合一MIPI MUX验证

3、软件设计

FPGA芯片采用Lattice Crosslink-NX LIFCL-40芯片,软件开发使用Radiant。

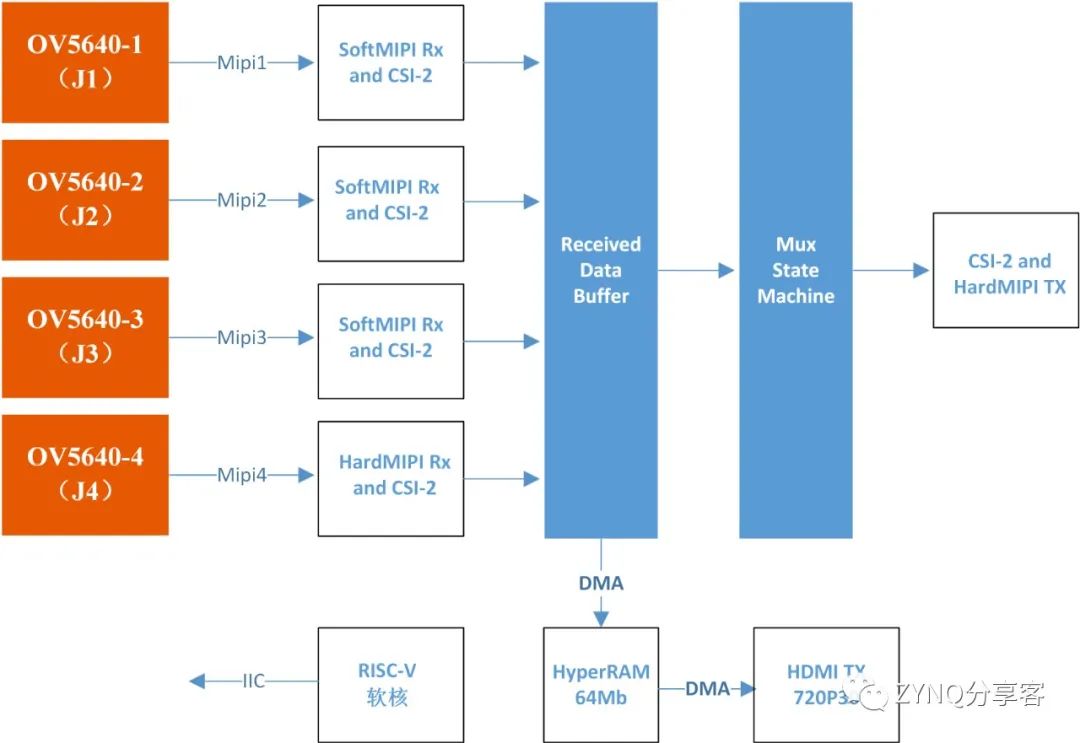

图3 软件框架

实现该需求的系统软件框图见上图1所示。通过一个RISC-V控制IIC外设配置四颗OV5640 Sensor使之输出720P30的YCbCr4:2:2图像,FPGA接收MIPI数据后经过缓存后通过一个MUX状态机将之合成到不同的VC通道上并通过HardMIPI接口发出。另外,可从四路sensor中选择一路图像经HyperRAM缓存并通过HDMI接口显示到电视上(备注:因输出为720P30图像,故可能大多数的显示器都不支持,但电视是可以直接显示的)。

3.1 IP配置

SoftMIPI和HardMIPI均使用Radiant里面的免费物理层IP MIPI DPHY来实现,CSI-2采用自己编写的源码,这样就避免了因部分用户未购买Radiant软件付费授权下无法使用的问题。下图4是HardMIPI的IP配置参数,图5是SoftMIPI的IP配置参数。

图4 HardMIPI IP配置

图5 SoftMIPI IP配置

因SoftMIPI是用普通的真差分IO来接收的,因此不具有专用MIPI Pad可以自主识别HS和LP状态的功能,所以需要引入MIPI LP信号(Lane-0的N端)来控制HS、LP的状态切换,判断依据是当LP信号翻转(说明有MIPI输入)时,当其为逻辑电平“0”时为HS状态,当其为逻辑电平‘1’时为LP状态。

3.2 CIS-2层

MIPI接收边的CSI层将数据恢复为Byte并通过一个Video Bridge将视频恢复为Vsync、Hsync、de和YCbCr4:2:2数据,收到的数据写入到Pingpong Buffer中,每写满一行向MUX状态发送一个输出请求信号,状态机对该信号接收并仲裁,并通过发送端的CSI-2层发出MUX后的数据到物理层。

同时,DMA会将给定通路Video Bridge恢复出来的视频数据通过DMA写入HyperRAM缓存供HDMI显示使用,HDMI的显示DMA读取数据并将YCbCr4:2:2的格式转换为RGB888格式送显。

好了,熊猫君今天的简单分享就到此为止了。这种MIPI的集合与分发在无人机、汽车成像、医疗成像、多屏显示等领域中得到了广泛应用,毕竟连接线只需要原来的1/4,也可以节省主控端口IO,好处不少。

最后,随便说一句,熊猫君的企鹅讨论组被毙了,如有需要,新组织可小窗熊猫君获取。

以上是关于Crosslink-NX器件应用案例: MIPI的多源合成(MUX)与分发(DeMUX)的主要内容,如果未能解决你的问题,请参考以下文章