ARM体系结构

Posted zch-blog

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了ARM体系结构相关的知识,希望对你有一定的参考价值。

ARM系列介绍

| 系列 | 频率 | 应用 |

| ARM7 | 100MHz | mp3/工控领域 |

| ARM9 | 200~400MHz | 第一代智能手机,加了内存管理单元(MMU) |

| ARM11 | 500~700MHz | 第二代智能手机、平板电脑 |

| cortexM | 100MHz | 单片机市场代替ARM7(功耗变低) |

| cortexA | 1GMHz | 消费类电子 |

| cortexR | 实时领域和安全领域 |

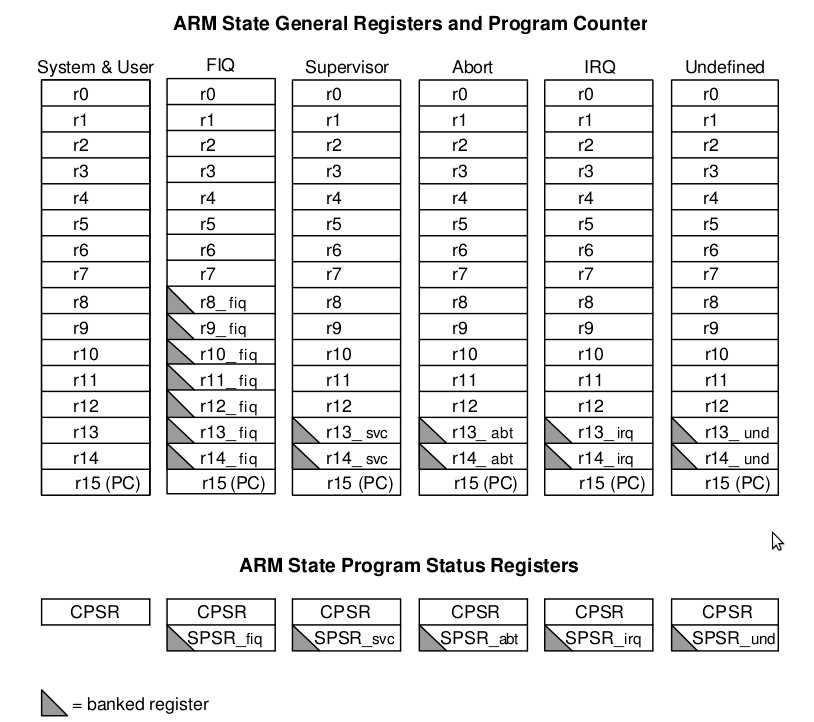

ARM寄存器

从上图我们可以看到ARM在逻辑上实现了七种工作模式,分别是:

系统模式(System)

用户模式(User)

快速中断模式(FIQ)

超级管理模式(Supervisor)

终止模式(Abort)

中断请求模式(也称普通中断,IRQ)

未定义指令模式(Underfined)

同一时刻下的CPU只能工作在一种模式下,CPU工作在某一模式下意味着只能看到该模式下的一组寄存器。且寄存器定长32位。

R0~R12寄存器是通用寄存器,保存数据临时变量

R13/SP是栈指针寄存器,记录栈顶地址

R14/LR是链接返回寄存器,保存程序的返回地址,如函数调用返回

R15/PC是程序计数器,PC只向哪个地址,CPU就到那个地址取指令执行

CPSR是当前程序状态寄存器,保存程序的运行状态

SPSR是备份当前程序状态寄存器

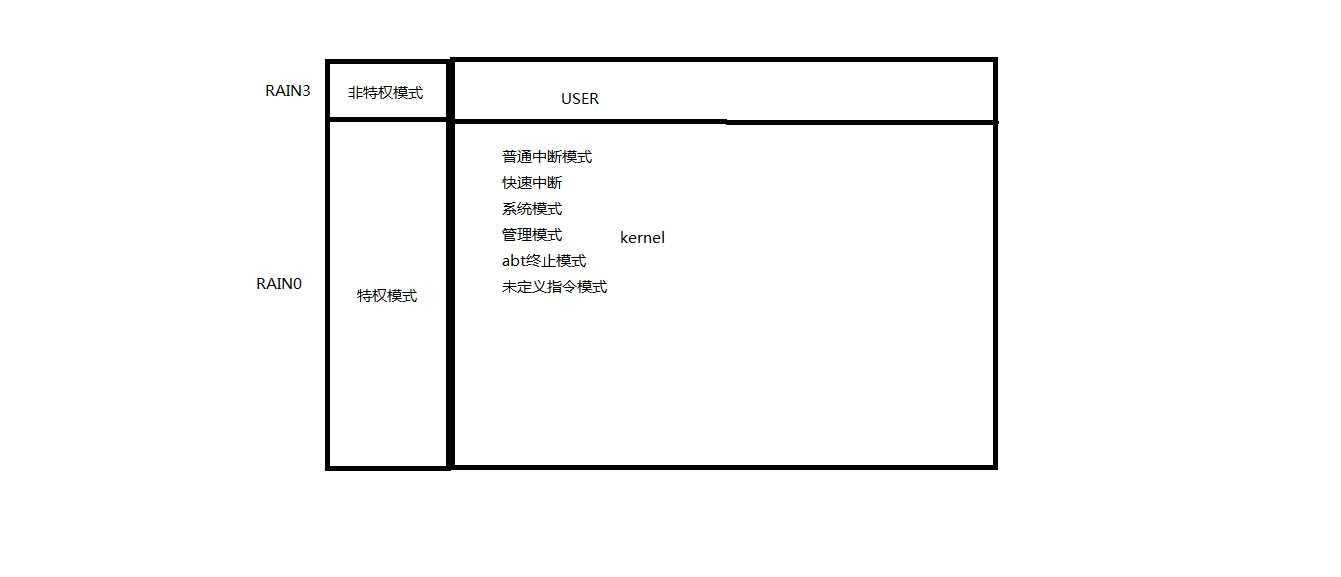

ARM的工作模式

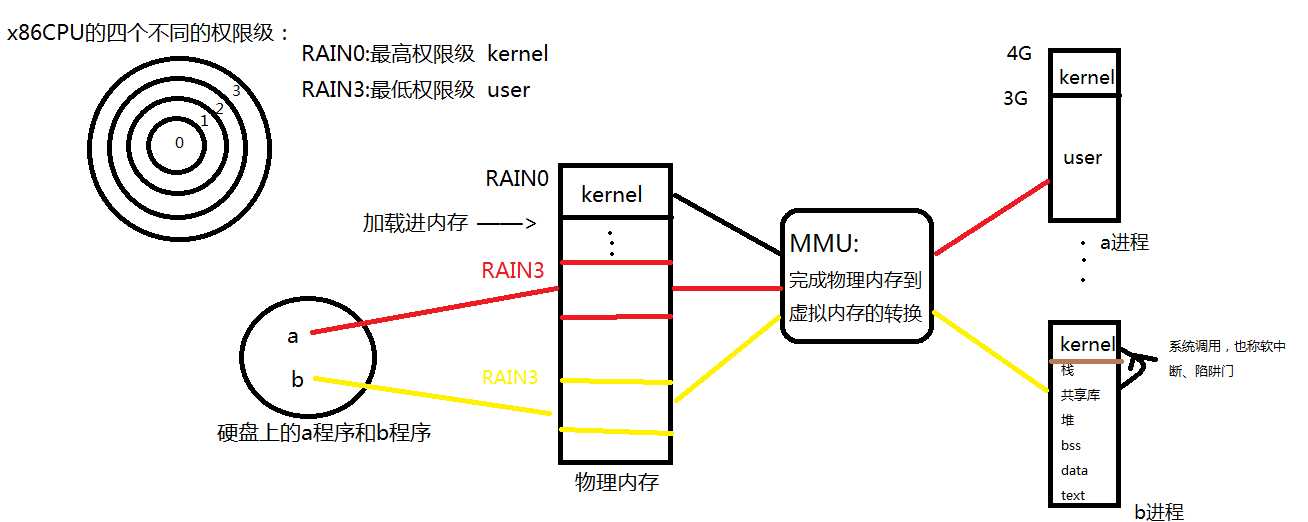

对比x86的工作模式

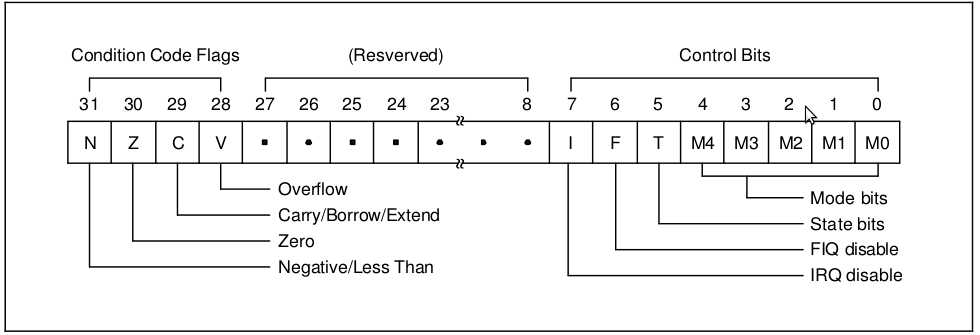

CPSR寄存器介绍

0~4位(M0~M4)是模式位,用于记录当前进程处于CPU哪种工作模式下。

5位(T)是记录指令模式,有ARM指令模式(32位汇编,执行效率高,存储大)和THUMB指令模式(16位汇编,把arm当单片机用时,采用该指令模式)

6、7位(F、I)分别是快速中断和普通中断的总开关

28位(V)是记录溢出位

29位(C)是记录进位

30位(Z)是零标志位,高级语言就是根据这位去判断两个数是否相等

31位(N)是符号位,是负数还是正数

以上是关于ARM体系结构的主要内容,如果未能解决你的问题,请参考以下文章