vivado + hdmi+ddr3--------基于VIVADO的DDR3三个时钟

Posted lgy-gdeu

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了vivado + hdmi+ddr3--------基于VIVADO的DDR3三个时钟相关的知识,希望对你有一定的参考价值。

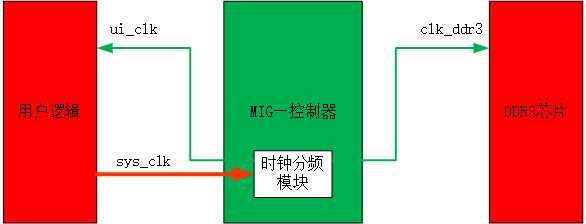

关于DDR3仿真平台的搭建,首先我们要了解DDR3IP盒子。DDR3的IP盒子是MIG。在我们使用MIG的时候,他所出的位置及其作用我们必须了解。也就是他所出在我们控制的什么位置。如下图所示:

MIG控制器也就是IP盒子,所处的位置是连接我们用户逻辑和DDR3芯片的中间控制器。其实大多数IP都是一端要链接我们用户逻辑一端连接我们要控制的器件。这里这样说是为了固话一下我们的思维,因为这里有三个时钟模块,经常会被弄混,也是在IP中起到了关键的作用。如果不能处理好这三个时钟模块,DDR3有很大的几率不能正常工作。如上图所示:因为DDR3芯片工作存储数据的时候必须用到时钟,所以MIG给了DDR3一个工作时钟;所有控制器的时钟都源于最顶层的时钟也就是sys_clk;当然MIG还会给用户糊一个时钟用于语用逻辑的控制。

一、三个始终的选择与介绍

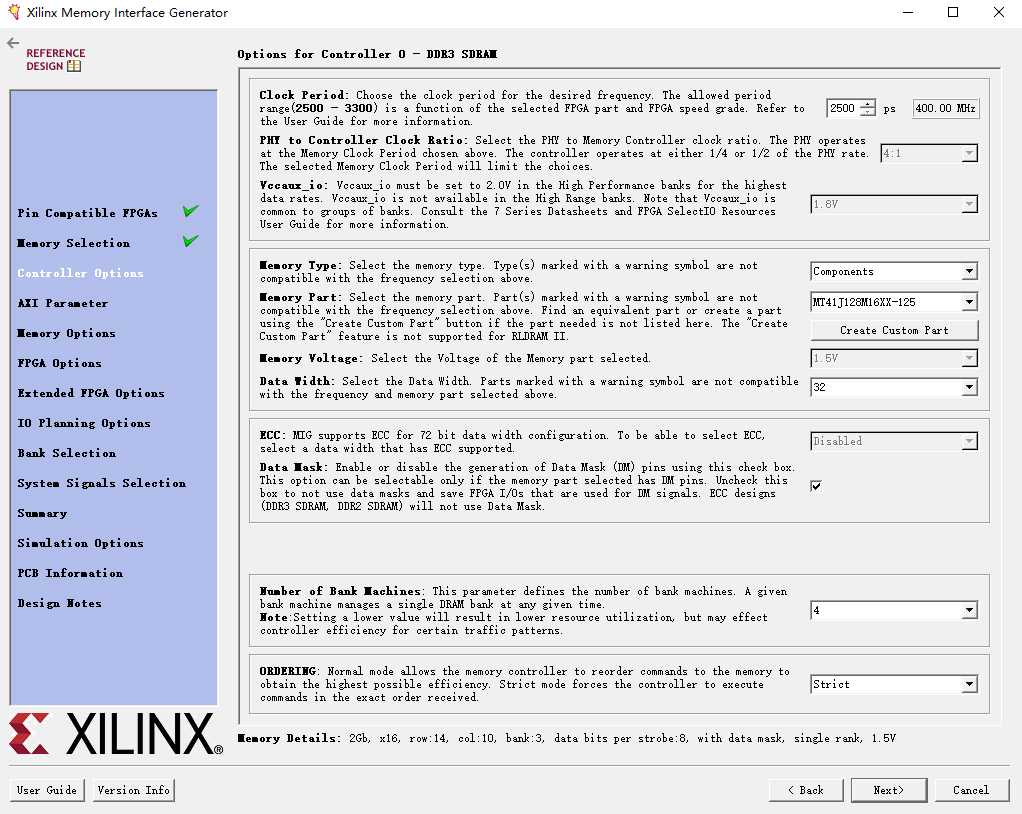

(1)第一个时钟,如下图所示,这里的locks_period ,这里的时钟功能是只是所有控制器的工作频率,该时钟收板子上的FPGA芯片和期间的速度等级的限制,速度等级就是选芯片的时候后面会有一个 -1,-2,就是代表速度等级。也就是对应着上图的ddr3_clk ,下图页面的第二个选项,是控制器的时钟频率和和用户的时钟频率,用户接口的数据总线的2:1比例宽度物理内存宽度的4倍,而4:1的比例总线是物理内存的8倍。RLDRA,2必须使用2:1,而RLDRAM3必须用4:1,同时2:1,具有较低的延迟,4:1速度快。就是说此处ddr3_clk 的工作时钟为400M,选择4:1的比例那么MIG会给出一个ui_clk给用户使用,也就是ui_clk=100M。

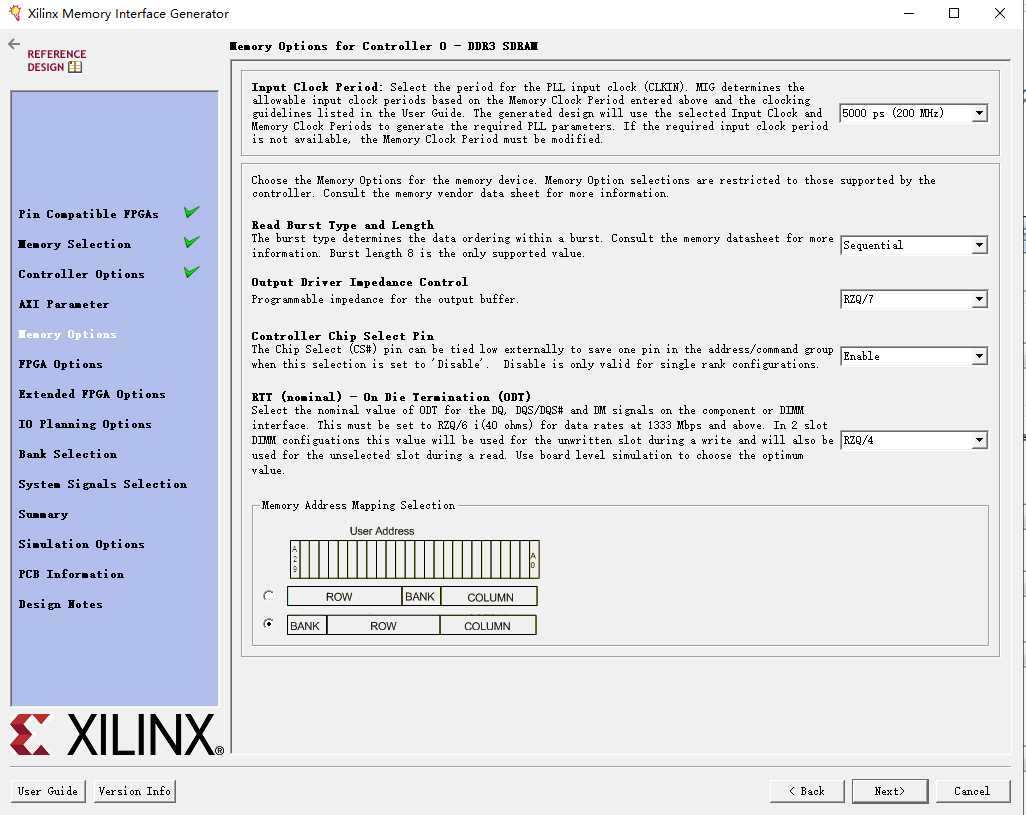

(2)、第二个时钟,如下图所示;这个时钟是给到MIG的时钟,也就是对应着的sys_clk。当然此处的sys_clk 不一定是你板子上的时钟,因为你板子的时钟总是某个特定值,这个值在这个芯片所承受的时钟范围内,但是在上图中的sys_clk 是可以是这个时钟的最大值;举个例子,假设某款FPGA的工作频范围是100M-533M,而我板子上的晶振为100M,但是此时此处的sys_clk就还可以选择300M、400M等。当然需要通过锁相环来实现。这里最好还是采用板子上的晶振时钟,一般的都为200M。

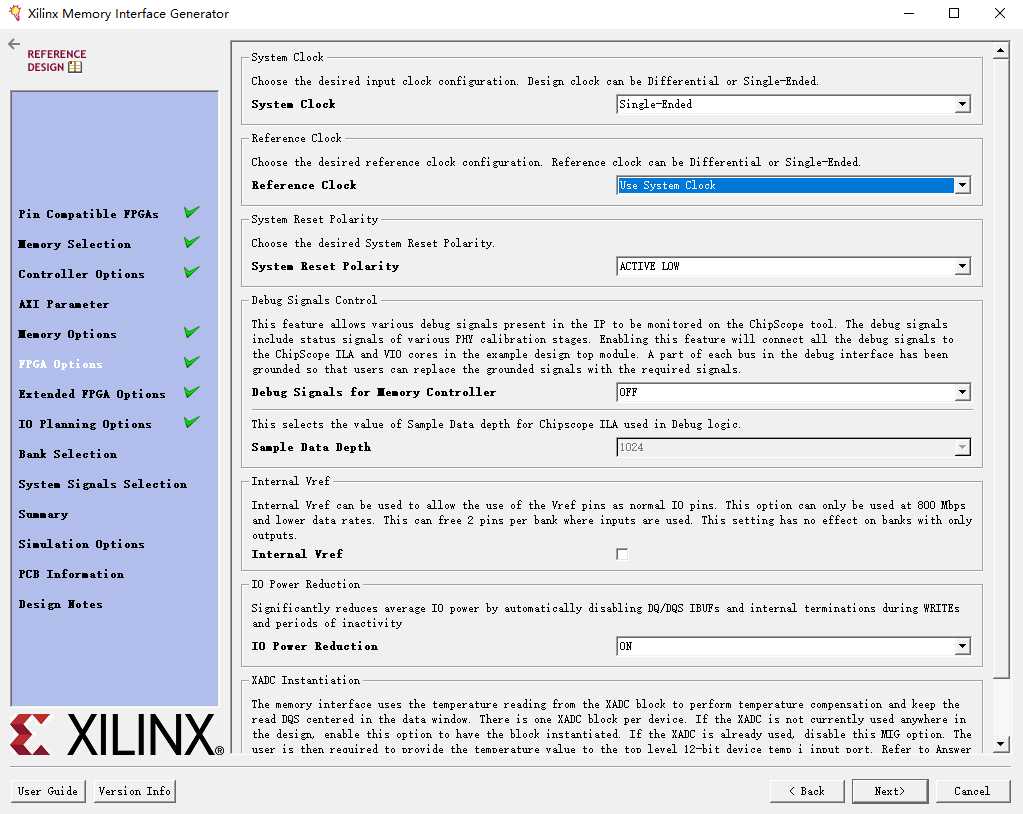

(3)、第三个时钟,如下图所示:此处选择的是输入到MIG的时钟类型(单端、差分或者否),只有用的官方的板子才选择NO-BUFF。第二个选项:参考时钟–该选项选择时钟类型(单端,差分,否对clk_ref信号对进行缓冲或使用系统时钟)。使用系统时钟选项当输入频率在199和201 MHz之间时(即输入时钟)出现周期介于5,025 ps(199 MHz)和4,975 ps(201 MHz)之间。参考时钟

以上是关于vivado + hdmi+ddr3--------基于VIVADO的DDR3三个时钟的主要内容,如果未能解决你的问题,请参考以下文章