AMD–7nm “Rome”芯片SOC体系结构,支持64核

Posted wujianming-110117

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了AMD–7nm “Rome”芯片SOC体系结构,支持64核相关的知识,希望对你有一定的参考价值。

AMD–7nm “Rome”芯片SOC体系结构,支持64核

AMD Fully Discloses Zeppelin SOC Architecture Details at ISSCC 2018 – 7nm EPYC “Rome” Chips Rumored To Feature Up To 64 Cores

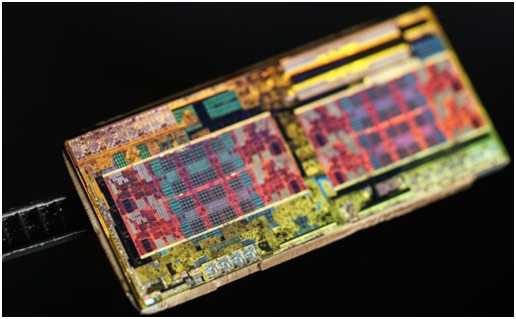

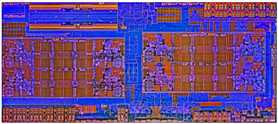

zeppelin模型的图像。

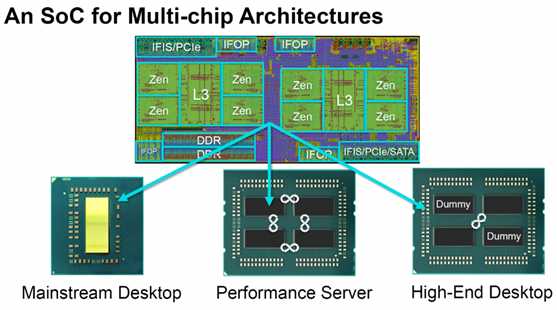

AMD已经正式发布了其用于多芯片架构的齐柏林SOC的最新细节。齐柏林SOC是芯片的代号,用于AMD14nm芯片的整个系列,包括Ryzen,Ryzen Threadripper和EPYC系列。AMD在其庞大的架构上提供了一个深层次的突破,在桌面、HETT和服务器领域的发布扰乱了市场。

AMD详细介绍了Zeppelin SOC用于多芯片架构-一个SOC用于主流桌面、高端桌面和性能服务器市场。

AMD齐柏林SOC的设计是为了迎合几个细分市场,同时具有性能和功率效率。这些目标都取得了惊人的成就,使公司(AMD)回到了CPU市场与英特尔的较量中。

英特尔的“真实世界性能”幻灯片再次显示了误导性的基准,市场定位显示英特尔酷睿i7与AMDryzen9台式机和笔记本电脑CPU不相上下。

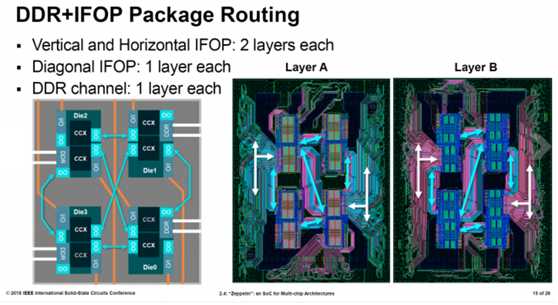

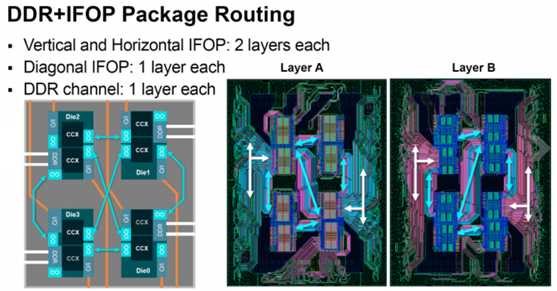

在每一个芯片内部都有一个由无限结构和相干连接链路组成的大型互连网络。每个Zeppelin模型提供32个高速I/O通道,对于Threadripper,共64个PCIe,对于EPYC,共128个PCIe通道。

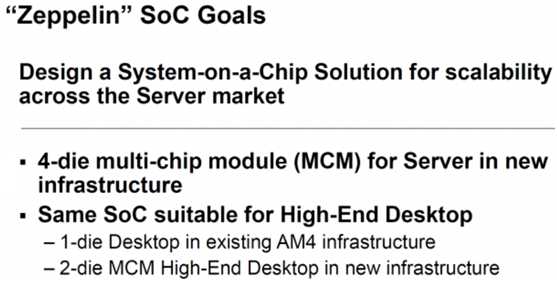

每个Zeppelin的模型都是由两个核心复合物组成的。核心综合体是Zeppelin模型的构建块,包括四个禅宗核心及其相关的L2/L3缓存。Zeppelin模型有三种产品,包括:

· 4-die multi-chip module (MCM) for Server

· 2-die multi-chip module (MCM) for High-End Desktop

· 1-die (CCX) for Desktop

每个Zeppelin模型由8个Zen x86核心组成,迄今发布的所有产品都基于第一代Zen核心架构,该架构使用14nm工艺节点。核心可以访问4MB的二级缓存,总共16MB的三级缓存。对于内存方面,每个Zeppelin模型可以提供2通道DDR4(带ECC)支持,允许每个通道2个DIMM,每个通道的最大容量为256 GB(EPYC)。

在每一个芯片内部都有一个由无限结构和相干连接链路组成的大型互连网络。每个Zeppelin模型提供32个高速I/O通道,对于Threadripper,共64个PCIe,对于EPYC,共128个PCIe通道。

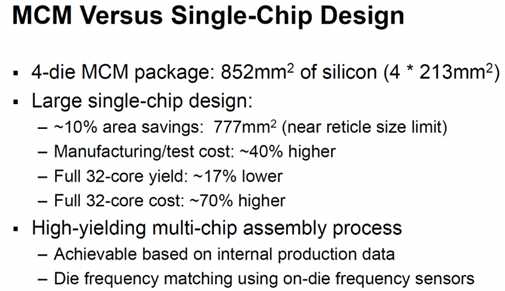

MCM方法与单芯片设计-成本节约,产量更高,生产问题更少。

AMD还想展示生产MCM芯片相对于单芯片的优势。当然,英特尔已经发布了一份声明,称AMD的做法只不过是一个4模粘在一起的架构,但EPYC已经证明了它的价值,无论是在性价比,还是增强的安全性和平台功能,Xeon的阵容,AMD的CPU必须提供。

AMD提到他们的4模MCM封装跨越了852平方毫米的硅面积,其中包括4个213平方毫米的Zeppelin模型。单芯片设计的面积约为777平方毫米,虽然它确实可以节省10%的面积,但这接近了制造节点的十字线尺寸限制,因此制造成本增加了40%。理论上32芯单模设计的成品率低17%,成本高70%。

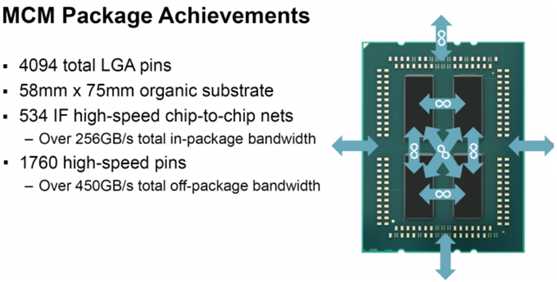

EPYC和Threadripper MCM解决方案配有4094个LGA管脚,整个硅由534个无限结构高速芯片到芯片网络组成,提供高达256 GB/s的总封装带宽。这是对1760个高速管脚的补充,这些管脚提供超过450gb/s的包外带宽。更大的基板尺寸也产生更好的功率传输和管理,有高达300安培的电流和高达200瓦的TDP支持。

AMD 7nm EPYC“罗马”-两个不同的芯片,多达64核。

有关于AMD7NM EPYC家族的报道。代号为“Rome”的新一代EPYC处理器有多达64个内核和128个线程。AMD的7NM EPYC芯片实际上基于两种不同的芯片。

· Die1: Single CCX 6 core, each Die 12 core, single CPU maximum 48 core

· Die2: Single CCX 8 core, each Die 16 core, single CPU maximum 64 core

第一个模具将包括每个核心复合物6个禅2核心,每个Zeppelin模型12核心。考虑到AMD长期使用同一个LGA 4094插座用于Threadripper和EPYC,可以从这个模型中看到最多48个核心和96个线程。传闻称,将有第二个7纳米EPYC芯片,将包括每个核心复合8核。这将允许16核关闭一个Zeppelin模型,给予7纳米EPYC多达64核和128线程。AMD可能真的会以如此出色的核心数量扰乱英特尔至强市场。

以上是关于AMD–7nm “Rome”芯片SOC体系结构,支持64核的主要内容,如果未能解决你的问题,请参考以下文章

国产GPU添新玩家,AMD出身,两款业界第一7nm芯片曾由他打造

Linux Kernel 4.21已更新:优化AMD 7nm Zen2架构

华为麒麟985已在台积电成功试产:7nm Plus工艺集成4G基带