计算机原理 6.13 单周期MIPS CPU

Posted fate-

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了计算机原理 6.13 单周期MIPS CPU相关的知识,希望对你有一定的参考价值。

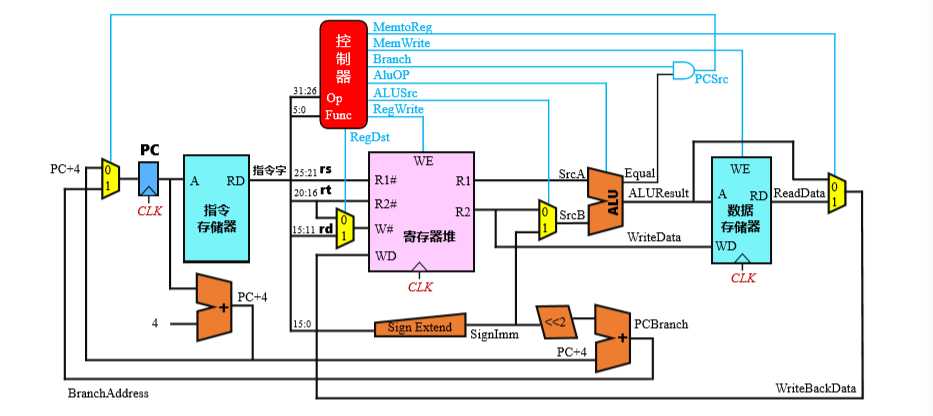

1、MIPS CPU控制器设计

定长指令周期:单周期实现

所有指令均在一个时钟周期内完成,CPI=1

性能取决于最慢的指令,时钟周期过长

变长指令周期:多周期实现

缩短时钟周期,复用器件或数据通路

可支持流水操作,提升性能

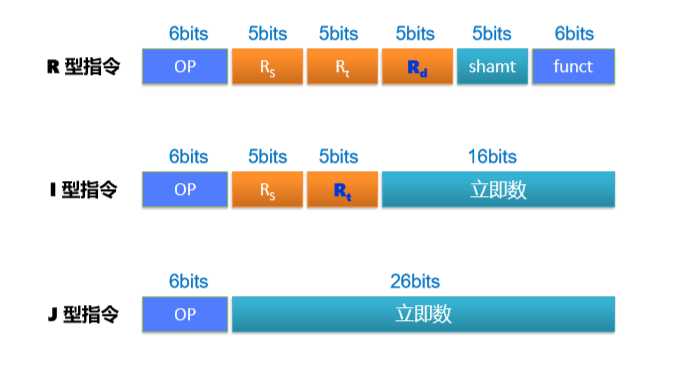

2、MIPS指令格式

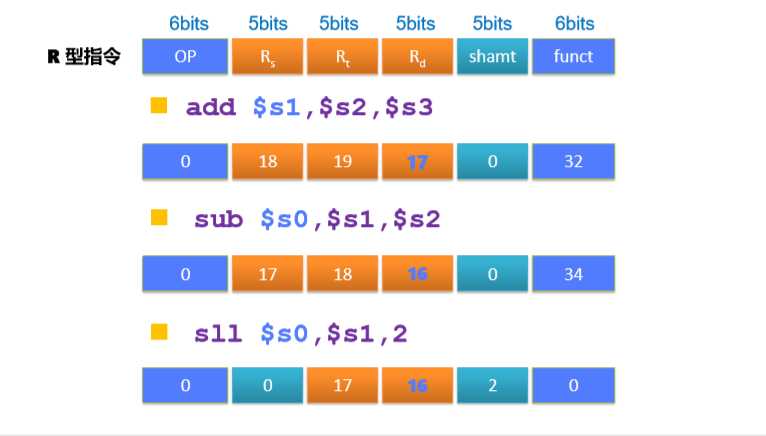

3、R型指令格式

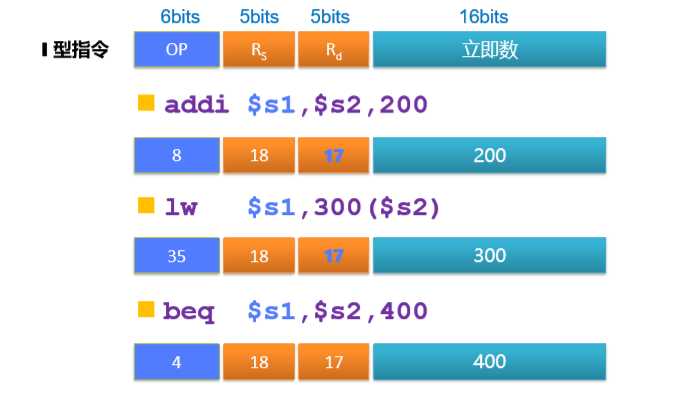

4、I型指令格式

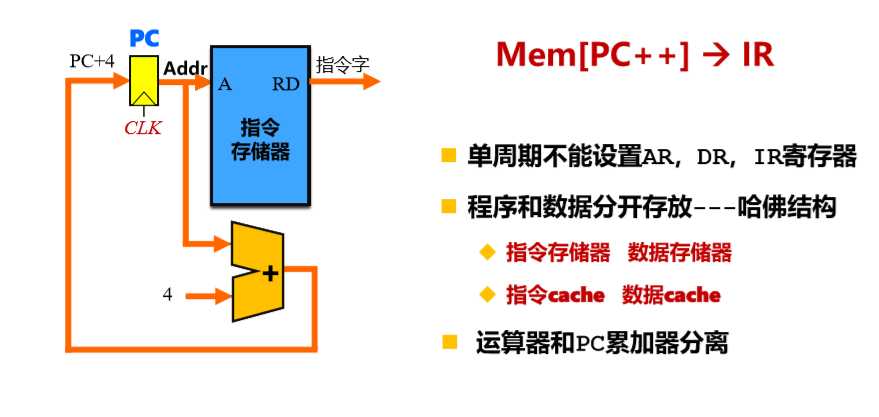

5、取指令数据通路

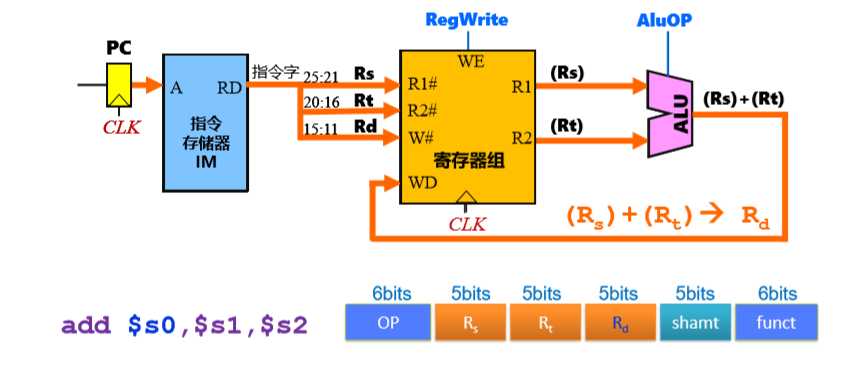

6、R型指令数据通路

7、lw指令数据通路

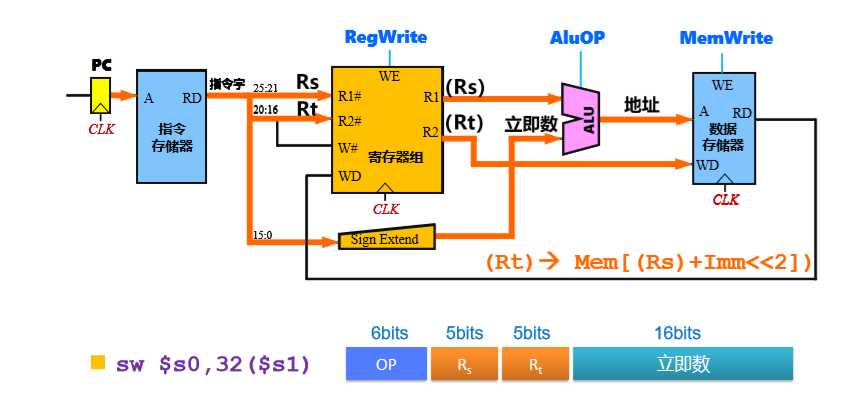

8、sw指令数据通路

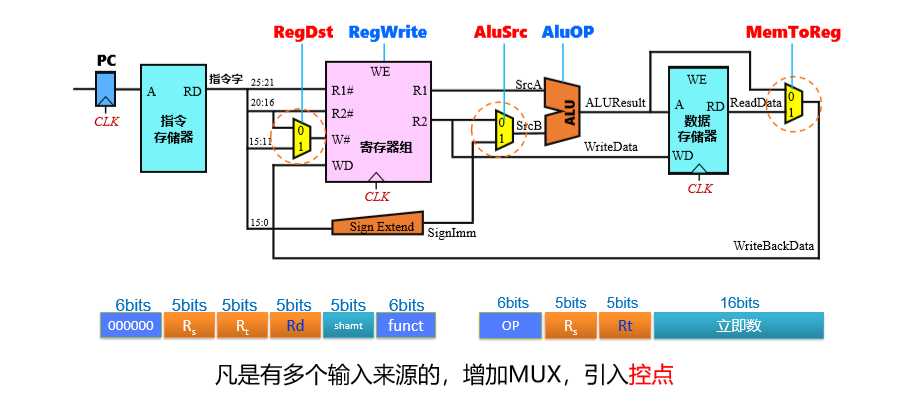

1、数据通路组合

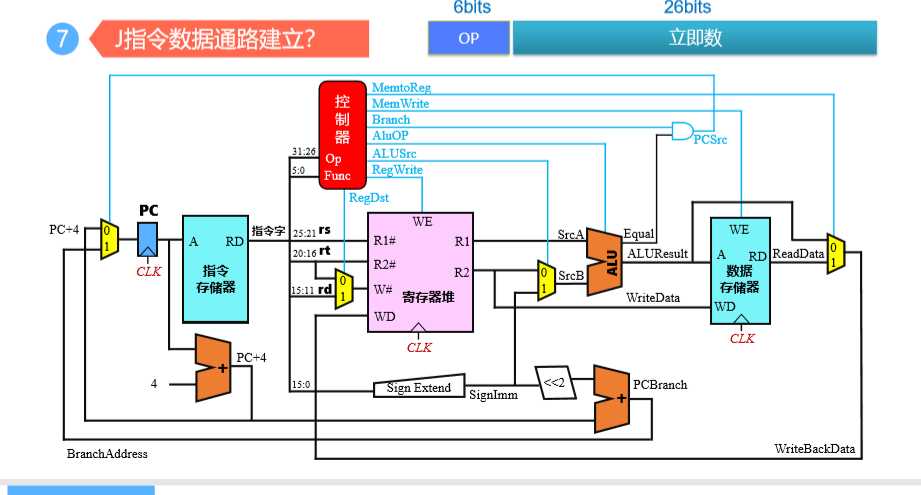

2、单周期MIPS数据通路

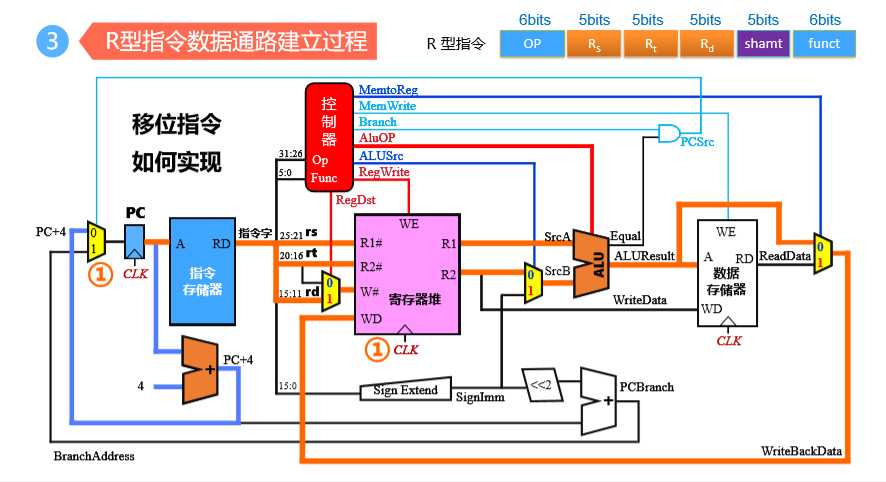

3、R型指令数据通路建立过程

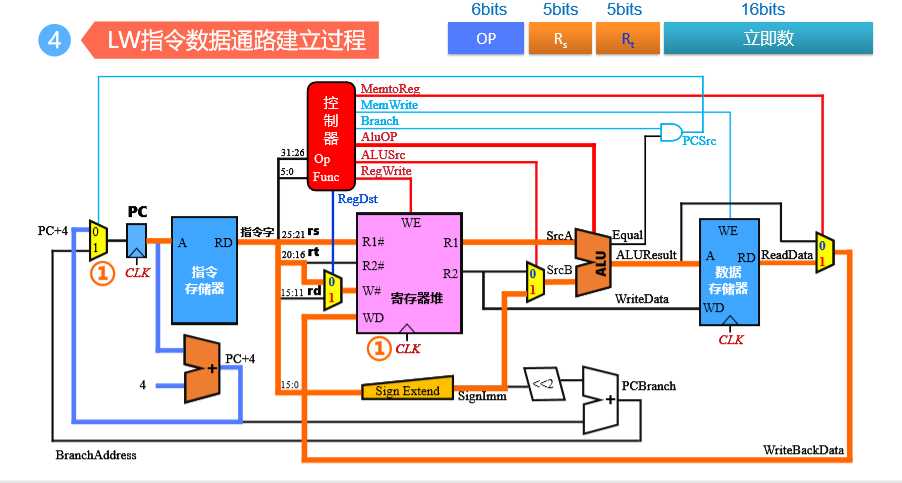

4、LW指令数据通路建立过程

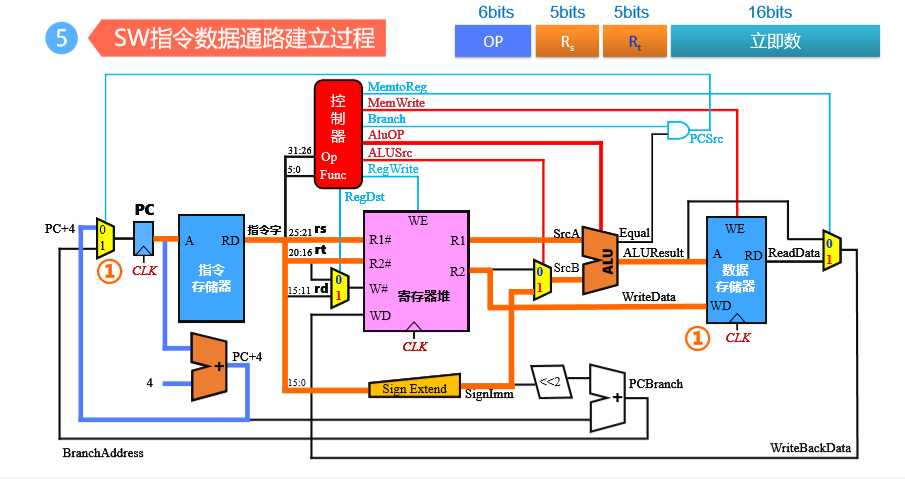

5、SW指令数据通路建立过程

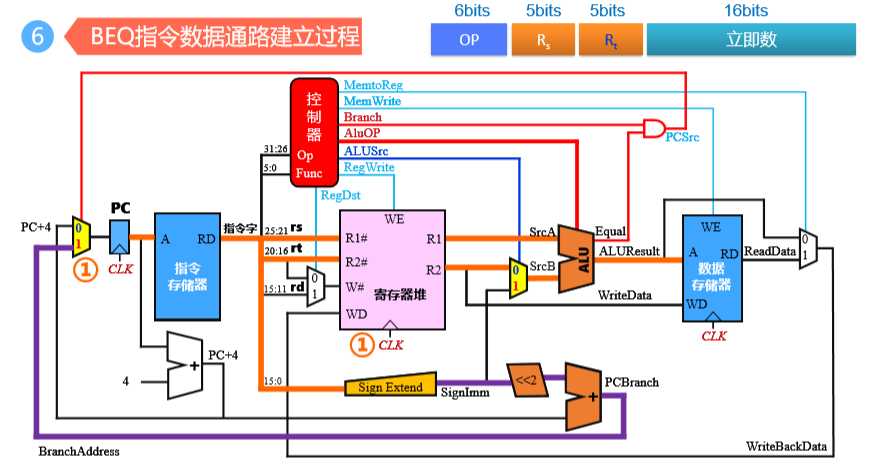

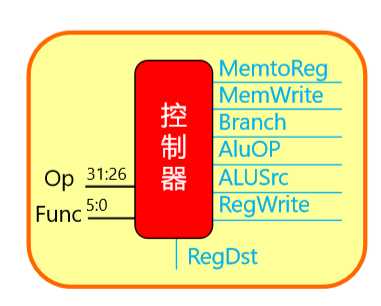

8、单周期MIPS控制器设计

单周期控制器无时序逻辑,纯组合逻辑电路

输入信号

指令字Opcode,Func字段(12位)

输出信号

多路选择器选择信号

内存访问控制信号

寄存器写使能信号

以上是关于计算机原理 6.13 单周期MIPS CPU的主要内容,如果未能解决你的问题,请参考以下文章