FPGAVHDL基础

Posted osea

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了FPGAVHDL基础相关的知识,希望对你有一定的参考价值。

对象

Constant(常量),Variable(变量),Signal(信号)

语法规则

1、保留字(int),对象(Architecture),函数,过程(process)组成的。

2、大小写不敏感

3、句末用“;”结束

4、对空格键不敏感

5、用--来注释

命名和标签

1、所有名字(字母数字下划线),以字母为首。

2、不能使用两个"_"

3、不能是关键字,名字必须独一无二地存在。

对象的声明

class object_name data_type [:int:value]

class:对象类型,(Constant,Signal,Variable)

object_name:对象名

data_type:数据类型(int,std_logic,std_logic_vector )

[:int : value ]: 初始值,可省略

例如

Constant a : integer := 100

Singal b : bit_vector(3 downto 0)

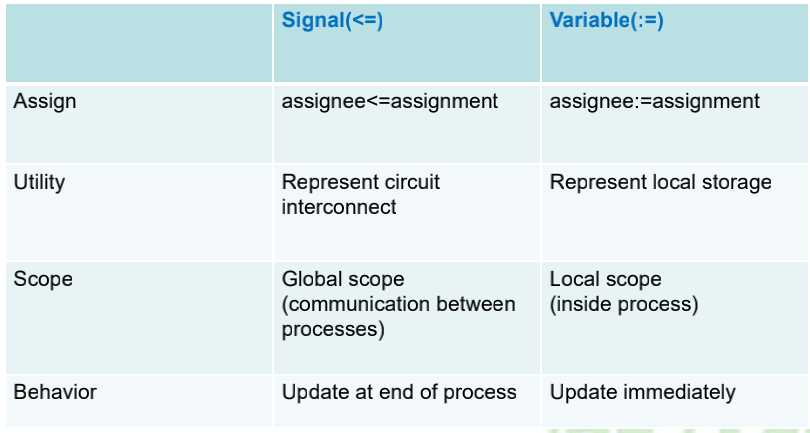

对象——变量和信号的赋值

Variable(Signal) tmp : std_logic_vector ( 7 downto 0 )

1、变量“:=” , 信号"<="

2、All bits :

tmp :=(<=) "10001000"

tmp :=(<=) X"88"

3、Signal bit:

tmp(7) :=(<=) ‘1‘

4、Bit-slicing:

tmp( 3 downto 0 ) = ‘1111‘

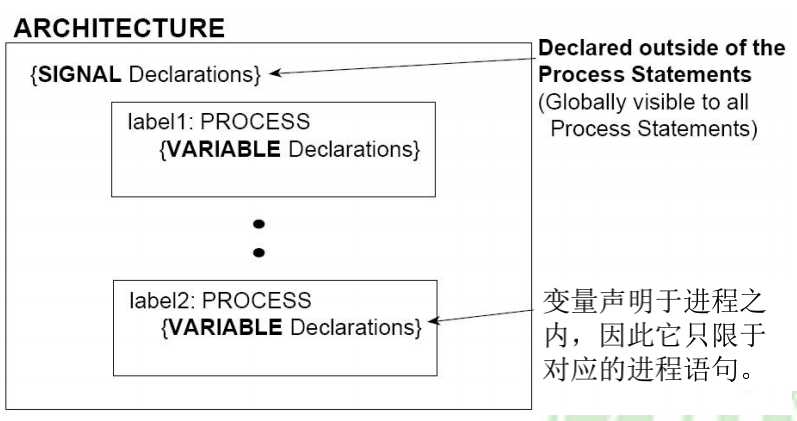

变量和信号的作用域范围

信号与变量的比较

数据结构

标准数据类型(std)和 标准逻辑数据类型(IEEE)

标准数据类型(std)

bit:2逻辑(‘0‘,‘1‘)

bit_vector:bits数组

signal A : bit_vector( 3 downto 0 )

signal B : bit_vector( 0 to 3 )

表示方向不同,位宽却一样

方向指的是"0001",可以是第0位,也可以是第3位,根据定义的方向不同。

( 3 downto 0 ) -> 第0位

( 0 to 3 ) -> 第3位

boolean:

false/true

integer

signal tmp : integer (32bits)

singal tmp : integer range 0 to 255 (8bits)

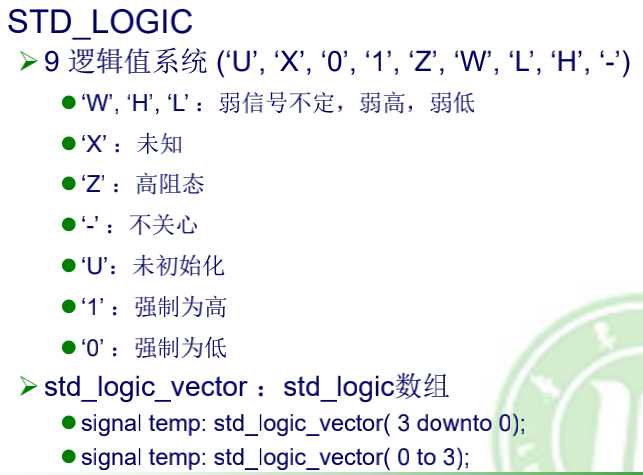

标准逻辑数据类型(IEEE)

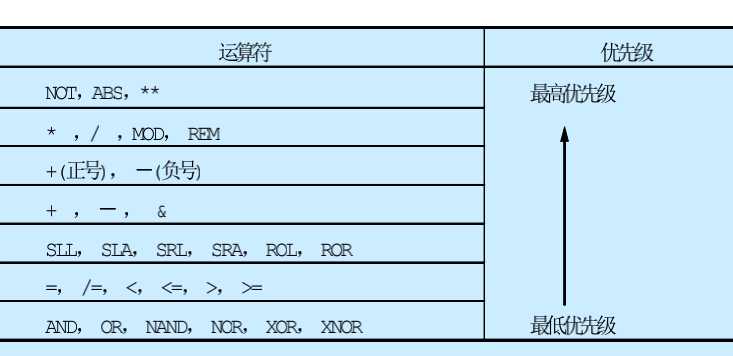

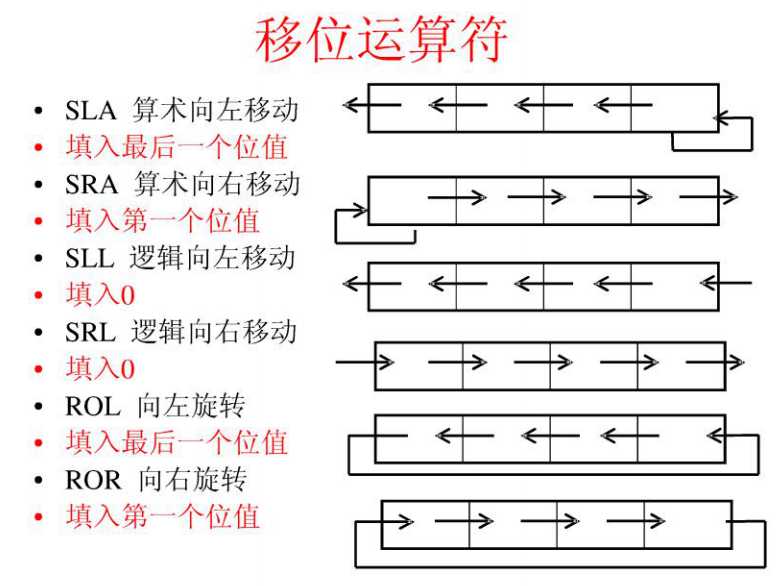

运算符

以上是关于FPGAVHDL基础的主要内容,如果未能解决你的问题,请参考以下文章