伪双口RAM的读写位宽不一致问题

Posted pangshian

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了伪双口RAM的读写位宽不一致问题相关的知识,希望对你有一定的参考价值。

伪双口RAM的写端口位宽和读端口的位宽可以不一致,但对应读写端口的深度也需要改变。

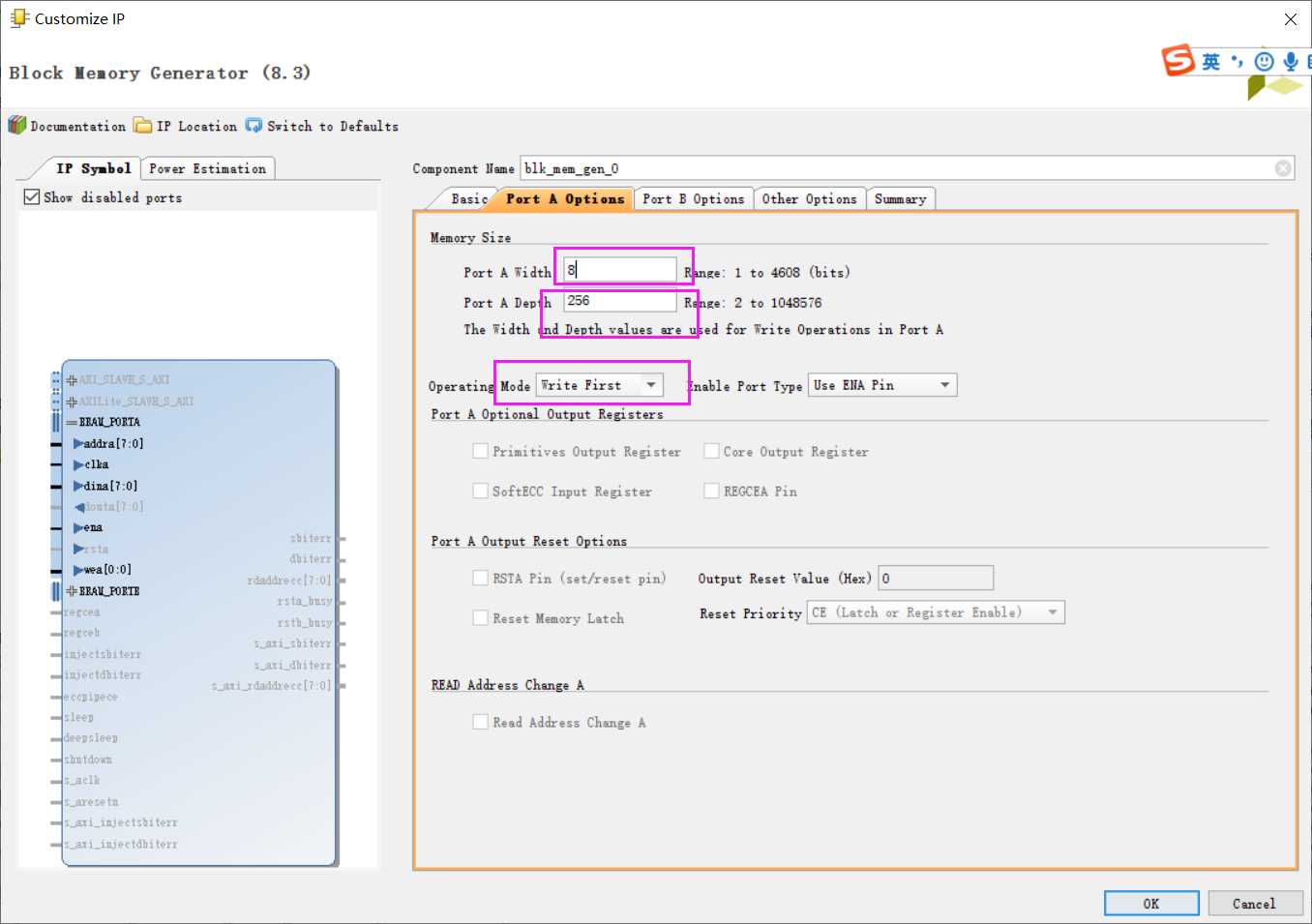

例如写端口Port A 数据位宽设置为 8bit,深度为 256 ;

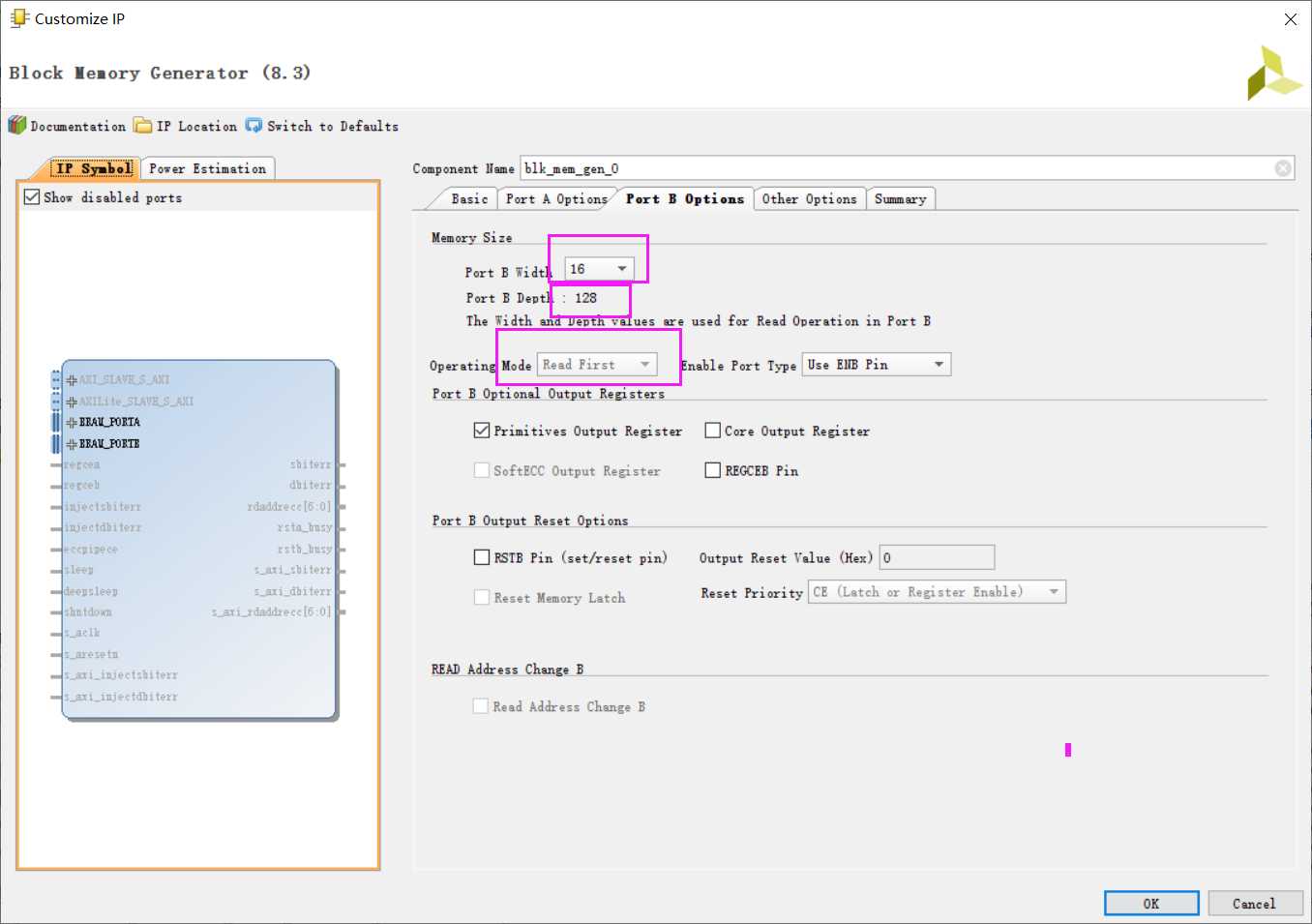

读端口Port B 数据位宽设置为16bit,那么对应的深度也需要减半,即128;因为读端口

每个时钟能够读出16bit的数据,所以深度也只需要一半。

这种方法在读写时钟保持一致的情况下,可以提升RAM中数据读取的速度,上述的例子

相当于读时钟是写时钟的两倍。

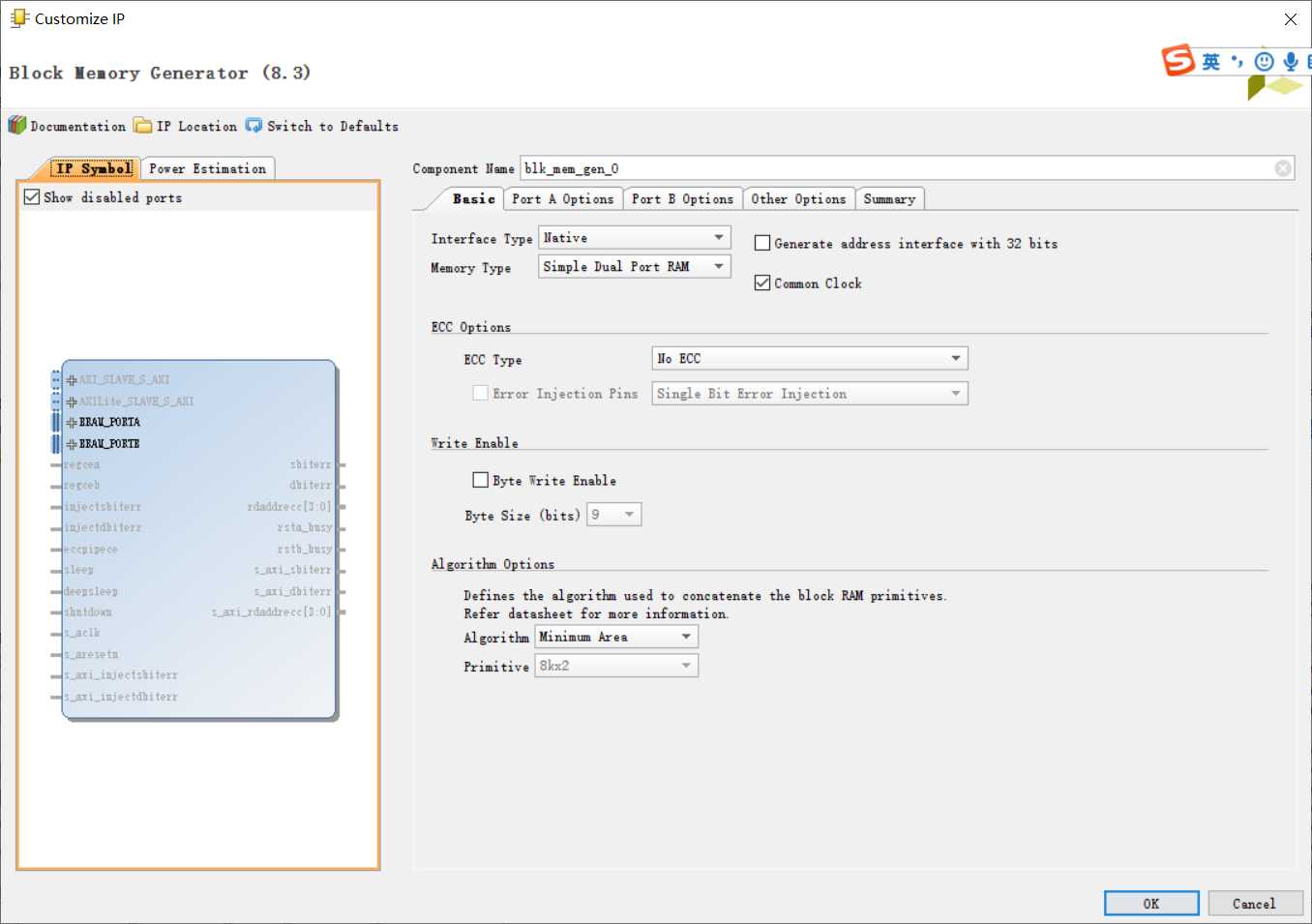

(1)basic

(2)Port A

(3)Port B

其他保持默认即可。

以上是关于伪双口RAM的读写位宽不一致问题的主要内容,如果未能解决你的问题,请参考以下文章