verilog 实现DDS

Posted yskn

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了verilog 实现DDS相关的知识,希望对你有一定的参考价值。

一.DDS的原理

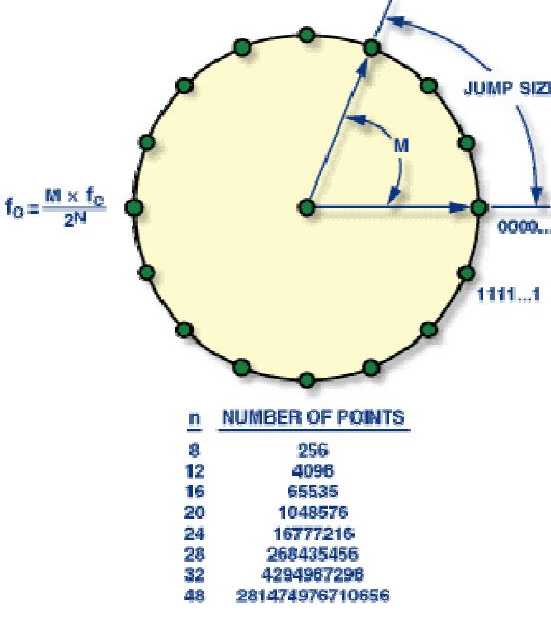

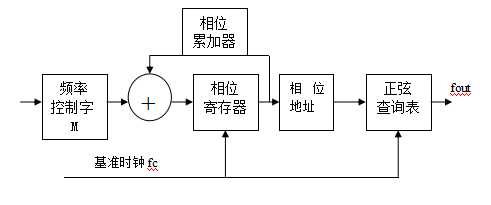

直接数字频率合成器(DDS),功能是通过输入频率输入字从而实现改变输出信号的频率的功能,它所利用的原理就是虽然对于一段正弦信号来说其幅度值是非线性的,但是其相位的值却是线性增加的,如下图所示:DDS的核心公式便脱颖而出

公式中N代表的是频率字输入的位数,当位数越大的时候输出的频率的频率分辨率便会越高,DDS的核心原理也如上图所示:

二.ROM的设计实现

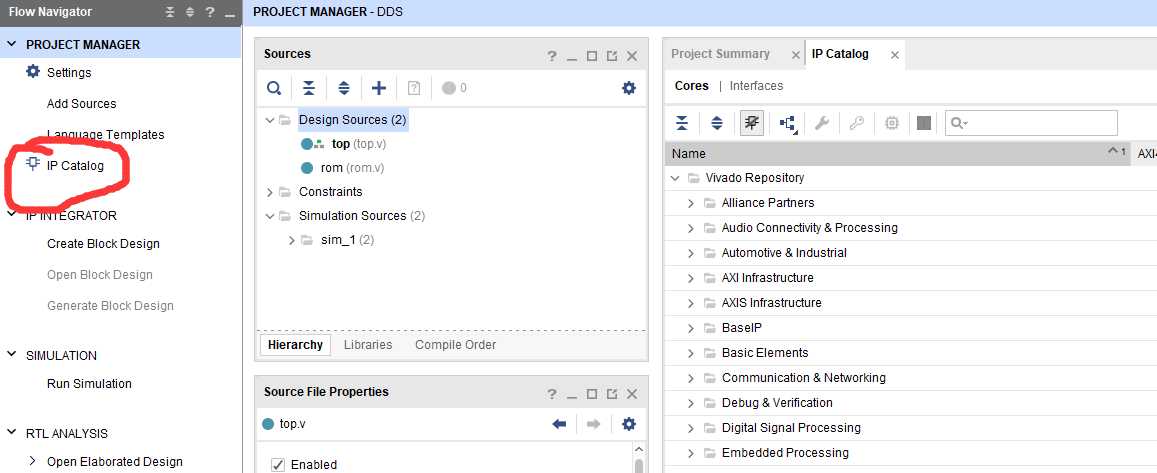

如果仅仅是为了设计方针可以通过$redmem来实现对某一文件的读取,但是为了实现可以综合的系统的设计我们采用如下的采用vivado自带的IP内核来设计,其实实现的过程是非常简单的,我们要完成的最主要的任务就是用vivado(我所使用的开发平台)完成ROM的IP核的配置工作,以及其他的工作即可,那么接下来我们来介绍一下ROM的配置:

首先第一步:(打来项目的IP catalog)

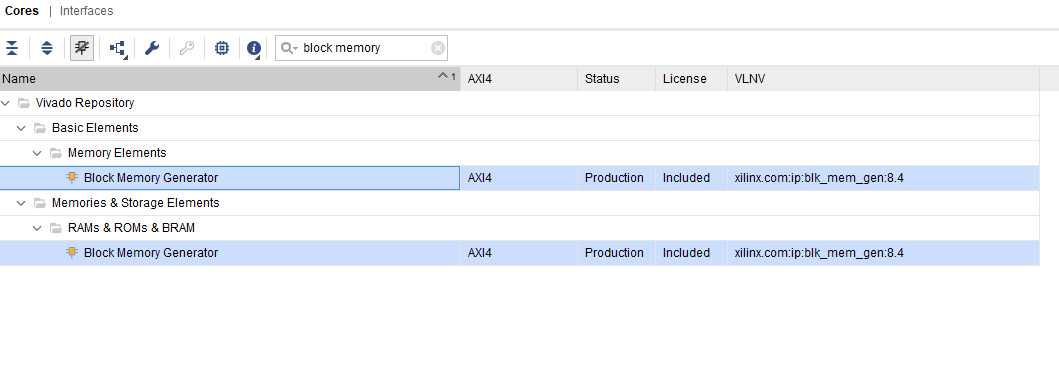

第二步,搜索block memory关键词

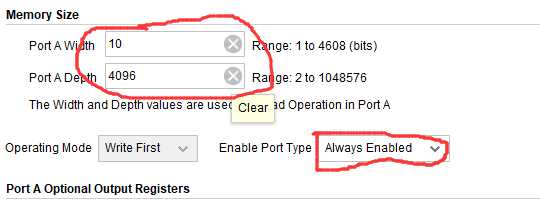

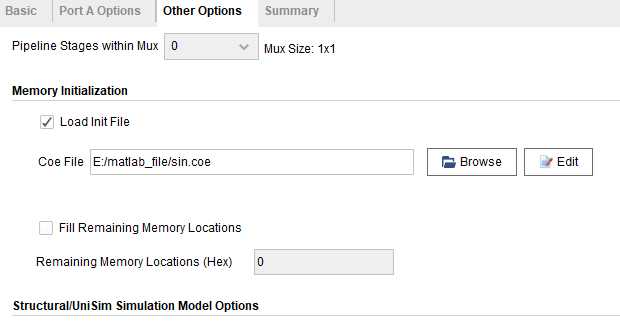

第三步,设置ROM的一些参数,包括其中的存储内容.coe文件以及其数据深度和数据宽度(数据深度指的是:最大可以存储的数据个数,比如12位的数据深度就是可以存储4096个数据。数据宽度指的是:存储数据的位数,即存储的几位数据)

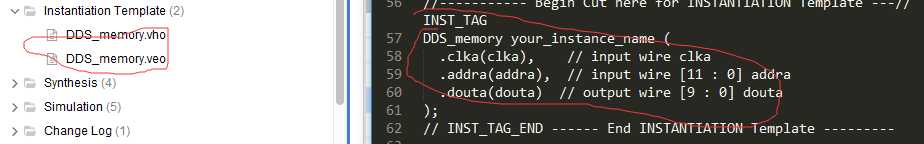

第四步,点击确认生成器件,在器件生成后依旧可以对器件进行修改,我们可以通过以下操作来引用ROM模块(右边是在sourses的IP sources的)。

三..coe文件的生成

t=0:2*pi/2^12:2*pi y=0.5*sin(t)+0.5; r=ceil(y*(2^8-1)); %将小数转换为整数,ceil是向上取整。 fid = fopen(‘sin.coe‘,‘w‘); %写到sin.coe文件,用来初始化sin_rom fprintf(fid,‘MEMORY_INITIALIZATION_RADIX=10; ‘); fprintf(fid,‘MEMORY_INITIALIZATION_VECTOR= ‘); for i = 1:1:2^12 fprintf(fid,‘%d‘,r(i)); if i==2^12 fprintf(fid,‘;‘); else fprintf(fid,‘,‘); end if i%15==0 fprintf(fid,‘ ‘); end end fclose(fid); t=1:1:2^12; y=(t<=2047); r=ceil(y*(2^8-1)); fid = fopen(‘square.coe‘,‘w‘); %写到square.coe,用来初始化rom_square fprintf(fid,‘MEMORY_INITIALIZATION_RADIX=10; ‘); fprintf(fid,‘MEMORY_INITIALIZATION_VECTOR= ‘); for i = 1:1:2^12 fprintf(fid,‘%d‘,r(i)); if i==2^12 fprintf(fid,‘;‘); else fprintf(fid,‘,‘); end if i%15==0 fprintf(fid,‘ ‘); end end fclose(fid); t=1:1:2^12; y=[0.5:0.5/1024:1-0.5/1024, 1-0.5/1024:-0.5/1024:0, 0.5/1024:0.5/1024:0.5]; r=ceil(y*(2^8-1)); fid = fopen(‘triangular.coe‘,‘w‘); %写到triangular.coe,初始化三角波rom fprintf(fid,‘MEMORY_INITIALIZATION_RADIX=10; ‘); fprintf(fid,‘MEMORY_INITIALIZATION_VECTOR= ‘); for i = 1:1:2^12 fprintf(fid,‘%d‘,r(i)); if i==2^12 fprintf(fid,‘;‘); else fprintf(fid,‘,‘); end if i%15==0 fprintf(fid,‘ ‘); end end fclose(fid);

以上是正弦波,方波以及三角波的形成matlab代码

以上是关于verilog 实现DDS的主要内容,如果未能解决你的问题,请参考以下文章