systemC构建时钟分频器

Posted

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了systemC构建时钟分频器相关的知识,希望对你有一定的参考价值。

时钟分频一般有两种,奇分频和偶分频,下面通过类中的普通函数方法分频:

分频器代码:

#include "base.h"

#ifndef CLKDIVIDER

#define CLKDIVIDER

const unsigned int N = 3;

SC_MODULE(clk_divider){

sc_in<bool> clk ;

sc_out<bool> divided ;

sc_signal<bool> e , o ;

sc_signal<sc_uint<32> > e_count;

sc_signal<sc_uint<32> > o_count;

void prc_clk_edivider();

void prc_clk_odivider();

void output();

bool param(unsigned int N);

SC_CTOR(clk_divider){

SC_METHOD(prc_clk_edivider);

sensitive<<clk.pos();

SC_METHOD(prc_clk_odivider);

sensitive<<clk.neg();

SC_METHOD(output);

sensitive<<e<<o;

};

};

#endif##############################################################################################################################

#include "clkdivider.h"

void clk_divider::prc_clk_edivider(){

sc_uint<32> temp = e_count.read();

if( temp == (N/2-1) )

{

// 对于一位的操作只能用!取反

e = !e ;

e_count = 0 ;

}

else

e_count.write(temp+1) ;

}

void clk_divider::prc_clk_odivider(){

sc_uint<32> temp = o_count.read();

if( temp == (N/2-1) )

{

// 对于一位的操作只能用!取反

o = !o ;

o_count = 0 ;

}

else

o_count.write(temp+1) ;

}

void clk_divider::output(){

if( param(N) )

divided = e|o ;

else

divided = e ;

}

bool clk_divider::param(unsigned N){

return N%2 ;

}##############################################################################################################################

#include "clkdivider.h"

int sc_main(int argc , char * argv[]){

// signal defination

sc_signal<bool> q ;

sc_clock clk("clock",1,SC_NS,0.5);

// istance the component

clk_divider div("fre_divider");

div(clk,q);

sc_trace_file * vcd = sc_create_vcd_trace_file("record");

sc_trace(vcd,clk,"clock");

sc_trace(vcd,q,"divided");

sc_start(1000,SC_NS);

sc_close_vcd_trace_file(vcd);

return 0 ;

}以上就是3分频的分频器的实现,只需改动常变量,那么就可以成为n分频的分频器。

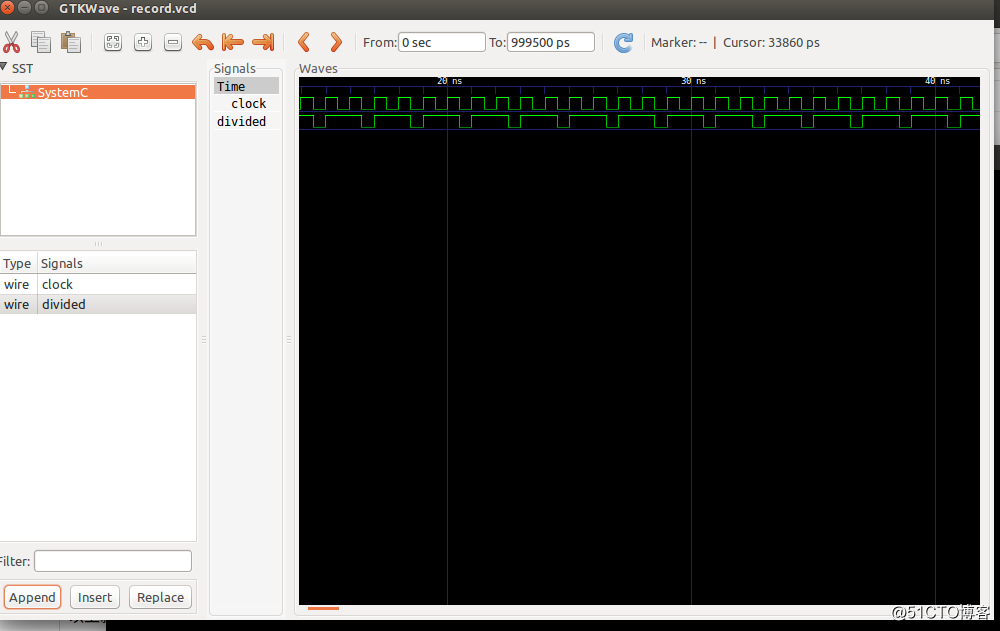

下面是gtkwave的显式图像:

参考文章:

https://blog.csdn.net/ywhfdl/article/details/7641288

以上是关于systemC构建时钟分频器的主要内容,如果未能解决你的问题,请参考以下文章