VHDL操作符

Posted lhkhhk

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了VHDL操作符相关的知识,希望对你有一定的参考价值。

1、逻辑运算符

(1)分类及功能

and(与),or(或),not(非),nand(与非),nor(或非),xor(异或),xnor(同或)。

(2)用法

a.操作数的数据类型必须符合操作符的要求

能进行逻辑运算的数据类型:bit、bit_vector、boolean,std_logic,std_logic_vector

b.表达式中有多个运算符时一般要加括号,但and、or、xnor、除外。

c.运算符两侧的操作数要对称

2、关系运算符

=(等于),/=(不等于),<(小于),>(大于),<=(小于等于,和信号的赋值符号相同),>=(大于等于)。

注:等于和不等于的操作对象可以是任何数据类型构成的操作数。

其他关系运算符对数据类型有一定的限制。(整数,枚举型)

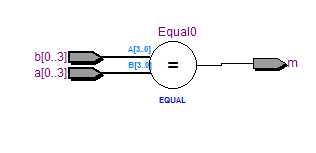

entity my1 is

port(a,b:in bit_vector(0 to 3);

m:out boolean

);

end my1;

architecture bhv of my1 is

begin

m<=(a=b);

end bhv;

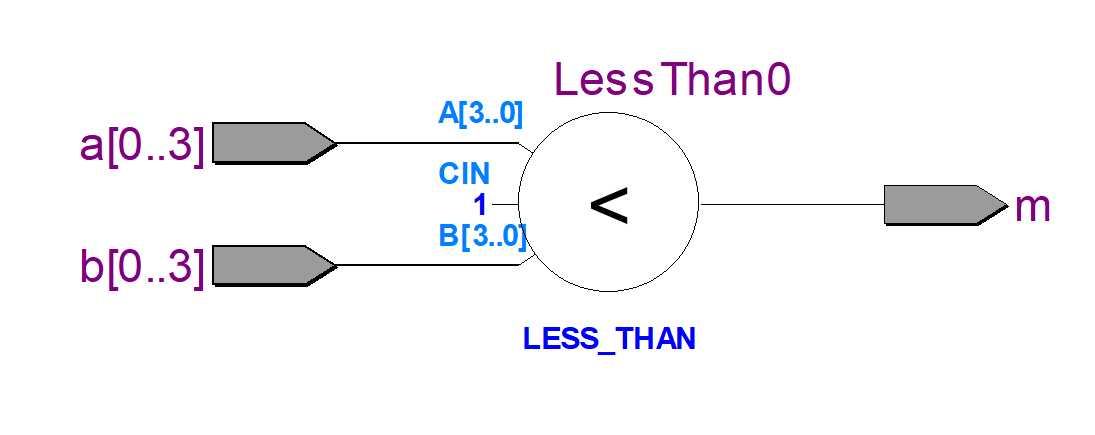

entity my1 is

port(a,b:in bit_vector(0 to 3);

m:out boolean

);

end my1;

architecture bhv of my1 is

begin

m<=(a<=b);

end bhv;

3、算术运算符

(1)分类及功能

求和运算符、求积运算符、符号运算符、混合运算符、移位运算符

(2)运用

a.求和运算符

VHDL中的求和运算符包括加减运算和并置运算,操作数的数据类型为整型。

例1:variable a,b,c,d,e,f:integer range 0 to 255;

a:=b+c; d:=e-f;

例2;signal a:std_logic_vector(4 to 0);

signal b:std_logic_vector(2 to 0);

signal c:std_logic_vector(1 to 0);

a<=b&c;

b.移位运算符

移位运算所对应的数据类型为一维数组,其中元素维bit、boolean。

variable a1:std_logic_vector(3 to 0);

a1 :="1011";

a1 SLL 1; a1=0110

a1 SLL 2; a1=1100

a1 ROL 1; a1=0111

以上是关于VHDL操作符的主要内容,如果未能解决你的问题,请参考以下文章

[从零开始学习FPGA编程-9]:快速入门篇 - 操作步骤2 - 硬件电路图形化描述与文本硬件描述语言Verilog HDL与VHDL语言以及比较