PCI Express

Posted _

tags:

篇首语:本文由小常识网(cha138.com)小编为大家整理,主要介绍了PCI Express相关的知识,希望对你有一定的参考价值。

PCI Express (Peripheral Component Interconnect Express), officially abbreviated as PCIe or PCI-e, is a high-speed serial computer expansion bus standard, designed to replace the older PCI, PCI-X and AGP bus standards. It is the common motherboard interface for personal computers\' graphics cards, hard disk drive host adapters, SSDs, Wi-Fi and Ethernet hardware connections. PCIe has numerous improvements over the older standards, including higher maximum system bus throughput, lower I/O pin count and smaller physical footprint, better performance scaling for bus devices, a more detailed error detection and reporting mechanism (Advanced Error Reporting, AER), and native hot-swap functionality. More recent revisions of the PCIe standard provide hardware support for I/O virtualization. It was created in 2003 by Intel, Dell, HP, and IBM.

In computer technology, transfers per second and its more common secondary terms gigatransfers per second (GT/s) and megatransfers per second are informal language that refer to the number of operations transferring data that occur in each second in some given data-transfer channel. It is also known as sample rate, i.e. the number of data samples captured per second, each sample normally occurring at the clock edge. The terms are neutral with respect to the method of physically accomplishing each such data-transfer operation; nevertheless, they are most commonly used in the context of transmission of digital data. 1 MT/s is 10⁶ or one million transfers per second; similarly, 1 GT/s means 10⁹, or equivalently in the US/short scale, one billion transfers per second. 在British English里,billion是万亿。

Speed of PCIE Version 6.0: 64 GT/s; x1: 7.88 GB/s; x16: 126 GB/s. x后面的1或16代表lane的个数,或者说位的个数。64/8=8, (64/8)*16=128, 刨去额外开销。5.0是32 GT/s, 4.0 16 GT/s, 3.x 8 GT/s. The PCI Express standard defines link widths of x1, x2, x4, x8, x12, x16 and x32.

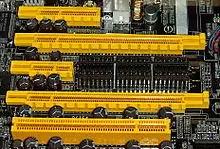

Various slots on a computer motherboard, from top to bottom: PCI Express x4; x16; x1; x16; PCI (32-bit):

Defined by its number of lanes, the PCI Express electrical interface is also used in a variety of other standards, most notably the laptop expansion card interface ExpressCard and computer storage interfaces SATA Express, U.2 (SFF-8639) and M.2.

Format specifications are maintained and developed by the PCI-SIG (PCI Special Interest Group), a group of more than 900 companies that also maintain the conventional PCI specifications. Website: pcisig.com

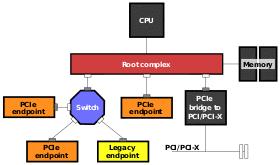

PCI Express is based on point-to-point topology, with separate serial links connecting every device to the root complex (host). a PCI Express bus link supports full-duplex communication between any two endpoints, with no inherent limitation on concurrent access across multiple endpoints. 听起来很像星形网络、交换机。网卡通过PCI Express与电脑相连。电子绕着原子转,月亮-地球,地球太阳。须弥藏芥子,芥子纳须弥。:-) PCI Express communication is encapsulated in packets. The work of packetizing and de-packetizing data and status-message traffic is handled by the transaction layer of the PCI Express port. [UDP...]

PCI Express devices communicate via a logical connection called an interconnect[8] or link. A link is a point-to-point communication channel between two PCI Express ports allowing both of them to send and receive ordinary PCI requests (configuration, I/O or memory read/write) and interrupts (INTx, MSI or MSI-X). At the physical level, a link is composed of one or more lanes.[8] Low-speed peripherals (such as an 802.11 Wi-Fi card) use a single-lane (x1) link, while a graphics adapter typically uses a much wider and therefore faster 16-lane (x16) link.

A lane is composed of two differential signaling pairs, with one pair for receiving data and the other for transmitting. Thus, each lane is composed of four wires or signal traces. Conceptually, each lane is used as a full-duplex byte stream, transporting data packets in eight-bit "byte" format simultaneously in both directions between endpoints of a link. Physical PCI Express links may contain from 1 to 16 lanes, more precisely 1, 4, 8 or 16 lanes. [x32仅理论上存在?] An eight-lane slot could be referred to as a "by 8" or as "8 lanes wide."

Timing skew results from separate electrical signals within a parallel interface traveling through conductors of different lengths, on potentially different printed circuit board (PCB) layers, and at possibly different signal velocities. Despite being transmitted simultaneously as a single word, signals on a parallel interface have different travel duration and arrive at their destinations at different times. 30万公里/秒 * 1ns = 0.3m, COBOL奶奶用这个演示光并不很快(量子纠缠无需时间)和纳秒很短。

A serial interface does not exhibit timing skew because there is only one differential signal in each direction within each lane, and there is no external clock signal since clocking information is embedded within the serial signal itself. PCI Express is one example of the general trend toward replacing parallel buses with serial interconnects; other examples include Serial ATA (SATA), USB, Serial Attached SCSI (SAS), FireWire (IEEE 1394), and RapidIO. In digital video, examples in common use are DVI, HDMI and DisplayPort.

The following table identifies the conductors on each side of the edge connector on a PCI Express card. The solder side of the printed circuit board (PCB) is the A side, and the component side is the B side. 表很长,不抄了,有82个pin,x1 cards end at pin 18; x4 cards end at pin 32; x8 cards end at pin 49. 这个pin是卡上的手指和主板上的插槽。芯片则有上千个pin.

Despite sharing the Mini PCI Express form factor, an mSATA slot is not necessarily electrically compatible with Mini PCI Express. Some notebooks (notably the Asus Eee PC, the Apple MacBook Air, and the Dell mini9 and mini10) use a variant of the PCI Express Mini Card as an SSD. This variant uses the reserved and several non-reserved pins to implement SATA and IDE interface passthrough, keeping only USB, ground lines, and sometimes the core PCIe x1 bus intact. This makes the "miniPCIe" flash and solid-state drives sold for netbooks largely incompatible with true PCI Express Mini implementations.

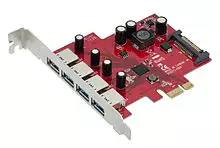

M.2 replaces the mSATA standard and Mini PCIe. Computer bus interfaces provided through the M.2 connector are PCI Express 3.0 (up to four lanes), Serial ATA 3.0, and USB 3.0 (a single logical port for each of the latter two). It is up to the manufacturer of the M.2 host or device to choose which interfaces to support, depending on the desired level of host support and device type. Two SSDs, left: mSATA (mini-SATA), right: M.2; A PCI Express 2.0 expansion card that provides USB 3.0 connectivity [没有USB 3.0的老电脑可以用右边的卡。我好像为只有USB 1.0接口的笔记本买过提供USB 2.0接口的PCMCIA卡,我折腾够了,copy许多文件时USB 2.0+散个步=能忍]. An open-end PCI Express x1 connector lets longer cards that use more lanes be plugged while operating at x1 speeds; A Marvell-based SATA 3.0 controller, as a PCI Express x1 card; An OCZ RevoDrive SSD, a full-height x4 PCI Express card

总之升级老电脑的方式是多样的。从SATA启动也足够快了。

The data link layer performs three vital services for the PCIe express link:

- sequence the transaction layer packets (TLPs) that are generated by the transaction layer,

- ensure reliable delivery of TLPs between two endpoints via an acknowledgement protocol (ACK and NAK signaling) that explicitly requires replay of unacknowledged/bad TLPs, 又像TCP了。negative acknowledgement message (NAK)

- initialize and manage flow control credits

OCuLink (standing for "optical-copper link", since Cu is the chemical symbol for Copper) is an extension for the "cable version of PCI Express", acting as a competitor to version 3 of the Thunderbolt interface. Version 1.0 of OCuLink, released in Oct 2015, supports up to PCIe 3.0 x4 lanes (8 GT/s, 3.9 GB/s) over copper cabling; a fiber optic version may appear in the future.

On 11 March 2019, Intel presented Compute Express Link (CXL), a new interconnect bus, based on the PCI Express 5.0 physical layer infrastructure. The initial promoters of the CXL specification included: Alibaba, Cisco, Dell EMC, Facebook, Google, HPE, Huawei, Intel and Microsoft.

Other communications standards based on high bandwidth serial architectures include InfiniBand, RapidIO, HyperTransport, Intel QuickPath Interconnect, and the Mobile Industry Processor Interface (MIPI). The differences are based on the trade-offs between flexibility and extensibility vs latency and overhead. For example, making the system hot-pluggable, as with Infiniband but not PCI Express, requires that software track network topology changes.

OCuLink (standing for "optical-copper link", since Cu is the chemical symbol for Copper) is an extension for the "cable version of PCI Express", acting as a competitor to version 3 of the Thunderbolt interface. Version 1.0 of OCuLink, released in Oct 2015, supports up to PCIe 3.0 x4 lanes (8 GT/s, 3.9 GB/s) over copper cabling; a fiber optic version may appear in the future.

以上是关于PCI Express的主要内容,如果未能解决你的问题,请参考以下文章